【導讀】本文描述一種基于自校準、自檢架構的低功耗16位SAR ADC。它帶有一個雙橋分離式CDAC和一個高速三級比較器。這種架構已經在生產中得到驗證,ENOB可達14.5位,而其成本遠低于目前市面上主流的12位SAR ADC。

對于之前使用分立ADC的應用,包括電能計量、手持式醫療設備、工業控制系統、電源管理系統、游戲機和儀器儀表等,低成本微控制器為其提供高性能模擬功能逐漸成為可能。在通用控制系統應用中,往往需要奈奎斯特ADC兼具低延遲、高帶寬和低功耗特性,與此同時,其精度達到約14位有效位數(14位ENOB),價格也為大眾所接受。在如此繁多的需求之下,目前的大多數SAR和Sigma-Delta (DS) ADC都將慘遭淘汰,因為在滿足頻率和延遲需求的同時還要實現低成本和低功耗目標太難。本文將介紹的是一款基于自校準、自檢架構的低功耗16位SAR ADC,其配有雙橋分離CDAC和高速三級比較器。生產數據表明,這種架構的精度高達14.5 ENOB,而且總成本(實現和測試)明顯低于市場上大多數暢銷的12位SAR ADC。

隨著SAR ADC分辨率的提高,CDAC單元的元件數量會呈線性增加,但這些元件的匹配要求會導致平方律區域增大。為了限制元件總數,通常使用橋接或縮放元件來將DAC拆分成更小的子DAC。這些縮放元件并非單位規格,其寄生效應可能會導致進一步的不匹配和錯誤。通常由于區域限制,匹配超過10~11位對于微控制器集成是不可行的。因此,必須對ADC DAC元件執行某種形式的校準才能滿足更高的分辨率和精度要求。本文將介紹一種差分、面積有效型16位自校準SAR ADC的設計。

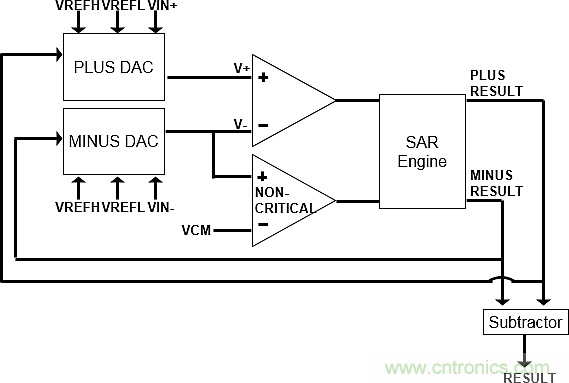

圖1:包含2個互補CDAC的全差分ADC架構。

ADC架構

圖1顯示了ADC架構,不包括通道多路復用器。SAR ADC通常由DAC和比較器構成反饋回路,并配有包括逐次逼近寄存器的邏輯。DAC通常由一組二進制加權元件組成,在本例中使用的是電容。一些應用中通常需要能夠對極性未知的差分輸入信號進行轉換。轉換差分信號也有助于通過共模噪聲抑制來提高結果的精度。

實現差分ADC常面臨諸多限制因素,其中一個是需要在逐次逼近期間將比較器的輸入保持在其共模范圍內。當比較器在共模電壓下自動調零后,如果輸入偏離該共模電壓,將導致轉換結果出現錯誤,進而增加非線性度。為了防止這一問題,我們添加了一個尺寸更小、功耗更低的“非關鍵”比較器。該比較器搭配負端DAC(負責采樣VIN-)實現部分逐次逼近。這樣可使比較器負輸入V-足夠接近VCM,從而確保比較器的精度在1LSB以內。負端所需的逼近次數由比較器的共模抑制比(CMRR)和ADC的分辨率決定。CMRR越高,所需的逼近次數越少。例如,如果12位ADC中比較器的CMRR為66dB,則只需在負端進行2次逼近(12位LSB的1/2 = 78dB,因此負端逼近需將|VCMV-|電壓減小12dB)。

我們實現的是16位ADC(1/2LSB = 102dB),比較器的CMRR大約為72dB,因此需要進行5次逼近(25 = 30dB)。對于5位SAR,“非關鍵”比較器必須解析的最小輸入電壓為VREFH/32。在負端完成部分逐次逼近之后,使用精密比較器和正端DAC(負責采樣VIN+)進行全16階逼近。兩個比較器輸出由SAR邏輯捕獲,以控制相應的DAC進行逐次逼近。正端結果與負端結果相減會得到未經校準的結果,從該結果中減去預設的校準值后即可得到最終轉換結果。該差分模式的運行速率最高可達320kS/s。在單端模式下,不需要在負端進行部分逐次逼近,因此最高運行速度可達460kS/s。此外,該ADC還具有低分辨率的12位模式,最高運行速率可達1MS/s。

CDAC陣列

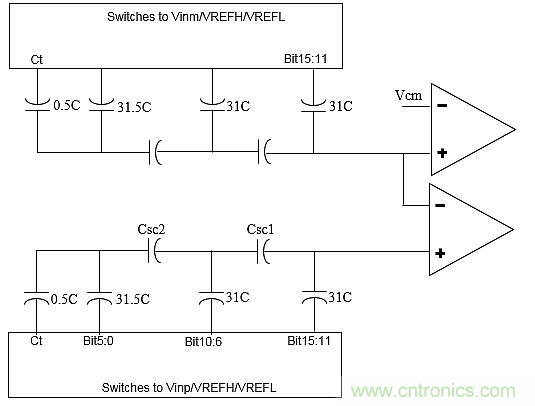

CDAC是SAR中最重要的組成部分。SAR ADC的線性度取決于電容陣列中的電容匹配。分離電容結構是限制芯片面積的常用方法。圖2所示的CDAC拓撲結構結合校準提供了一種可在電容陣列大小(96個電容)、速度、噪聲和線性度之間取得最佳權衡的設計。每個電容代表一組單位電容。通過對最高有效位電容進行校準,可以減小單位電容的尺寸。本設計使用了一個大約125fF的單位邊緣電容,可以向未校準的電容提供充分的匹配,并使16位的kT/C噪聲保持在1LSB以下。CDAC根據單位尺寸電容分為3個二進制加權的子DAC。最高有效位(MSB)子DAC包含5位,中間有效位(ISB)子DAC包含5位,最低有效位(LSB)子DAC包含6位。LSB部分由用于位0和終止的半尺寸電容構建成一個5位陣列。

圖2:包含2個橋接電容的全差分5b-5b-6b分離CDAC拓撲結構。

ADC校準

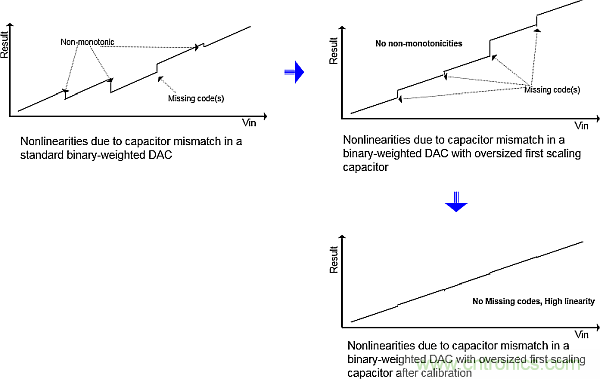

SAR ADC有許多種校準方法,一些方法使用基于數字關聯的校準,另一些方法使用相關技術測量DAC中的電容比例差,然后通過模擬調整方式來修改DAC元件或者通過數字調整方式來調整結果。本文中ADC使用的測量方法,是通過測量電容比例差來確定電容誤差值,然后通過數字調整方式來修改結果。正端和負端CDAC的MSB電容均被校準。為了在調整SAR結果后不產生較大的非線性度,校準前的CDAC必須是單調的,將縮放電容Csc1(圖3)的尺寸調整為略大于理想值可以保證單調性。圖3對這一概念進行了說明。

為了確定校準誤差值,每個MSB電容(由位15:11控制)都將與所有最低有效位電容的組合進行比較。例如,校準的某一步是將位11電容(1C)與位10:0電容和末位電容(由于Csc1過大而略大于1C)進行比較。下一步是將位12電容(2C)與位11:0電容和端接電容(略大于2C)進行比較。依此類推,每個MSB電容都會執行這一過程。校準系數會進行累加并存儲在存儲器中,每個ADC需要的存儲空間不到128位。完成正常ADC轉換之后,從未經校準的結果中減去對應于MSB結果的校準值可獲得校準結果。

然后,應用基于累積校準系數的增益因子可生成最終轉換結果。該校準方法可補償MSB電容之間的不匹配以及第一個縮放電容的不匹配和寄生效應。必須指出的是,為了提高未校準電容的線性度和耐受過程梯度、限制校準范圍,必須采用共質心版圖技術。此外,在電容陣列的邊緣采用了虛設的電容環,以確保電容陣列中的所有單位電容都具有相同的周邊結構。

圖3:非線性度以及提高CDAC線性度的方法。

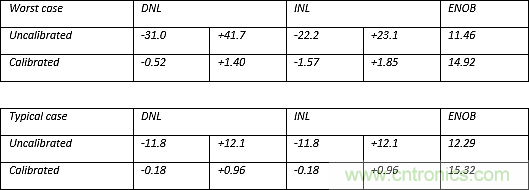

表1:典型情況和最差情況下CDAC INL和DNL的蒙特卡羅模擬結果。

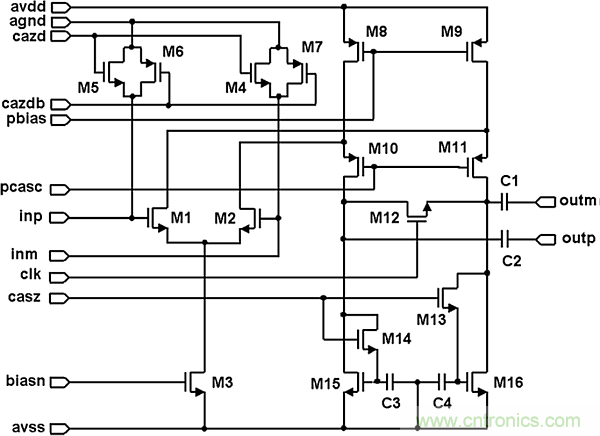

圖4:具有電容耦合和自動調零功能的全差分比較器。

在比較器設計中,需要權衡的主要是速度與精度。精度可通過提供足夠的高增益、低偏移和低輸入參考噪聲來保證。比較器偏移會引起ADC傳輸特性的偏移,但不影響ADC的線性度。在我們的實現方案中,偏移通過自動調零技術來消除。比較器需要足夠的增益來解決小于1LSB的電壓問題(在16位模式下,低至15mV左右),并在規定的延遲時間內提供響應。在16位模式下,最大ADC時鐘為12MHz,這種情況下比較器需要在大約半個周期(即41.6ns)內完成每次比較。

這里選用三級比較器來取得速度和增益之間的折衷。每一級均獨立自動調零,并與下一級電容耦合。注意,前兩級是全差分比較器,第三級是單端比較器。圖5給出了比較器各級的簡化原理圖。利用折疊共源共柵結構可提供足夠的增益,以解決16位ADC相關的電壓電平。在ADC采樣/自動調零階段,差分對M1-M2的柵極連接到模擬接地電壓(cazd為高電平),輸出級通過M13 - M14(casz為高電平)配置為低增益,以便存儲C3和C4上的偏移。

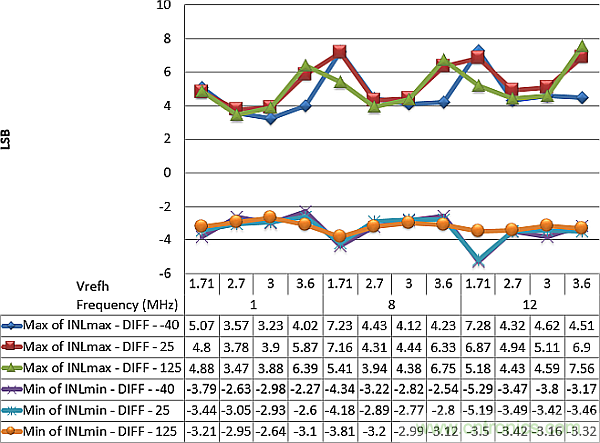

圖5:LSB中的最小/最大INL與參考電壓、溫度和采樣頻率之間的關系(在16位差分模式下的最大轉換速率時)。

在自動調零階段結束時,會將第一個casz解除置位,然后使用非交疊時鐘相位將cazd解除置位。ADC隨后會啟動逐次逼近階段,比較器級切換到高增益配置,輸入信號由折疊共源共柵增益級放大。在逐次逼近周期,比較器輸出級由M12復位,DAC可穩定下來(clk為高電平)。接下來,會將clk解除置位并進行比較操作。比較器布局對ADC的性能至關重要,特別要注意防止模擬和數字信號的耦合。

實驗結果

ADC采用90nm CMOS工藝制造,ADC電路已集成到90nm微控制器系列中,目前處于生產階段。在某一晶圓生產批次中隨機選取了4個器件,測得的ADC積分非線性(INL)誤差如圖5所示。圖中所示的最小和最大INL的測試條件如下:最大轉換速率,時鐘頻率從1MHz到12MHz(最大時鐘頻率),電壓從1.71V到3.6V,溫度從-40°C到125°C。

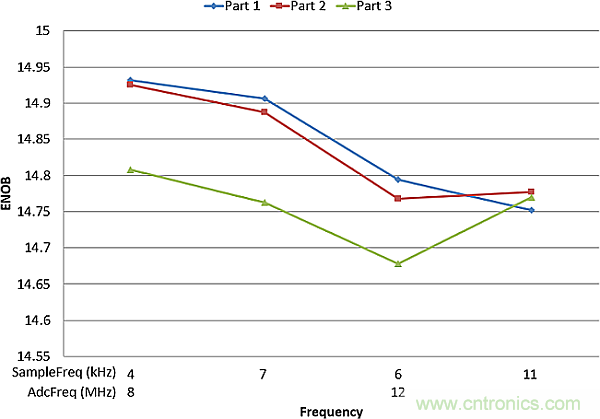

圖6顯示了在8MHz和12MHz時鐘速率下的ENOB,11kS/s轉換速率時可達到近15位的ENOB。

圖6:典型條件下SAR ADC ENOB與采樣頻率之間的關系。

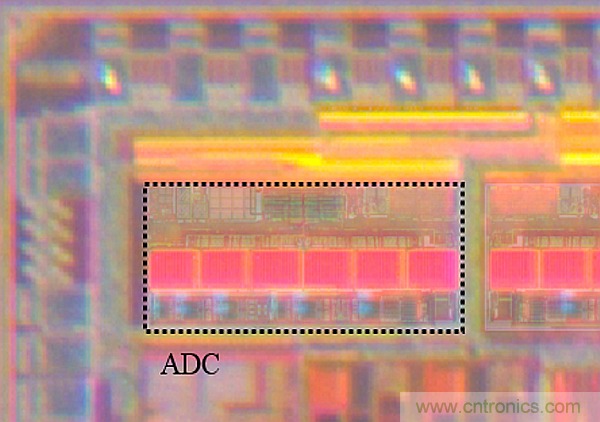

圖7是微控制器芯片上ADC的照片。CDAC位于中心部分,而開關位于每個邊緣電容單元的下面。比較器和電流參考位于CDAC下方,通道多路復用器位于CDAC上方,即電路的頂部。

圖7:微控制器芯片照片(突出顯示ADC)。

結論

借助90nm CMOS技術,現已成功使用金屬邊緣電容實現一款低功耗差分自校準460kS/s 16位軌到軌輸入SAR A/D轉換器。這款ADC在全速下測得的電流消耗為800mA,適于多種應用。硅測量顯示其總體性能達13.5-14.5 ENOB。該電路現已集成到90nm微控制器系列中,目前處于生產階段。

作者:Michael Berens,Jim Feddeler,Stefano Pietri和Brent Macha,恩智浦半導體

本文轉載自電子技術設計。