【導讀】今天的設計團隊如果采用傳統的RTL設計流程,將花費很多時間才能將運算密集型網絡帶入到硬件中,該領域亟需一個有別于以往RTL流程,同時又能有效提高生產力的方法。

今天的設計團隊如果采用傳統的RTL設計流程,將花費很多時間才能將運算密集型網絡帶入到硬件中,該領域亟需一個有別于以往RTL流程,同時又能有效提高生產力的方法。

CATAPULT HLS平臺的時代來臨

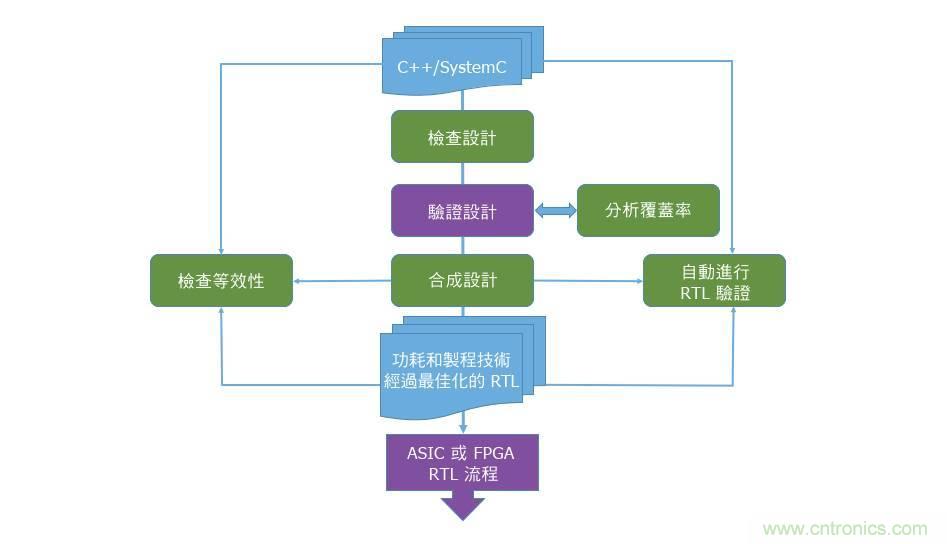

15年前,Mentor認識到設計和驗證團隊需要從RTL升級到HLS層級,并開發Catapult®HLS平臺。該平臺提供了從C + +到最佳化RTL的完整流程(圖1)。

圖1:Catapult HLS平臺

Catapult HLS平臺為算法設計師提供硬件設計解決方案,可以從C++/SystemC描述,生成高品質的RTL,并且以ASIC、FPGA或eFPGA為目標。此平臺能在合成之前檢查設計中的錯誤、為功能驗證和覆蓋率分析提供無縫且可重復使用的測試環境,同時支持在生成的RTL與原始HLS來源之間執行形式等效性檢查。

該解決方案的優勢包括:

支持后期階段變更。可隨時變更C++算法,重新生成RTL代碼或使用新制程。

支持硬件評價。可迅速地探索功耗、性能和面積選項,而無需變更原始代碼。

加快時程。將設計和驗證所花時間從一年縮短至幾個月,可在數日內增添新功能,使用的C/C++代碼行數比RTL減少5倍。

AI加速器生態系統

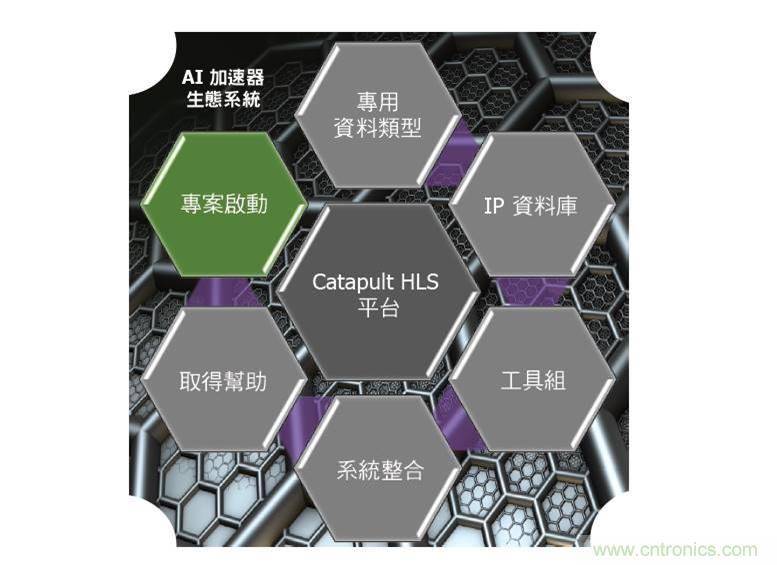

同時,Mentor在Catapult HLS平臺中部署了AI加速器生態系統(圖2),為AI設計師提供能快速展開項目的環境。

圖2:Catapult AI加速器生態系統

AC MATH數據庫

Algorithmic C Math(AC Math)中的所有函數都以C ++模板參數寫成,讓設計師可依據目標應用來指定數值的精準度。許多函數都使用不同的近似策略,例如,自然對數提供兩種形式,即分段線性近似和cordic形式。在可接受準確度稍有誤差的情況下,前者較小且較快; 后者雖然較慢,但準確許多。所有情況下都能自定義來源以達成設計目標。每個功能/內存塊都附有詳細的設計文件和C ++驗證程序。由于Catapult HLS平臺會利用C ++驗證程序,因此很容易根據來源設計來驗證RTL準確度。

該數據庫中的數學函數類別包括:

分段線性函數-絕對值、正規化、倒數、對數和指數(自然和底數2)、平方根、反平方根和正弦/余弦/正切(正和反)

激勵函數,如雙曲正切、S函數和Leaky ReLU函數

線性代數函數,如矩陣乘法和Cholesky分解

DSP數據庫

Algorithmic C DSP(AC DSP)數據庫定義了DSP設計師通常所需要的可合成C ++函數,例如濾波器和FFT。這些函數采用以C ++類別為主的設計,讓設計師能輕松示例物件的眾多變體,以打造復雜的DSP子系統。與AC Math數據庫一樣,輸入和輸出參數都會參數化,以便能在所需的定點精確度下執行算術,從而在為合成的硬件執行面積和性能折衷時,提供高度的彈性。

DSP數據庫包含:

濾波器函數,如FIR、1-D移動均值,以及多相位抽取

快速傅立葉變換(FFT)函數,如radix-22單一延遲回授、radix-2x動態就位和radix-2就位圖像處理數據庫Algorithmic C圖像處理數據庫(AC IPL)首先會定義一些常見的像素格式類型定義。

AI加速器生態系統還可提供豐富的工具組,由真實且經過測試的加速器參考設計示例,團隊可以研究、修改和復制這些示例,迅速展開項目。這些隨Catapult提供的套件,包含了可設定的C++/SystemC IP原始代碼、文件紀錄、驗證程序和指令碼,讓設計能進行HLS合成和驗證流程。這些工具組展示了各種能用來對性能(延遲)、幀率、面積或功率的折衷進行實驗的方法和編寫程序技術。

PIXEL-PIPE視訊處理工具組

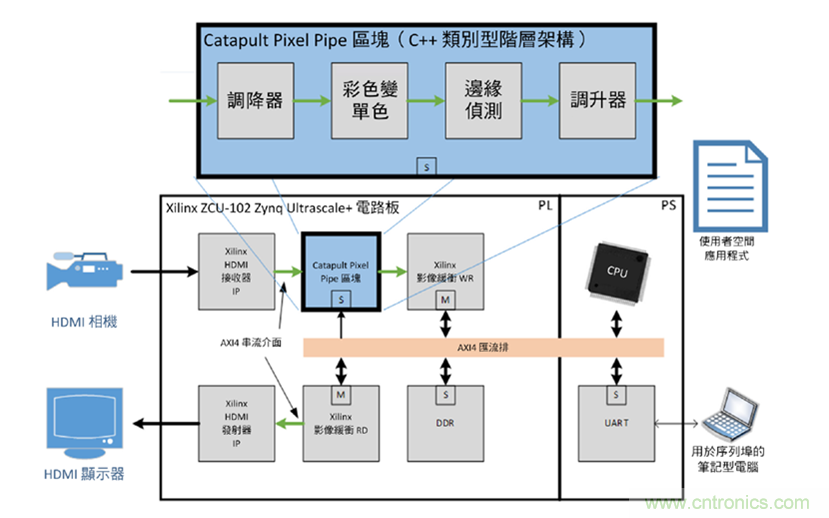

該視訊處理工具組展示了一個使用pixel-pipe加速器的即時圖像處理應用程序(圖3)。加速器內存塊使用C++類階層構架來實作。該內存塊將圖像縮小,并將圖像從彩色轉換為單色,以執行邊緣偵測,然后放大圖像。Xilinx®PetaLinux下的CPU上,執行了一個使用者空間應用程序,此程序能讓軟件控制開啟或關閉邊緣偵測內存塊。工具組文件紀錄會顯示如何使用Xilinx IP將該內存塊整合到Xilinx電路板中,以便團隊展示該系統。

圖3:Pixel-pipe視訊處理工具組

2-D折積工具組

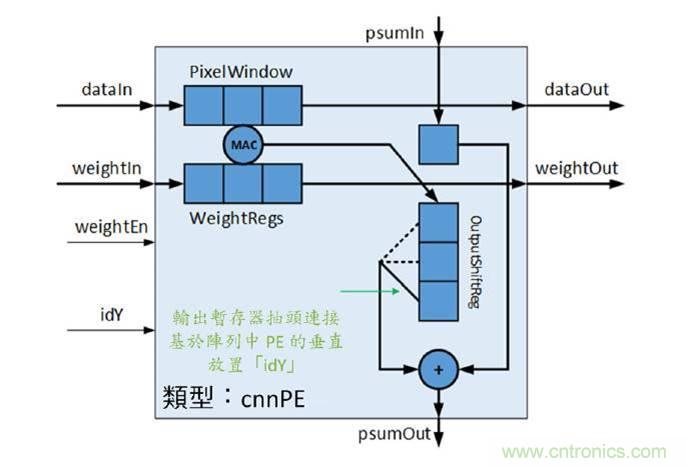

該工具組展示了如何以C++對Eyeriss1處理元件(PE)數組進行編碼,實作2-D折積以執行圖像的強化(銳化、模糊和邊緣偵測)。處理元件(圖4)可以執行3x1乘積累加(折積)。

圖4:Eyeriss處理元件

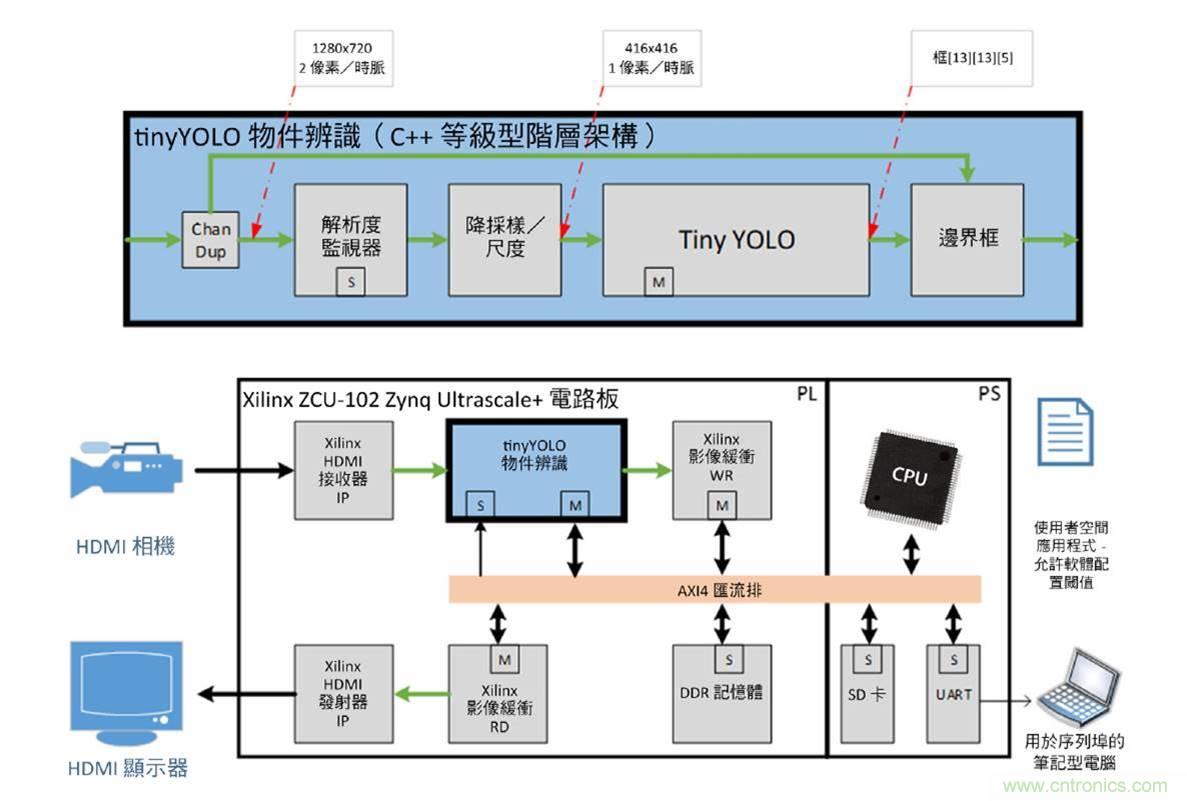

TINYYOLO物件辨識工具組

物件辨識工具組(圖5)展示了使用折積加速器引擎的物件辨識應用程序,該引擎使用2-D Eyeriss工具組中的PE數組實現。該工具組展示了如何透過AXI4互連(從系統內存來讀取核心權重數據)取得高速數據路由,并展示如何定義高效能內存構架。該工具組提供TensorFlow整合能力,可以C++語言的網絡層能進行推理測試。

圖5:TINYYOLO工具組示例-系統視圖

系統整合

加速器內存塊并非獨立存在,Catapult HLS提供“界面合成”能力,以將時間性協定加入至非時間性C++函數界面變數。設計師只需要在Catapult GUI中,為協定設定構架約束條件。此工具可支持典型的協定,例如AXI4視訊串流、請求/認可交握,以及內存界面。這讓設計師不必變更C++原始碼,就能探索界面協定。

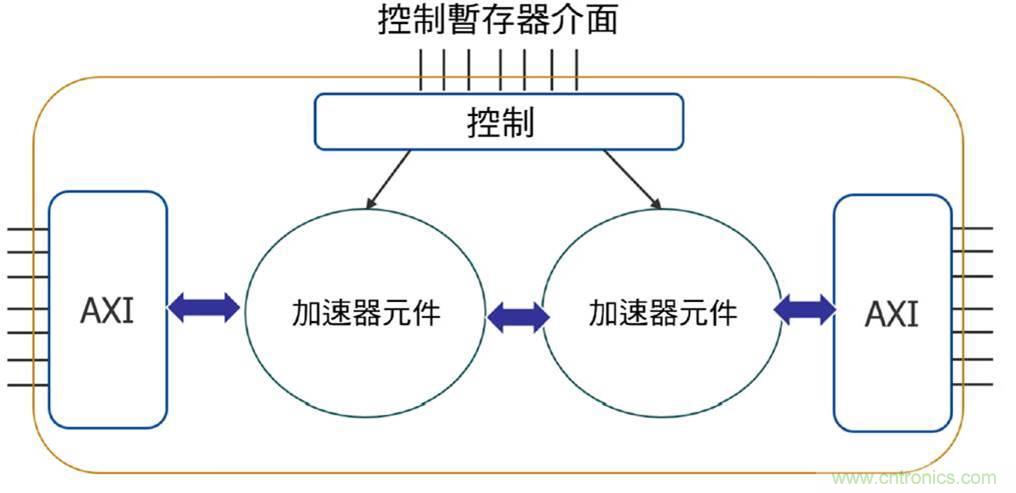

AXI示例

AXI示例(圖6)顯示了如何使用Catapult HLS產生的AXI界面IP,在AXI SoC子系統中示例一個或多個加速器元件。提供主控端、受控端和串流示例。

圖6:AXI示例

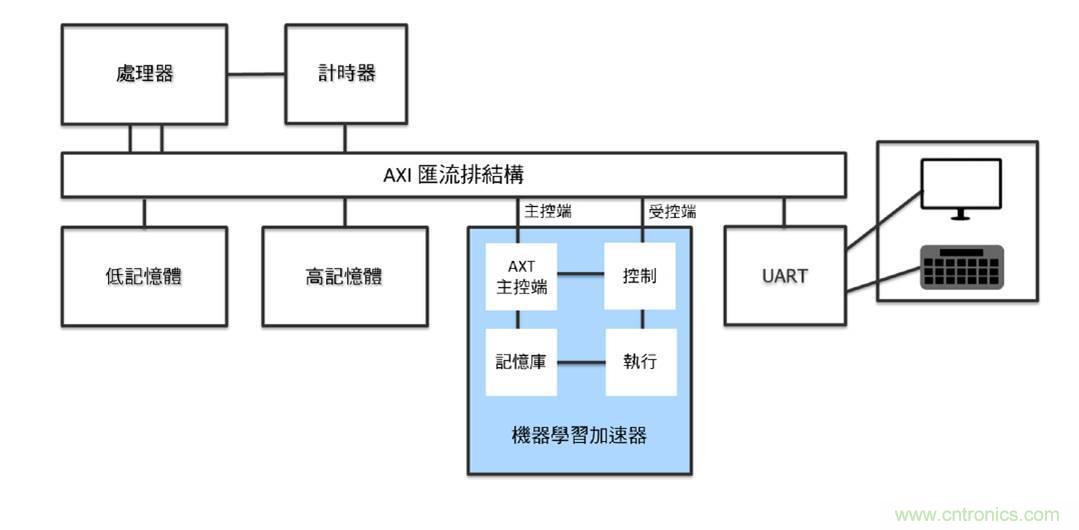

基礎處理器示例

基礎處理器示例(圖7)顯示了如何將機器學習加速器連接到完整的處理器型系統中,并采用了AXI示例。此示例中的機器學習加速器采用了簡單的乘積/累加構架,搭配2-D折積和區域取最大值。支持數個第三方處理器IP模型,并包含一個用于裸金屬編程的軟件流程(含有相關數據)。

圖7:基礎處理器平臺示例

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。