【導讀】隨著集成電路設計師將更復雜的功能嵌入更狹小的空間,異構集成包括器件的3D堆疊已成為混合與連接各種功能技術的一種更為實用且經濟的方式。

隨著集成電路設計師將更復雜的功能嵌入更狹小的空間,異構集成包括器件的3D堆疊已成為混合與連接各種功能技術的一種更為實用且經濟的方式。作為異構集成平臺之一,高密度扇出型晶圓級封裝技術正獲得越來越多的認可。此種封裝解決方案的主要優勢在于其封裝的基片更少,熱阻更低,電氣性能也更優秀。這是一個體現“超越摩爾定律”的例子,即使用 “摩爾定律”以外的技術也能實現更高的集成度和經濟效益。

異構集成技術

高密度扇出型封裝技術滿足了移動手機封裝的外形尺寸與性能要求,因此獲得了技術界的廣泛關注。構成此技術的關鍵元素包括重布線層(RDL)金屬與大型銅柱鍍層。重布線層連通了硅芯片上的高密度連接和印制電路板的低密度連接。通常需要使用多層重布線層,才能夠讓信號路由至電路板。

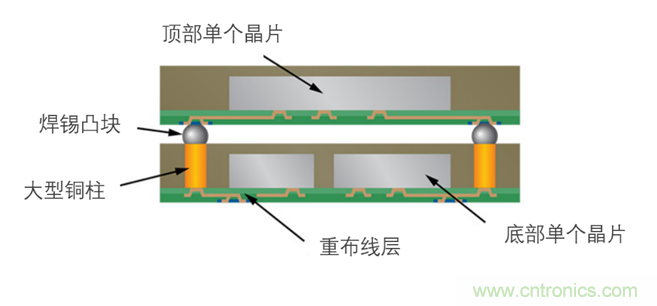

如圖1所示,大型銅柱是垂直連接不同層級的金屬支柱。頂部單個晶片的焊錫凸塊被放置于大型銅柱之上,并通過回流焊完成連接。

圖1. 2.5D封裝中的中介層結構

大型銅柱的工藝挑戰

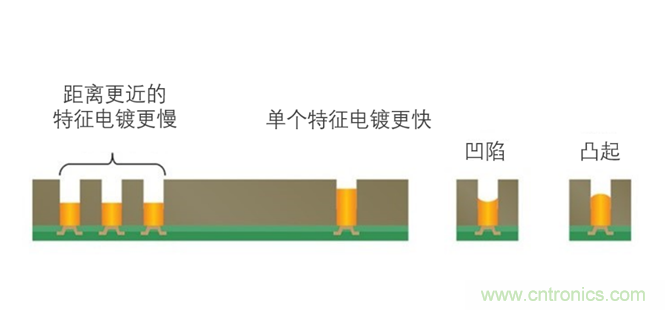

大型銅柱的區別在于其尺寸大小:它的高度和寬度是標準銅柱的5倍之多。構建大型銅柱的傳統方法是采用常規電鍍,這個過程漫長且緩慢。而最大的問題在于,此過程通常會產生不可接受的不一致結果。電鍍銅柱的高度會隨局部電流負載密度的不同而變化,并可能在支柱頂部產生一定程度的隆起或凹陷,而不是所需的平坦表面(圖2)。這種高度與特征形狀的不一致,可能會需要額外的后續平面化步驟(如CMP),并會導致連接不穩定,降低設備性能,增加總體工藝時間和成本。

影響以上電鍍結果的單個晶片布局差異包括特征形狀、寬度、深寬比以及周圍光阻的厚度和給定區域的特征密度。這些差異可能會演變成為晶圓、單個晶片或各個特征之間的差異。

解決這個問題的方法之一就是在目標厚度上電鍍多余的金屬,然后逆轉電鍍極化與電流方向。這將回蝕所添加金屬,以縮小銅柱的高度分布,或使大型銅柱的頂部更平整。但這種方法可能無法有效提升不同長度銅柱尺寸的一致性,而且通常會導致不良變形,使得大型銅柱的表面粗糙凹陷,邊緣腐蝕。

圖2. 電鍍大型銅柱的常見差異包括電流負載問題、凹陷和凸起。

泛林集團的解決方案

泛林集團通過其獨有的Durendal®工藝解決這一問題。該工藝可以產出優質、光滑的大型銅柱頂部表面,整個晶圓上的大型銅柱高度也非常均勻。整套Durendal®工藝可以在SABRE® 3D設備上實施完成。

圖3. 通過SABRE® 3D使用Durendal®工藝,產出尺寸均勻、高質量的大型銅柱。下方的圖片比較了晶圓邊緣(左側)與晶圓中心(右側)大型銅柱的高度差異。

Durendal®工藝提供了一種經濟高效的方式進行單個晶片堆疊,并能產出高良率以及穩固可靠的連接。在未來,我們期待Durendal®工藝能促進扇出型晶圓級封裝在單個晶片堆疊中得到更廣泛的應用。

(來源:作者:泛林集團)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。