【導讀】本文給出了一種1 ~ 3 GHz 頻段的寬帶低噪聲放大器的設計,電路采用電阻負反饋結構,采用SMIC 0.18 μm RF CMOS 工藝對寬帶低噪聲放大器進行了優化分析和仿真,結果表明在寬帶匹配、通道增益及噪聲系數方面都取得了較好的性能,對于寬帶低噪聲放大器的設計具有一定的參考價值。

隨著衛星通信、調頻技術等相關技術的發展,對射頻前端特別是低噪聲放大器的工作頻帶提出了更高的要求,傳統的窄帶低噪聲放大器越來越受到限制。低噪聲放大器位于射頻的最前端,根據通道噪聲系數的理論,低噪聲放大器的增益和噪聲系數對整個射頻通道的噪聲系數起著及其重要的作用。基于CMOS 工藝的低噪聲放大器經過多年的發展,其噪聲系數及增益都已經達到了很高的水平,但是其大多需要采用無源電感器件來實現。眾所周知,基于CMOS 工藝的電感不僅占用較大的芯片面積,而且其品質因數性能也通常不會超過10。同時在一些大規模應用的場合,在管芯的鍵合、封裝時由于鍵合線的長度不可控、寄生電容不同等原因,傳統的片外匹配電路通常會發生較大的變化,電路性能受到較大的影響。

本文設計一種集成度高、匹配方便的寬帶低噪聲放大器,而基于寬帶匹配的pH 甚至fH 級的電感在現有的集成電路制造及鍵合水平下將是很嚴重的瓶頸問題。而且運用較多的電感、電容也是其目前不能大規模應用的重要原因,所以研究基于CMOS工藝的無電感型寬帶低噪聲放大器具有重 要的學術價值和應用價值。

1 結構分析

低噪聲放大器是無線接收系統中第一個模塊,影響著整個系統的噪聲性能和靈敏度等參數。隨著超寬帶技術的發展,寬帶低噪聲放大器設計已成為當前設計的一個熱點。根據目前國內外發表的相關文獻,當前寬帶低噪聲放大器的結構大致有帶通濾波網絡匹配和電阻負反饋2 種結構。

帶通濾波網絡匹配結構主要是基于傳統的源級負反饋結構的低噪聲放大器,在輸入端口處采用帶通濾波器來實現寬帶乃至超寬帶匹配來實現輸入S 參數的匹配。在低噪聲放大器電路設計時,此結構是窄帶低噪聲放大器設計中提供阻抗和噪聲同時匹配的經典技術。因此,要在寬帶內獲得良好的輸入匹配及平坦的增益,就必須在輸入端加入較高階數的LC帶通濾波器以展寬低噪聲放大器的工作頻帶。由于該匹配網絡為同頻帶的帶通濾波器,通常需要2 階乃至3 階的帶通濾波器,這就意味著需要在芯片內部需要多個電感,這就會導致 芯片面積較大。同時,為了達到輸入匹配,該結構引入了源級負反饋電感,電感值通常較少,封裝參數將會對源級負反饋電感造成很大的影響。該源級負反饋電感一般取值較小,在片實現時很難保證精度,從而影響輸入端的匹配。

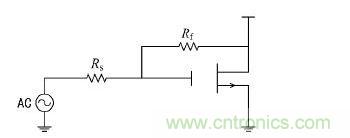

電阻負反饋型低噪聲放大器由于其占用面積小、噪聲系數低以及良好的線性度性能等特點,在無電感型寬帶低噪聲放大器的設計中存在較大的優勢。電阻負反饋型低噪聲放大器可以提供良好的寬帶匹配和平坦的增益。但是其負反饋會導致噪聲性能的惡化和最大可用增益的降低,電阻負反饋型低噪聲放大器原理圖如圖1 所示。

圖1 電阻負反饋型低噪聲放大器原理

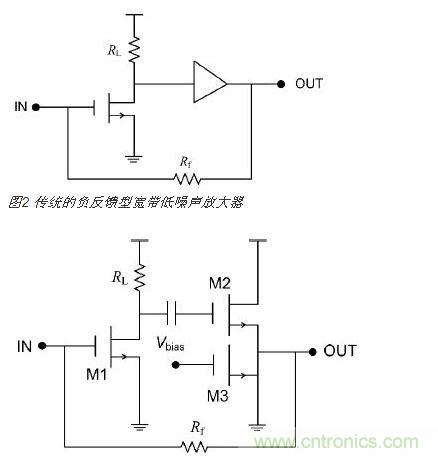

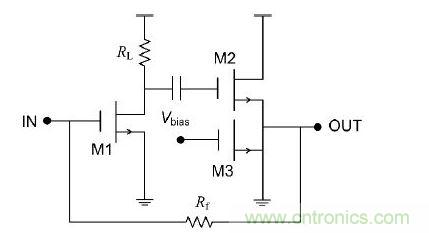

在電阻負反饋型低噪聲放大器中,輸入阻抗由反饋電阻和反饋放大器的閉環增益的比值決定。反饋電阻Rf的值通常遠大于源阻抗Rs。因此,為了匹配低的源噪聲電阻( 典型值為50 Ω) ,反饋電阻一般在幾百歐姆的量級,這一點也加重了噪聲指數的升高。在電阻負反饋的低噪聲放大器中,反饋電阻直接與輸出相連,需要在噪聲系數與輸入阻抗匹配直接做出一些折中,通常在反饋電阻與輸出端口之間增加緩沖電路來減少它們之間的影響,其電路原理如圖2 和圖3 所示。

圖3 改進的負反饋型寬帶低噪聲放大器

M2、M3 共同組成源跟隨電路,起著隔離輸入輸出端口,減小反饋電阻與輸出電路的作用,同時該源跟隨器還起著增大輸出驅動能力的作用,其輸出電阻為1 /gm2。合理地調節M2 的寬長比及偏置電流,可以使其輸出阻抗匹配至50 Ω。

[page]

2 電路設計

本文設計的低噪聲放大器的完整電路結構如圖3所示。該電路為單端結構,共有2 級。其中,M1、RL構成了第1 級的放大電路; M2、M3 為源級跟隨器,為寬帶低噪聲放大器的第2 級,2級電路之間通過電容進行耦合,Vbias為第2 級電路的偏置電壓,Rf為反饋電阻,主要起著調整輸入電阻作用,同時它和M1 也在很大程度上影響著噪聲系數,因此,在電路設計中需要對其阻值進行折中。合理調整反饋電阻Rf及M1 管的寬長比,便可實現良好的輸入匹配。M1 柵極的噪聲經過主放大電路進行放大,在M1 的漏端的噪聲電壓與器相位相反,該噪聲電壓經過源級跟隨電路后相位與之前相同,即與M1 的柵極噪聲電壓極性相反,經過反饋電阻后在M1 的柵極處形成噪聲抵消,合理調節共源放大電路與源級跟隨電路的增益可以使得主放大電路M1 管的溝道熱噪聲完全抵消。

圖3 改進的負反饋型寬帶低噪聲放大器

該結構的設計要點如下:

① 在工作頻段范圍內實現1 ~ 3 GHz 寬帶匹配,使其S11<-15 dB;

② 帶內增益>14 dB;

③ M1 的溝道熱噪聲被反饋電路降低,在寬頻帶范圍內實現噪聲系數NF<3. 6 dB。通過分析小信號模型和噪聲系數,得到該結構的輸入阻抗為:

式中,Qsp的值為3. 5 ~ 5. 5,在該范圍內噪聲的影響很小,Qsp取最佳值4. 5 時,噪聲可表示為:

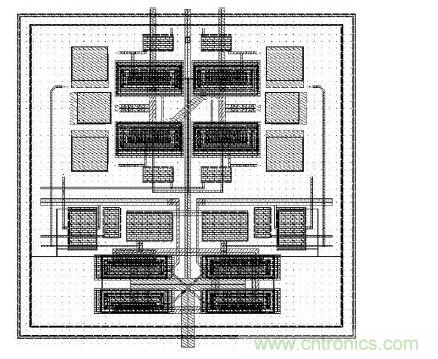

當上面2 個條件同時滿足時,低噪聲放大器絕對穩定; 如果這2 個條件不能同時滿足,低噪聲放大器會存在潛在的不穩定和振蕩,本文所設計的寬帶低噪聲放大器的版圖如圖4 所示。

圖4 寬帶低噪聲放大器的整體版

[page]

3 仿真結果分析

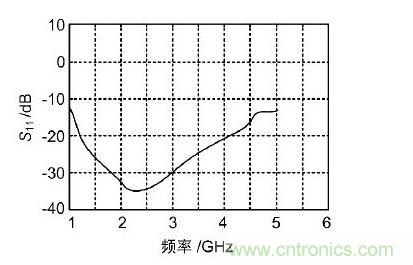

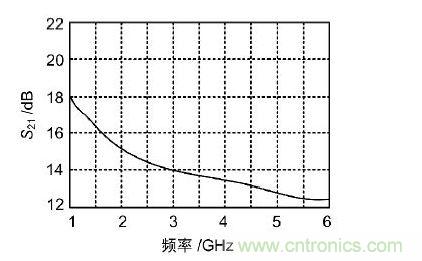

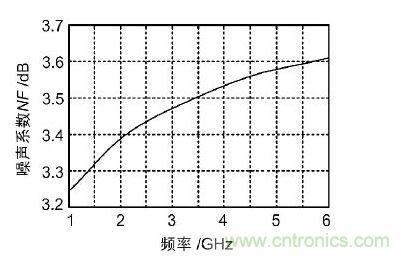

在對電阻負反饋型寬帶低噪聲放大器電路分析與設計的基礎上,基于SMIC 0. 18 μm RFCMOS 工藝進行設計,在Cadence Virtuoso 平臺上對電路原理圖進行設計,并對噪聲系數、S11、S21等參數進行了優化設計,仿真優化后得到的LNA 的S 參數、噪聲系數的仿真結果如圖5、圖6 和圖7 所示,電阻反饋型低噪聲放大器在工作頻帶范圍內提供了較平坦的高增益,在1 ~ 3 GHz 的頻帶,相應的仿真結果為: S11 <-15 dB,增益>14 dB,并在在整個頻帶范圍內的平坦度較好,增益波動<2. 6 dB,噪聲系數<3. 6 dB。

圖5 寬帶匹配的S11參數

圖6 寬帶低噪聲放大器的帶內增益

圖7 寬帶低噪聲放大器的噪聲系數

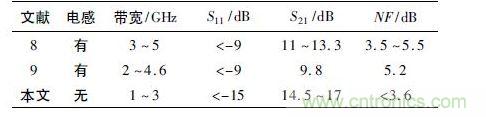

本文設計的寬帶低噪聲放大器與已經發表文獻中的寬帶低噪聲放大器的性能比較如表1 所示,這些文獻均采用0. 18 μm 工藝進行設計,具有一定的比較意義。通過表1 可以看出,本設計中各項參數都達到了較好的性能指標,避免了傳統集成電路設計中需要采用電感的缺點,而電感通常在電路設計中占用非常大的面積,本文設計的寬帶低噪聲放大器省略了傳統低噪聲放大器設計中的電感,這將在很大程度上減少芯片的面積; 更為重要的是該芯片依靠自身的MOS 管和比例電阻實現了內匹配,避免了大批量應用時由于芯片內部參數受工藝參數影響而造成的外圍匹配電路的更改,簡化了芯片的應用,在實際的工程應用中具有重要的意義。