【導讀】之前,我們在博客系列《快速開關和顛覆性的仿真生態系統》的第1部分介紹了安森美半導體獨一無二的寬禁帶生態系統及我們的物理可擴展模型。在這第2部分,我們將介紹我們的碳化硅功率MOSFET模型。

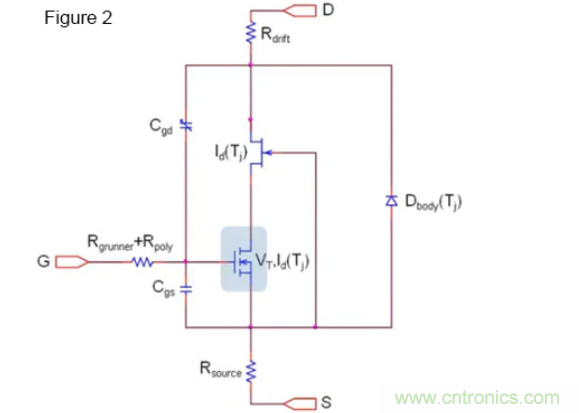

現在介紹該模型的幾個元素,如下所示。首先,我們討論關鍵通道區域。這里我們使用著名的伯克利BSIM 3v3模型。只要有可能,我們就盡力不做重復工作。在本例中,我們嘗試建模一個適合BSIM模型的MOSFET通道。該模型以物理為基礎,通過亞閾值、弱反和強反準確地捕捉轉換過程。此外,它具有很好的速度和收斂性,廣泛適用于多個仿真平臺。

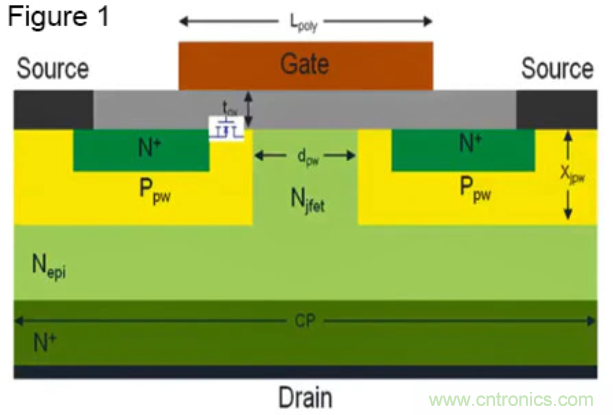

圖1顯示典型的碳化硅MOSFET器件的橫截面。圖2展示我們精簡版本的子電路模型。

接下來,我們需要包含由EPI區域的多晶硅重疊形成的門極到漏極的臨界電容CGD。該電容器基本上是高度非線性金屬氧化物半導體(MOS)電容器。該電容的耗盡區域依賴于復雜的工藝參數,包括摻雜分布、p阱dpw之間的距離和外延層的厚度。基于物理的模型考慮到所有這些影響,采用SPICE不可知論的行為方法實現。稍后,我們將談談什么是SPICE不可知論方法。

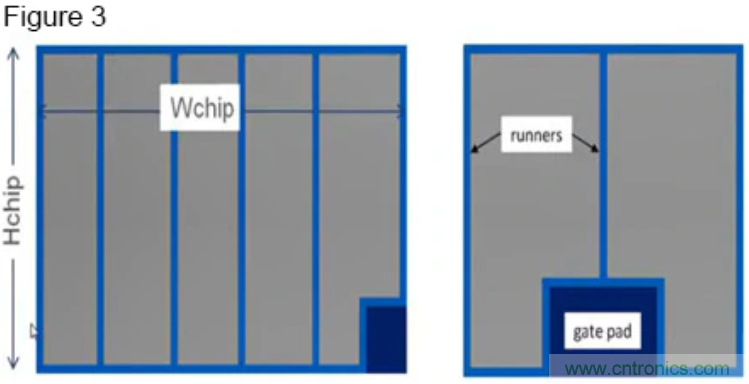

從橫截面開始,我們將介紹芯片布局可擴展性的一些概念和構造,如圖3所示,灰色區域是有源區。藍色無源區與裸芯邊緣、門極焊盤(gate pad)和門極流道(gate runners)相關聯。基于物理幾何的導子決定了無源區和有源區之間的分布,這是實現可擴展性所必需的。我們非常關注在有源和無源區邊界區域形成的寄生電容。一旦您開始忽略布局中的寄生電容,什么時候停止?所有可忽略的電容最終加起來就成了一個問題。在這種情況下無法實現擴展。我們的理念是使寄生電容為0。

碳化硅MOSFET支持非常快的dV/dts,約每納秒50 V至100 V,而dI/dts則支持每納秒3 A至6 A。本征器件門極電阻很重要,可用來抗電磁干擾(EMI)。在圖3中右邊的設計有較少的門極流道,因此RG較高;很好地限制振鈴。圖3左邊的設計有許多門極流道,因此RG較低。左邊的設計適用于快速開關,但每個區域有更高的RDSon,因為門極流道吞噬了有源區。

我們在該系列博客的下一篇將談談碳化硅功率MOSFET模型驗證,請繼續關注。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀: