【導讀】從2003年至今,電纜服務寬帶數據訂閱用戶數量的復合年增長率接近14%,并且增長趨勢沒有放緩,而要想在消費者數據需求增長的環境下保持領先地位,電纜服務提供商需要升級其分配系統。本文介紹的電纜系統下游發射機設計也許是個不錯的參考。

過去十年間,電纜系統中使用的寬帶數據數量增長迅猛。從2003年起,電纜服務寬帶數據訂閱用戶數量的復合年增長率接近14%。近年來,數據使用增長的趨勢沒有出現放緩的跡象,因為越來越多的消費者使用基于網絡的服務來實現視頻流、音頻流和游戲應用。

電纜服務提供商正在升級其分配系統,從而在消費者數據需求增長的環境下保持領先地位。傳輸系統的本質是從多址傳送系統發展成多址傳送和窄播相結合的系統,前者向所有的訂閱者都發送相同的信號,后者中有些內容由所有訂閱者共享,有些內容直接發送至特定的訂閱者。

電纜系統下游發射機

數字電纜發射機已從傳統發射機發展到直接調制技術,傳統發射機中的一對基帶DAC用來驅動正交調制器,正交調制器的本振用來選擇正確的RF頻率。

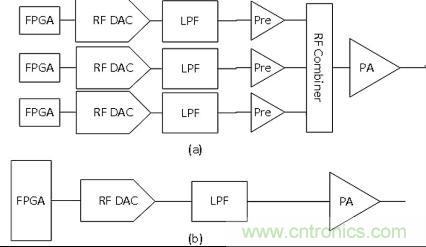

在直接調制發射機中使用了一個RF DAC,電纜通道全部創建在數字域中,通常為FPGA。數字信號從FPGA發送至RF DAC,將其轉換成模擬信號然后發送至功率放大器。典型電纜發射機的簡化框圖如圖1所示。

圖1(a):使用多個RF DAC和一個RF合成器實現完整電纜頻譜的典型電纜發射機框圖

(b):使用新型AD9129 RF DAC的新型電纜發射機框圖

(b):使用新型AD9129 RF DAC的新型電纜發射機框圖

在圖1(a)中,發射機由幾個RF DAC組成,這些RF DAC由幾個FPGA驅動,然后每個RF DAC的輸出發送至前置放大器。前置放大器的輸出組合后反饋至驅動電纜設備的單個功率放大器。使用該架構的原因是,以合理功耗來綜合大量數字信號的FPGA的柵極數量和容量是有限的,而且每個RF鏈都可以針對特定頻帶進行優化。

RF DAC通常具有信號處理功能,可以限制可能產生的總RF帶寬,但可以減少FPGA的接口要求。上一代RF DAC具有良好的性能,但諧波性能不能滿足嚴格的DOCSIS規格,因此需要進行細致的頻率規劃和RF濾波器設計才能達到可接受的性能。

其架構可能采用每個RF DAC 2、4或8個256-QAM通道,雖然需要耗費額外的硬件成本,但可以提供可擴展性。該架構存在若干不足之處。隨著所需通道數量的增加,RF合成器變得更加復雜,隨著每個DAC通道的增加,合成器的損耗也會增加。

每個FPGA+RF DAC+前置放大器鏈的功耗很大,可能達到每通道10 W。所需的多個RF鏈可能需要多卡來實現158通道的完整電纜頻譜,每張卡的功耗為1 kW或更高。在一個設備中安放多張卡是為1000戶的群組提供服務所必需的。

系統變得很大,需要多張卡才能為每個1000戶的群組提供服務。因此需要大型設施或建筑將所有的卡安放在大型機架或機殼中,必須特別注意機架冷卻系統,將建筑保持在適當的工作溫度所需的費用也很高。

如今,由于柵極數量的增加和細線CMOS工藝的出現,FPGA可以實現足夠高的密度,從而在FPGA(驅動一個RFDAC)上創建整個1586MHz寬電纜通道。結合ADI公司的新型AD9129 RFDAC后,可以設計出更加簡化的電纜發射機。

圖1(b)顯示的是新型發射機的框圖,這種發射機能夠合成50MHz~1GHz的整個下游電纜頻譜。FPGA中的數字調制器以2.8GSPS的高采樣速率驅動AD9129 RFDAC。

DAC具有一個可選2倍插值器濾波器,可以用來實現帶外元件的片上數字濾波,可將有效采樣速率提高到5.6GSPS。DAC輸出采用低通濾波器進行濾波,并從Triquint TAT2814發送至新的高度集成的可變增益放大器和驅動放大器。

放大器將前置放大器、可變衰減器和驅動器放大器集成在一個模塊中,實現了新的集成水平。這使得無線電部分的布局變得緊湊,并減小了每個無線電端口的物理尺寸。

[page]

設計示例

1、RF DAC

AD9129 RFDAC的采樣速率高達2.8GSPS。這種高采樣速率的優點在于,DAC鏡像折疊比之前的解決方案高fDAC/2。這可以防止鏡像在600MHz下折疊,從而降低其抑制要求。數據通過時鐘頻率為700MHz的雙LVDS端口傳輸至DAC,數據輸入至時鐘的兩個邊沿,每個端口上的數據傳輸速率為1.4GHz。

DAC的電流驅動架構和細致設計可以實現出色的雜散性能和噪底。DAC采用0.18μm工藝,使得功耗降至約1.1W。

2、低通濾波器

在DAC和放大器之間,無源信號調理有助于滿足DOCSIS規格,實現所需的帶外抑制比和功率波動。設計示例中選用了七階橢圓濾波器來解決帶外抑制問題。AD9129DAC的2.305 GSPS低采樣速率用來評估低通濾波器帶外性能,因為鏡像在低采樣速率時折疊在離電纜帶更近的位置。

1GHz通道的鏡像需要特別注意,因為它落在1.3GHz的位置,離所需信號僅300 MHz。該設計針對1.3GHz鏡像達到了62.5dBc的鏡像抑制,符合DOCSIS規格對于帶外抑制比要求。兩個串聯諧振均衡器用來解決電纜帶上由于DAC輸出上的sinc滾降和功率放大器中的額外滾降造成的功率波動問題。均衡器在電纜帶中的最高功率通道和最低功率通道之間達到的功率波動約1.4dB,滿足DOCSIS規格,無需任何輸入信號的數字操控。每個獨立通道的功率都可以進行數字調整,以便在電纜帶上實現更加精細的調諧平坦度。

3、輸出放大器

TAT2814輸出放大器將三項功能合并在一個封裝內,大大降低了電路板空間,具有高集成度。這款放大器可能達到的總增益約30dB。輸出能夠為1通道256-QAM信號提供高達+65dBmV的功率。放大器在GaAs工藝中實現,并針對低功耗進行了優化。該集成器件的總功耗約4.2W。

4、非線性校正

非線性校正(NLC)用來改進整個信號鏈的帶內諧波性能,校正來自DAC和功率放大器的失真,以及可能沿信號鏈產生的其他失真。NLC過程可以進行編程設置,以使電路板滿足規格要求,或留出指定的裕量,以允許制造容差。NLC校準僅需幾分鐘,可大大改進系統性能。

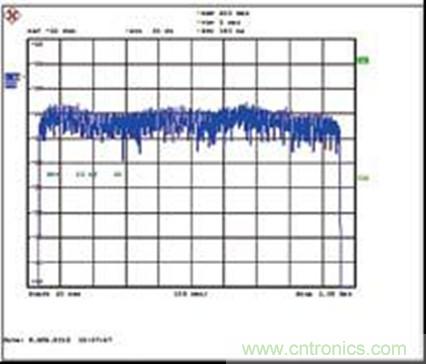

圖2:設計示例輸出端158DOCSIS256-QAM通道的整個電纜帶

5、測量結果

我們用AD9129設計了一塊優化布局的電路板,并測量了其性能。具有所有158個通道的信號用來測試電纜帶上的電路板響應平坦度。圖2所示為以整個頻帶信號作為輸入的優化電路板輸出。最高和最低功率通道之間的功率波動僅約1.4dB,在DOCSIS規格內,且能夠通過數字操作輸入信號進一步改進。

測試顯示,電路板可以用4dB裕量來可靠校正,使系統在制造容差內保持穩定。

相關閱讀:

RF電路板分區設計中PCB布局布線技巧

http://hdh-sz.com/emc-art/80009703

RFID技術原理及其射頻天線設計

http://hdh-sz.com/rf-art/80005888

射頻電纜性能指標及設計準則

http://hdh-sz.com/rf-art/80012962