【導讀】在芯片設計階段,對任何的代碼或版圖的改動都是非常容易的,在芯片設計階段植入后門已屢見不鮮、廣為人知,但是,在制造生產階段,同樣也可能被有意植入后門,而這一點則往往被人們所忽略。

一顆高性能芯片在區區數百平方毫米的硅片上蝕刻數十億晶體管,晶體管間的間隔只有幾十納米,需要經過幾百道不同工藝加工,而且全部都是基于精細化操作,制作上凝聚了全人類的智慧,是當今世界上最先進的工藝、生產技術、尖端機械的集中體現。

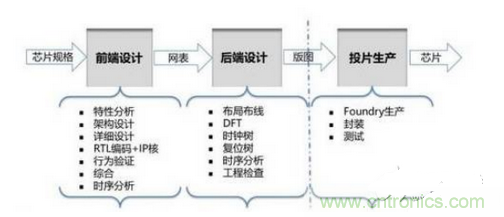

我們知道,芯片的設計制造要經過一個非常復雜的過程,可大體分為三個階段:前端設計(邏輯代碼設計)、后端設計(布線過程)、投片生產(制芯、測試與封裝)。如圖所示:

從圖中可以看出,前端設計包括需求分析、邏輯設計與綜合,輸出門級網表;后端設計對原有的邏輯、時鐘、測試等進行優化,輸出最終版圖;投片生產是在特定電路布線方式與芯片工藝條件下將電路邏輯“畫”到硅片上的過程。

一顆高性能芯片在區區數百平方毫米的硅片上蝕刻數十億晶體管,晶體管間的間隔只有幾十納米,需要經過幾百道不同工藝加工,而且全部都是基于精細化操作,制作上凝聚了全人類的智慧,是當今世界上最先進的工藝、生產技術、尖端機械的集中體現。在如此復雜和細微的芯片內部,除了完成所宣稱的功能之外,在額外的電路中構建一個后門,使得可以接受外部控制,一般的驗證檢測手段通常不能找出任何問題,一般用戶也很難察覺芯片上后門的操作行為。

在芯片設計階段,對任何的代碼或版圖的改動都是非常容易的,在芯片設計階段植入后門已屢見不鮮、廣為人知,但是,在制造生產階段,同樣也可能被有意植入后門,而這一點則往往被人們所忽略。

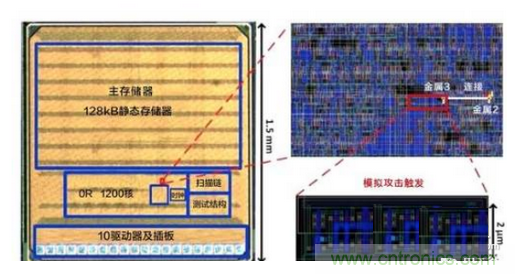

據報道,2016年6月,在DARPA和國家科學基金會支持下,美國密歇根大學首次在開源OR 1200處理器制造中植入模擬惡意電路(即硬件木馬),可進行遠程控制和實施攻擊。如下圖所示,該硬件木馬比傳統數字電路構成的硬件木馬小2個數量級,結構小巧,難以檢測,易于實現,危害極大。該事例再次證實了芯片潛在安全風險來源從設計階段延伸至制造階段,給芯片安全帶來新的挑戰。

應根據應用需求合理選擇工藝制程

近年來,隨著技術的不斷進步,芯片工藝水平也得到逐步提高,較小的工藝制程能夠在同樣大小的硅片上容納更多數量的芯片,可以增加芯片的運算效率;也使得芯片功耗更小。

但是,芯片尺寸的縮小也有其物理限制,摩爾定律正在逐漸失效,當我們將晶體管縮小到 20nm左右時,就會遇到量子物理中的問題,晶體管存在漏電現象,抵消縮小芯片尺寸獲得的效益;另外,必須采用更高精度的機器進行芯片的掩膜蝕刻,會帶來制造成本高、良品率下降等問題。

由此可見,芯片的工藝制程并不是越小越好,在我們推進核心芯片自主化研制過程中,絕不能一味追求高端工藝和高性能,而是根據應用需求選擇國內成熟制造工藝,做到量力而行、夠用就好。

如何實現真正意義的自主可控

盧錫城院士指出,自主可控至少應包括三個方面的涵義:一是信息系統的軟件在設計和制造階段不會被對手插入惡意功能,導致潛藏的不安全隱患;二是無論平時、戰時都能按需提供相應軟硬件產品,供應保障不受制于人;三是掌握核心技術,軟硬件產品能適應技術進步或需求變化自主發展。

多年來實踐經驗告訴我們,核心芯片的國產化是一項長期艱苦的工作,無任何捷徑可走,依靠買來的技術只會讓我們的信息系統成為“房子蓋在沙堆上”,只會讓信息系統的發展永遠被別人“牽著鼻子走”。唯有把核心技術和自主知識產權牢牢掌握在自己手里,堅持芯片設計、流片、生產全過程國產化,才能做到信息安全不受制于人,產業發展不受制于人,也才會有真正意義上的自主可控。