【導讀】MOS管的驅動對其工作效果起著決定性的作用。設計師既要考慮減少開關損耗,又要求驅動波形較好即振蕩小、過沖小、EMI小。這兩方面往往是互相矛盾的,需要尋求一個平衡點,即驅動電路的優化設計。

概述

MOS管的驅動對其工作效果起著決定性的作用。設計師既要考慮減少開關損耗,又要求驅動波形較好即振蕩小、過沖小、EMI小。這兩方面往往是互相矛盾的,需要尋求一個平衡點,即驅動電路的優化設計。驅動電路的優化設計包含兩部分內容:一是最優的驅動電流、電壓的波形;二是最優的驅動電壓、電流的大小。在進行驅動電路優化設計之前,必須先清楚MOS管的模型、MOS管的開關過程、MOS管的柵極電荷以及MOS管的輸入輸出電容、跨接電容、等效電容等參數對驅動的影響。

MOS管的模型

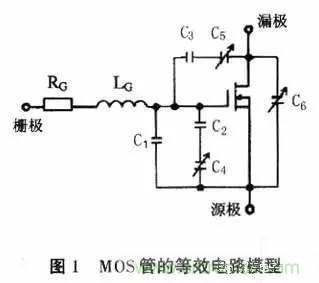

MOS管的等效電路模型及寄生參數如圖1所示。圖1中各部分的物理意義為:

(1)LG和LG代表封裝端到實際的柵極線路的電感和電阻。

(2)C1代表從柵極到源端N+間的電容,它的值是由結構所固定的。

(3)C2+C4代表從柵極到源極P區間的電容。C2是電介質電容,共值是固定的。而C4是由源極到漏極的耗盡區的大小決定,并隨柵極電壓的大小而改變。當柵極電壓從0升到開啟電壓UGS(th)時,C4使整個柵源電容增加10%~15%。

(4)C3+C5是由一個固定大小的電介質電容和一個可變電容構成,當漏極電壓改變極性時,其可變電容值變得相當大。

(5)C6是隨漏極電壓變換的漏源電容。

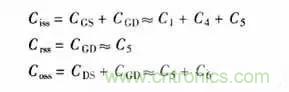

MOS管輸入電容(Ciss)、跨接電容(Crss)、輸出電容(Coss)和柵源電容、柵漏電容、漏源電容間的關系如下:

MOS管的開通過程

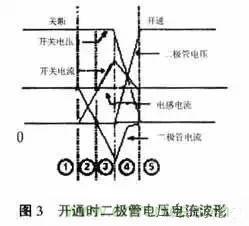

開關管的開關模式電路如圖2所示,二極管可是外接的或MOS管固有的。開關管在開通時的二極管電壓、電流波形如圖3所示。

在圖3的階段1開關管關斷,開關電流為零,此時二極管電流和電感電流相等;

在階段2開關導通,開關電流上升,同時二極管電流下降。開關電流上升的斜率和二極管電流下降的斜率的絕對值相同,符號相反;

在階段3開關電流繼續上升,二極管電流繼續下降,并且二極管電流符號改變,由正轉到負;

在階段4,二極管從負的反向最大電流IRRM開始減小,它們斜率的絕對值相等;在階段5開關管完全開通,二極管的反向恢復完成,開關管電流等于電感電流。

圖4是存儲電荷高或低的兩種二極管電流、電壓波形。從圖中可以看出存儲電荷少時,反向電壓的斜率大,并且會產生有害的振動。而前置電流低則存儲電荷少,即在空載或輕載時是最壞條件。所以進行優化驅動電路設計時應著重考慮前置電流低的情況,即空載或輕載的情況,應使這時二極管產生的振動在可接受范圍內。

柵極電荷QG和驅動效果的關系

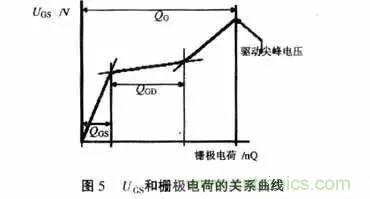

柵極電荷QG是使柵極電壓從0升到10V所需的柵極電荷,它可以表示為驅動電流值與開通時間之積或柵極電容值與柵極電壓之積。現在大部分MOS管的柵極電荷QG值從幾十納庫侖到一、兩百納庫侖。

柵極電荷QG包含了兩個部分:柵極到源極電荷QGS;柵極到漏極電荷QGD—即“Miller”電荷。QGS是使柵極電壓從0升到門限值(約3V)所需電荷;QGD是漏極電壓下降時克服“Miller”效應所需電荷,這存在于UGS曲線比較平坦的第二段(如圖5所示),此時柵極電壓不變、柵極電荷積聚而漏極電壓急聚下降,也就是在這時候需要驅動尖峰電流限制,這由芯片內部完成或外接電阻完成。實際的QG還可以略大,以減小等效RON,但是太大也無益,所以10V到12V的驅動電壓是比較合理的。這還包含一個重要的事實:需要一個高的尖峰電流以減小MOS管損耗和轉換時間。

重要是的對于IC來說,MOS管的平均電容負荷并不是MOS管的輸入電容Ciss,而是等效輸入電容Ceff(Ceff=QG/UGS),即整個0

漏極電流在QG波形的QGD階段出現,該段漏極電壓依然很高,MOS管的損耗該段最大,并隨UDS的減小而減小。QGD的大部分用來減小UDS從關斷電壓到UGS(th)產生的“Miller”效應。QG波形第三段的等效負載電容是:

優化柵極驅動設計

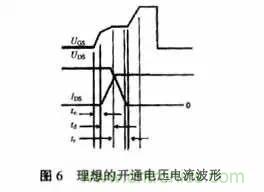

在大多數的開關功率應用電路中,當柵極被驅動,開關導通時漏極電流上升的速度是漏極電壓下降速度的幾倍,這將造成功率損耗增加。為了解決問題可以增加柵極驅動電流,但增加柵極驅動上升斜率又將帶來過沖、振蕩、EMI等問題。優化柵極驅動設計,正是在互相矛盾的要求中尋求一個平衡點,而這個平衡點就是開關導通時漏極電流上升的速度和漏極電壓下降速度相等這樣一種波形,理想的驅動波形如圖6所示。

圖6的UGS波形包括了這樣幾部分:

UGS第一段是快速上升到門限電壓;UGS第二段是比較緩的上升速度以減慢漏極電流的上升速度,但此時的UGS也必須滿足所需的漏極電流值;UGS第四段快速上升使漏極電壓快速下降;UGS第五段是充電到最后的值。當然,要得到完全一樣的驅動波形是很困難的,但是可以得到一個大概的驅動電流波形,其上升時間等于理想的漏極電壓下降時間或漏極電流上升的時間,并且具有足夠的尖峰值來充電開關期間的較大等效電容。該柵極尖峰電流IP的計算是:電荷必須完全滿足開關時期的寄生電容所需。

應用實例

在筆者設計的48V50A電路中采用雙晶體管正激式變換電路,其開關管采用IXFH24N50,其參數為:

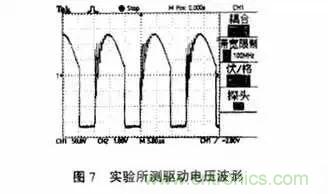

根據如前所述,驅動電壓、電流的理想波形不應該是一條直線,而應該是如圖6所示的波形。實驗波形見圖7。

結論

本文詳細介紹了MOS管的電路模型、開關過程、輸入輸出電容、等效電容、電荷存儲等對MOS管驅動波形的影響,及根據這些參數對驅動波形的影響進行的驅動波形的優化設計實例,取得了較好的實際效果。

影響MOSFET開關速度除了其本身固有Tr,Tf外,還有一個重要的參數:Qg (柵極總靜電荷容量).該參數與柵極驅動電路的輸出內阻共同構成了一個時間參數,影響著MOSFET的性能(你主板的MOSFET的柵極驅動電路就集成在IRU3055這塊PWM控制芯片內); r6 @0 k" S/ l3 }4 u, r/ W

廠家給出的Tr,Tf值,是在柵極驅動內阻小到可以忽略的情況下測出的,實際應用中就不一樣了,特別是柵極驅動集成在PWM芯片中的電路,從PWM到MOSFET柵極的布線的寬度,長度,都會深刻影響MOSFET的性能.如果PWM的輸出內阻本來就不低,加上MOS管的Qg又大,那么不論其Tr,Tf如何優秀,都可能會大大增加上升和下降的時間

偶認為,BUCK同步變換器中,高側MOS管的Qg比RDS等其他參數更重要,另外,柵極驅動內阻與Qg的配合也很重要,一定 程度上就是由它的充電時間決定高側MOSFET的開關速度和損耗..

看從哪個角度出發

電荷瀉放慢,說明時間常數大。時間常數是Ciss與Rgs的乘積。柵源極絕緣電阻大,說明制造工藝控制較好,材料、芯片和管殼封裝的表面雜質少,漏電少。時間常數大,柵源極等效輸入電容也大。柵源極等效輸入電容,與管芯尺寸成正比并與管芯設計有關。通常,管芯尺寸大,Ron(導通電阻)小、跨導(增益)大。

柵源極等效電容大,會增加開關時間、降低開關性能、降低工作速度、增加功率損耗。Ciss與電荷注入率成正比,可能還與外加電壓有關并具有非線性等。以上,均是在相同條件下的對比。從應用角度出發,同等價格,多數設計希望選用3個等效電容(包括Ciss)小的器件。Ciss=Cgd+Cgs,充放電時間上也有先后,先是Cgs充滿,然后是Cgd.。

柵源極等效電容大,會增加開關時間、降低開關性能、降低工作速度、增加功率損耗。Ciss與電荷注入率成正比,可能還與外加電壓有關并具有非線性等。以上,均是在相同條件下的對比。從應用角度出發,同等價格,多數設計希望選用3個等效電容(包括Ciss)小的器件。Ciss=Cgd+Cgs,充放電時間上也有先后,先是Cgs充滿,然后是Cgd.。