【導讀】可控硅SCR(Silicon Controlled Rectifier)結構靜電防護器件由于其自身的正反饋機制,具有單位面積泄放電流高、導通電阻小、魯棒性強、防護級別高的優點,但同時它還引入了觸發電壓高響應速度慢、維持電壓低易閂鎖的缺點。

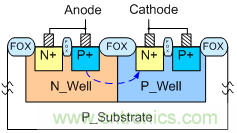

可控硅器件能夠以較小的版圖面積獲得較高ESD防護等級,因此,此類器件已在集成電路片上靜電防護中占有一席之地。但是在深亞微米CMOS工藝中SCR器件仍然具有高的開啟電壓的缺點,觸發電壓一般高于20V,且高于輸入級的柵氧化層擊穿電壓。隨著工藝水平的不斷進步,柵氧化層的厚度不斷減小,擊穿電壓進一步降低,因此,避免內核電路薄柵氧化層器件永久損壞的必要措施是減小SCR器件開啟電壓提高開啟速度。如圖1所示為簡單橫向SCR器件剖面圖,針對此結構降低觸發電壓的器件結構有MLSCR和LVTSCR;針對此結構提高開啟速度的一般方法是采用輔助觸發電路,例如,柵極耦合技術、熱載流子觸發技術、襯底觸發技術、雙觸發技術等。本文介紹幾種降低觸發電壓提高開啟速度的方法。

圖1 簡單橫向SCR器件剖面圖

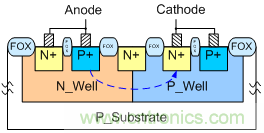

1、改進型SCR(Modified Lateral SCR,MLSCR)

如圖2所示,MLSCR通過在N阱/P阱的結面上增加N+擴散區來降低此結的雪崩擊穿電壓。通過此法可將開啟電壓降低到12V,但還不足以保護輸入級的薄柵氧化層,因此,MLSCR與LSCR一樣需要與二級保護器件配合來實現輸入級的靜電保護。當然,由于其開啟電壓的降低,二級保護器件的版圖面積可以減小。而對于輸出級,由于兩級ESD保護會給正常工作下的電路帶來信號延時,LSCR和MLSCR一般不用于輸出級的靜電保護。

圖2 MLSCR器件剖面圖

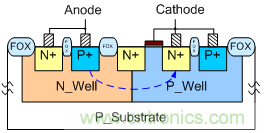

2、低觸發電壓SCR(Low-Voltage Triggering SCR,LVTSCR)

如圖3所示,LVTSCR通過在結構中嵌入一個NMOS將器件開啟電壓降低到約7V,與短溝NMOS的漏擊穿電壓或穿通電壓相近。此器件可獨立使用作為CMOS集成電路的輸入級ESD保護,極大地減小了ESD保護電路的版圖實現面積。而作為輸出級保護時,需要在LVTSCR和輸出級之間加入小的串聯電阻以保證ESD保護的有效性。

圖3 LVTSCR器件剖面圖

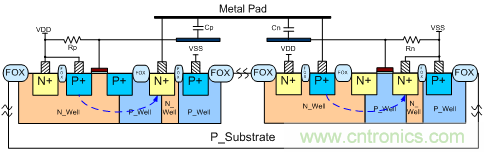

3、柵極耦合的LVTSCR(Gate-Coupled LVTSCR)

如圖4所示為互補型柵極耦合LVTSCR,此器件采用非雪崩擊穿機制來開啟。通過合理設置Cn和Cp的電容值,可以使耦合到柵上的電壓在電路正常工作狀態下小于內嵌NMOS/PMOS的閾值電壓,而在ESD應力到來時大于內嵌NMOS/PMOS的閾值電壓。LVTSCR的開啟電壓可以通過調整內嵌NMOS/PMOS柵極的耦合電壓來設置。耦合電壓越大,LVTSCR的開啟電壓越低,快速開啟的LVTSCR可有效保護輸入/輸出級。

圖4 柵極耦合的 LVTSCR器件結構

4、襯底觸發SCR(Substrate-Triggered SCR,STSCR)

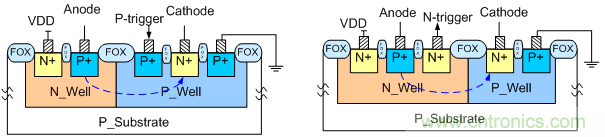

如圖5所示為P型和N型襯底觸發SCR器件,它們分別通過在傳統LSCR器件中加入P+或N+擴散區作為觸發節點。襯底觸發SCR器件的開啟機制屬于電流觸發事件。當電流被加在SCR器件的襯底,也即寄生三極管的基極時,SCR可以快速觸發并進入閂鎖狀態。隨著襯底觸發電流的增大,開啟電壓下降、開啟時間縮短。當然,此器件的應用需要外加RC偵測電路。

圖5 襯底觸發的SCR器件結構

推薦閱讀: