【導讀】對于數字波束成形相控陣,要生成本地振蕩器(LO) ,通常會考慮的實現方法是向分布于天線陣列中的一系列鎖相環分配常用基準頻率。對于這些分布式鎖相環,目前文獻中還沒有充分記錄用于評估組合相位噪聲性能的方法。

在分布式系統中,共同噪聲源是相關的,而分布式噪聲源如果不相關,在 RF 信號組合時就會降低。對于系統中的大部分組件,這都可以非常直觀地加以評估。對于鎖相環,環路中的每個組件都有與之相關聯的噪聲傳遞函數,它們的貢獻是控制環路以及任何頻率轉換的函數。這會在嘗試評估組合相位噪聲輸出時增加復雜性。本文基于已知的鎖相環建模方法,以及對相關和不相關貢獻因素的評估,提出了跟蹤不同頻率偏移下的分布式PLL貢獻的方法。

對于任何無線電系統,都需要為接收器和激勵器精心設計 LO生成的實現方法。隨著數字波束成形在相控陣天線系統中不斷普及,需要在大量分布式接收器和激勵器中分配 LO 信號和基準頻率,這讓設計變得更加復雜。

在系統架構層面需要權衡的因素包括,分配所需的LO頻率或分配較低的頻率基準,以及在靠近使用點的物理位置產生所需的LO。通過鎖相環從本地產生 LO 是一種高度集成的現成選項。下一個挑戰是評估來自各種分布式組件以及集中式組件的系統級相位噪聲。

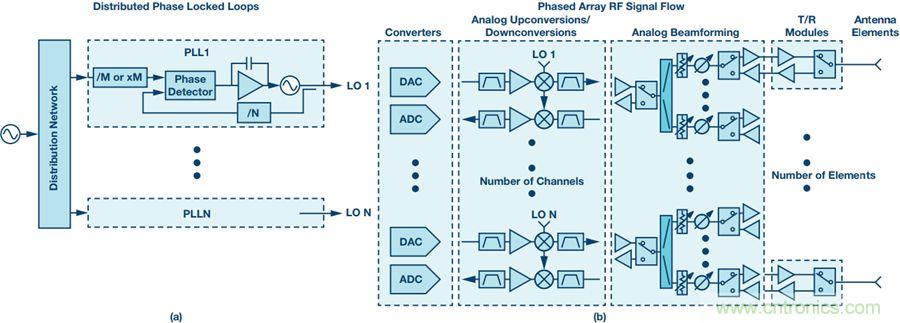

采用分布式鎖相環的系統如圖1所示。常用基準頻率被分配至多個鎖相環,各產生一個輸出頻率。圖1a中的LO輸出被假設為圖1b的混頻器的LO輸入。

圖1. 分布式鎖相環系統。每個振蕩器都被鎖相到一個共同的參考振蕩器上。從1到N的LO信號都應用到相控陣中所示的混頻器的LO端口上。

系統設計人員面臨的一個挑戰是跟蹤分布式系統的噪聲貢獻、了解相關和不相關的噪聲源,并估計整體的系統噪聲。在鎖相環中,這個挑戰變得更加嚴峻,因為噪聲傳遞函數都是鎖相環中的頻率轉換和環路帶寬設置的函數。

動機:組合鎖相環測量示例

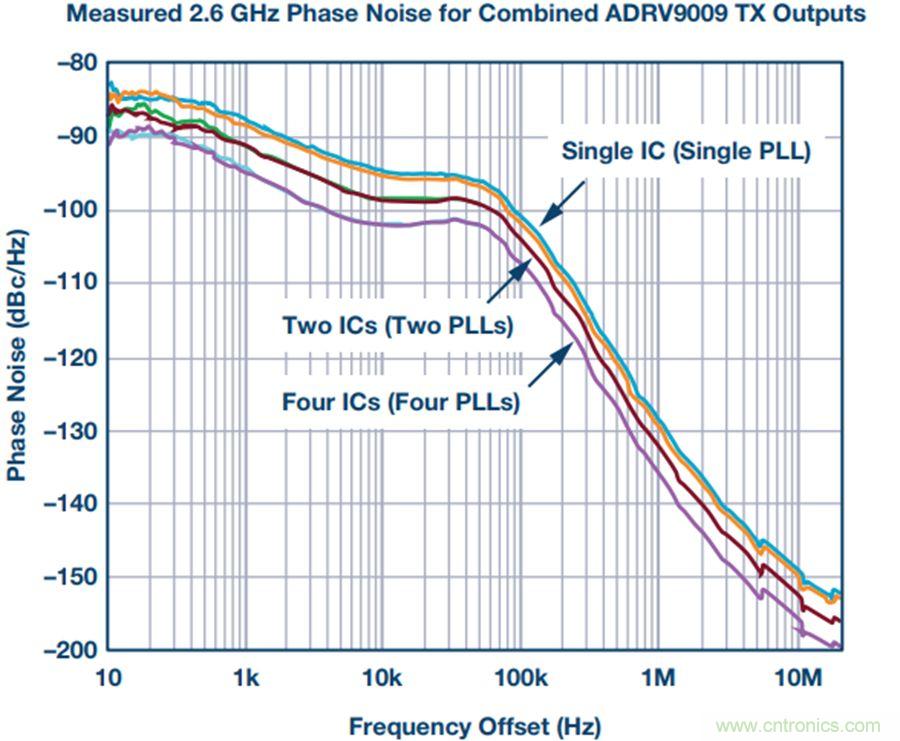

圖2所示為針對組合鎖相環的測量示例。這些數據是通過組合來自多個 ADRV9009 收發器的發射輸出獲得的。圖中所示為單個 IC、兩個組合 IC 和 四個組合 IC 的情況。對于這個數據集,在 IC 組合之后,可以看到明顯的 10logN 改進。為了達到這個結果,需要采用一個低噪聲晶體振蕩器參考源。下一節建模的動機是推導出一種方法,以計算在具有許多分布式收發器的大型陣列中,更廣泛地說是在具有分布式鎖相環的任何架構中,這種測量結果會如何變化。

圖2. 兩個組合鎖相環的相位噪聲測量。

鎖相環模型

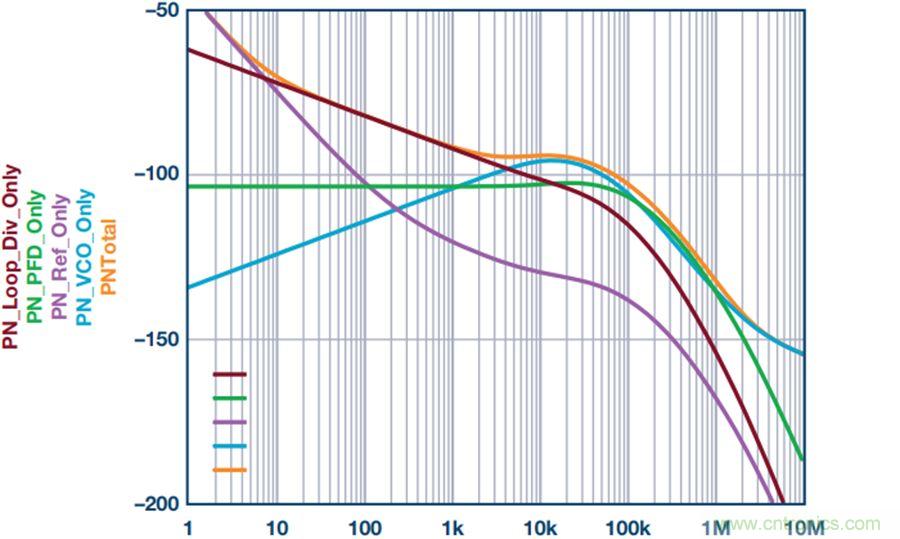

鎖相環中的噪聲建模已有充分的文檔記錄。1-5 圖 3 所示為輸出相位噪聲圖。在這種類型的圖中,設計師可以快速評估環路中每個組件的噪聲貢獻,而這些貢獻因素累計起來即可決定整體的噪聲性能。模型參數設置為代表 圖2 所示的數據,源振蕩器用于估算將大量 IC 組合在一起時的相位噪聲。

圖3. 典型的鎖相環相位噪聲分析,顯示所有組件的噪聲貢獻。總噪聲是所有貢獻因素的總和。

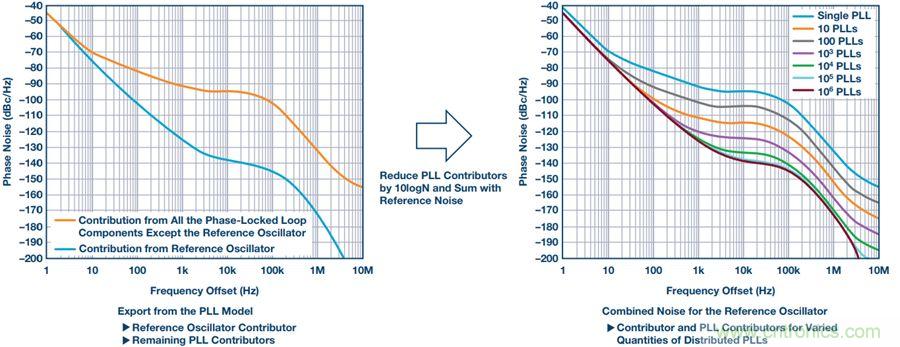

要檢驗分布式鎖相環的效果,首先要從PLL模型導出參考貢獻和其余PLL組件的貢獻。

將已知的PLL模型擴展為分布式PLL模型

本節介紹為具有多個分布式鎖相環的系統計算組合相位噪聲的過程。這種方法的前提是能夠將參考振蕩器的噪聲貢獻與VCO和環路組件的噪聲貢獻分離開來。圖4所示為一個假設的分布式示例,一個參考振蕩器對應多個PLL。這個計算假設了一個無噪聲分布,這不切實際,但可以用來說明原理。假設分布式PLL的噪聲貢獻是不相關的,并減少10logN,其中N表示分布式PLL的數量。隨著通道增加,噪聲在較大偏移頻率下得到改善,對于大型分布系統,噪聲變得幾乎完全由參考振蕩器主導。

圖4. 開始采用分布式鎖相環相位噪聲建模方法:從鎖相環模型中提取參考振蕩器和鎖相環中除參考振蕩器外的所有其他組件的相位噪聲貢獻。作為分布式鎖相環數量的函數,組合相位噪聲假設參考噪聲是相關的,而分布在多個PLL之間的噪聲貢獻是不相關的。

圖4所示的示例簡化了對參考振蕩器分布的假設。在真正的系統分析中,系統設計人員還應該考慮參考振蕩器分布中的噪聲貢獻,它們會降低總體結果。但是,像這樣的簡化分析是非常有用的,能夠讓人了解架構方面的權衡會如何影響系統的總體相位噪聲性能。接下來我們來看看分布系統中相位噪聲的影響。

參考分布中的相位噪聲說明

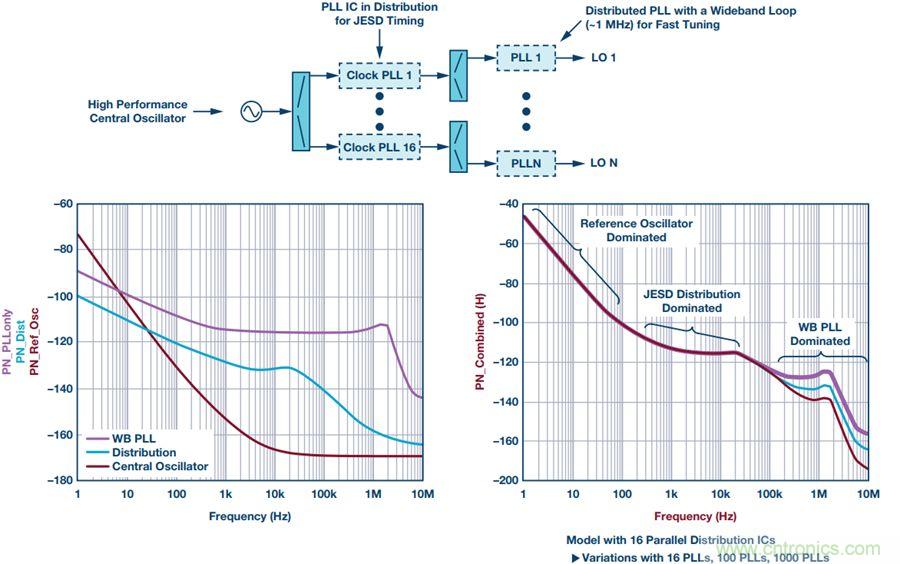

本節評估兩個分布選項示例。考慮的第一種情況如圖5所示。在這個示例中,選擇了一個常用于快速調諧VCO頻率的寬帶PLL。參考信號的分布是通過時鐘PLL IC實現的,這種IC也常用于簡化數字數據鏈路(如JESD接口)的時序限制。左下角顯示了各個貢獻因素。這些貢獻因素位于器件的頻率,并未調整到輸出頻率。右下角的相位噪聲圖顯示了不同數量的分布式PLL的系統級相位噪聲。

圖5. 分布中具有PLL IC的分布式寬帶PLL。

該模型的有些特性值得注意。假設采用一個高性能晶體振蕩器,標稱頻率為100 MHz,中央振蕩器的單個貢獻因素反映在可用的較高端晶體振蕩器上,雖然不一定是最好、最昂貴的可用選擇。雖然中央振蕩器輸出實際上會扇出到有限數量的分布式PLL,但這些PLL會再次按某個實際限值扇出并重復,以實現系統中的完整分布。對于本例中的分布貢獻,假設有16個分布組件,然后假設它們會再次扇出。左下角所示的分布電路的單個貢獻是不含參考振蕩器貢獻的PLL組件的噪聲。本例中的分布假設與源振蕩器同頻率,并根據該函數可用的典型IC來選擇噪聲貢獻因素。

寬帶PLL假設采用S波段標稱頻率,設置采用1 MHz環路帶寬(盡量與實際環路的帶寬一般寬),以進行快速調諧。

值得注意的是,選擇這些模型是為了代表可能的實際情況,且說明了陣列中的累積效應。任何詳細的設計或許都能夠改善特定的PLL噪聲曲線,這在預料之中,且這種分析方法旨在幫助從工程角度去決定應將設計資源分配在哪些位置以獲得最佳總體效果,而不是為了做出相對于可用組件的確切論斷。

圖5右下角的圖計算了LO分布的總組合相位噪聲。其中應用了各個貢獻因素的PLL噪聲傳遞函數,它們都被調整至輸出頻率,也包含PLL環路帶寬的影響。系統數量也包括在內,并且假設它們是不相關的,因此,這個貢獻減少了10logN。假設分布數量為16,如前所述,分布貢獻會減少10log16。在實踐中,隨著分布不斷重復,這種貢獻會進一步減少。但是,額外的噪聲貢獻不那么顯著。對于大型陣列中的扇出分布,噪聲將由第一組有源器件主導。在16組扇出的情況下,如果每個有源器件都是16個其他有源器件的輸入,那么在所有器件互不相關的情況下,16個器件的額外分布層只會降低~0.25 dB。如果繼續這種分布,總體貢獻將更小。因此,為了簡化分析,不會考慮這種影響,且分布的噪聲貢獻通過計算前16個并行分布組件得出。

所得的曲線說明了幾種效果。與單個PLL模型相似,近載波噪聲由基準頻率主導,遠載波噪聲由VCO主導,且在將不相關的VCO組合起來時,遠載波噪聲得到改善。這一點相當直觀。不太直觀的是,模型的值在由分布中的選擇主導的偏移頻率中占較大比重。這一結果導致考慮具有更低噪聲分布和更窄PLL環路帶寬的第二個示例。

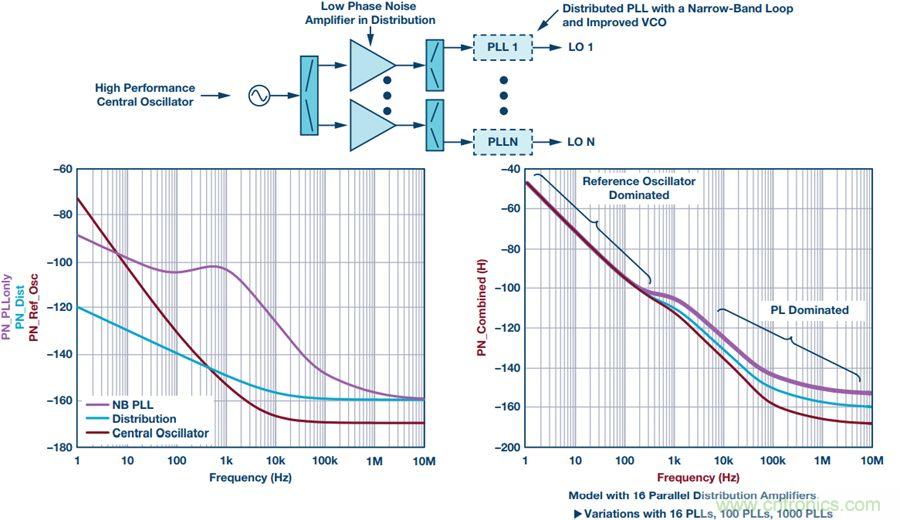

圖6顯示了一種不同的方法。采用相同的低噪聲晶體振蕩器作為參考。但通過RF放大器來分配,而不是通過PLL重定時和重新同步。選擇固定頻率的分布式PLL。這會產生兩種效果:采用單個頻率且調諧范圍較窄時,VCO本質上可以更好,且環路帶寬可以變得更窄。左下角的圖顯示了各個貢獻因素。中央振蕩器與前一個例子相同。請注意分布放大器:考慮低相位噪聲放大器時,它們的性能不是特別高,但比起使用PLL LC(如之前的示例)要好得多。VCO更好、環路帶寬更窄時,分布式PLL在更高偏移頻率下會得到改善,但在~1 kHz的中間頻率下時,實際上要比寬帶PLL示例差。右下角顯示組合結果:參考振蕩器主導低頻,而高于環路帶寬時,性能會由分布式PLL主導,且隨著分布式PLL的陣列尺寸和數量增加而提高。

圖6. 分布式窄帶PLL,分布中具備放大器。

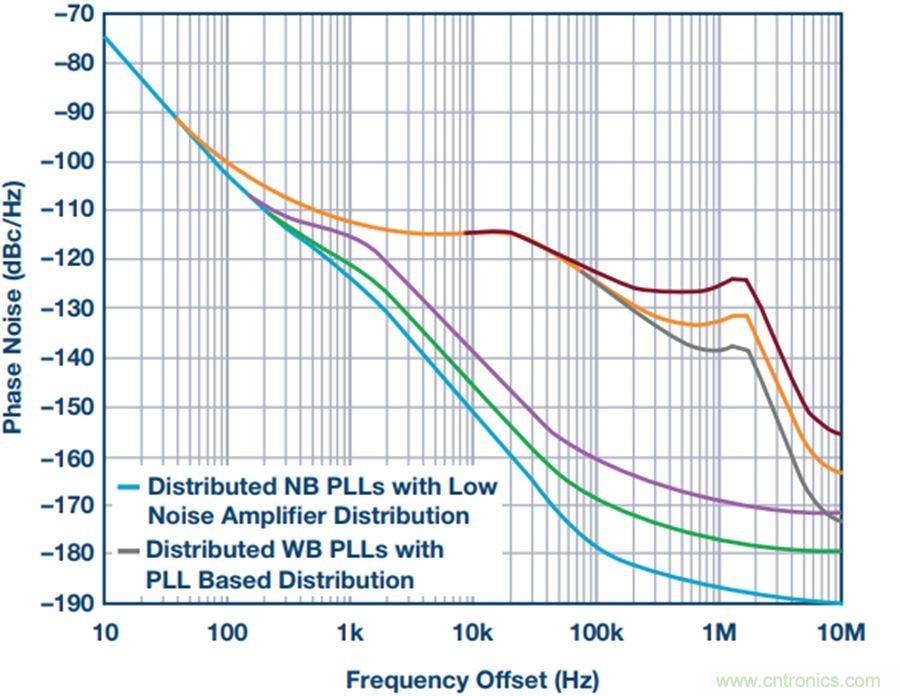

圖7顯示這兩個示例之間的比較。注意~2 kHz到5 kHz偏移頻率范圍內的大范圍差異。

圖7. 圖5和圖6之間的比較,顯示了基于所選的分布和架構的廣泛系統級性能范圍。

分布式PLL陣列級考慮因素

基于對總體系統相位噪聲性能的加權貢獻的理解,可以得出幾個與相控陣或多通道RF系統架構相關的結論。

PLL帶寬

針對相位噪聲優化的傳統鎖相環設計將環路帶寬設置為偏移頻率,以最小化總體相位噪聲曲線。此時的頻率一般是參考振蕩器相位噪聲按輸出頻率標準化后與VCO相位噪聲相交的頻率。對于具有多個鎖相環的分布式系統,這可能不是最佳環路帶寬。分布式組件的數量也需要考慮。

要在采用分布式鎖相環實現的系統中獲得最佳LO噪聲,需要采用一個較窄的環路帶寬來最小化參考振蕩器的相關噪聲貢獻。

對于需要快速調優PLL的系統,通常會擴大環路帶寬來優化速度。遺憾的是,這種優化分布式相位噪聲貢獻的思路本身就是背道而馳的。克服這一問題的選擇之一是在寬帶環路之前設置分布式窄帶清理環路,以降低參考噪聲和分布噪聲相關位置的偏移頻率。

大型陣列

對于使用數千個通道的系統,如果分布式組件的貢獻之間保持互不相關,則系統能夠獲得大幅改進。主要考慮的問題可能圍繞參考振蕩器的選擇展開,以及面向分布式接收器和激勵器維持低噪聲分布系統。

直接采樣系統

隨著速度和RF輸入帶寬持續提升的GSPS轉換器的不斷普及,直接采樣系統正逐漸在微波頻率實現。這導致出現一種有趣的取舍現象。數據轉換器只需要一個時鐘頻率,RF調諧完全在數字域中完成。通過限制調諧范圍,可以構建具備相位噪聲性能更高的VCO。這也使得創建數據轉換器時鐘的PLL的環路帶寬降低。更低的環路帶寬會將參考振蕩器的噪聲傳遞函數降至更低的偏移頻率,從而減少它在系統中的貢獻。這一點,再加上改進過的VCO,在某些情況下可能給分布式系統帶來好處,即使單通道比較結果似乎更青睞替代架構。

組件選項

根據系統架構中所需的選擇,設計人員擁有大量可用的組件選項。2018年度RF、微波和毫米波產品選型指南更新版現已發布,需要的親可點擊“閱讀原文”免費獲取。

集成 VCO/PLL 選項包括 ADF4371/ADF4372。它們提供的輸出頻率分別高達32 GHz和16 GHz,采用–234 dBc/Hz的先進PLL相位噪聲FOM。 ADF5610 提供高達15 GHz的輸出。 ADF5355/ADF5356 的輸出可達13.6 GHz,ADF4356的輸出可達6.8 GHz。

對于單獨的PLL和VCO配置, ADF41513 的工作頻率可達26 GHz,且配有一個先進的鎖相環相位噪聲FOM,其相位噪聲FOM為-234dBc/Hz。有時,在選擇PLL IC時要考慮的一個問題是在盡可能高的頻率上操作鑒相器,從倍增20logN到輸出頻率,最小化環路中的噪聲。 HMC440, HMC4069, HMC698 和 HMC699 采用的PFD的工作頻率高達1.3 GHz。對于VCO,2018年選型指南列出了幾十個VCO選項,范圍從2 GHz到26 GHz不等。

對于直接采樣選項,ADC 和 DAC 均已發布。產品支持在L頻段和S頻段直接采樣。ADC具有更高的輸入頻率帶寬,支持C頻段直接采樣。 AD9208 是一個雙通道3 GSPS ADC,輸入頻率為9 Ghz,支持在上Nyquist區采樣。AD9213是一個單通道10 GSPS ADC,支持具有較大瞬時帶寬的接收器。對于DAC, AD917x系列采用雙通道12 GSPS DAC,AD916x系列采用單通道12 GSPS DAC,經過優化之后可實現更低的殘留相位噪聲和更好的SFDR。兩個系列都支持L頻段和S頻段波形生成。

PS.本節僅提供入門指南。

結語

本文介紹了為采用分布式鎖相環的系統評估相位噪聲的方法。該方法的前提是:每個組件都可以通過其各自的噪聲、組件與系統輸出之間的噪聲傳遞函數、使用的數量以及器件之間的任何相關性來進行跟蹤。所示的示例并不意在對可用的組件或架構功能進行論斷。它們旨在說明一種方法,以幫助設計人員在數字波束成形相控陣中,對LO中的陣列級相位噪聲貢獻因素以及為分布式波形發生器和接收器提供服務的時鐘分布網絡進行有根據的評估。

推薦閱讀: