【導讀】輸入電容可能會成為高阻抗和高頻運算放大器(op amp)應用的一個主要規格。值得注意的是,當光電二極管的結電容較小時,運算放大器的輸入電容會成為噪聲和帶寬問題的主導因素。運算放大器的輸入電容和反饋電阻在放大器的響應中產生一個極點,從而影響穩定性并增加較高頻率下的噪聲增益。因此,穩定性和相位裕量可能會降低,輸出噪聲可能會增加。實際上,以前的一些CDM(差模電容)測量技術依據的是高阻抗反相電路、穩定性分析以及噪聲分析。這些方法可能會非常繁瑣。

在諸如運算放大器之類的反饋放大器中,總有效輸入電容由CDM與負輸入共模電容(或對地的CCM–)并聯組成。CDM難以測量的原因之一是運算放大器的主要任務是防止兩個輸入不相關。與測量CDM的難度相比,直接測量對地的正輸入共模電容CCM+相對容易一些。在運算放大器的同相引腳上放置一個較大的串聯電阻并施加正弦波或噪聲源,就可以使用網絡分析儀或頻譜分析儀來測量由運算放大器輸入電容而產生的-3 dB的頻率響應。假定CCM+和CCM–相同,特別是對于電壓反饋放大器。但是,這些年來,測量CDM變得日益困難;運算放大器的固有特性會迫使其輸入相等,從而自舉CDM,因此所使用的各種不同的技術都無法令人滿意。當輸入被強制分開并進行電流測量時,輸出將試圖進行對抗。-檢測CDM的傳統方法是間接測量,該方法依賴于相位裕度的降低,且因并聯使用CCM–等其他電容而變得更復雜。

我們希望待測運算放大器能夠像客戶平時的用法一樣,在閉環條件下正常運行并執行功能。建議的一種可行方法是分離輸入并進行輸出削波,但是這可能會使內部電路無法工作(取決于運算放大器拓撲),因此實測電容可能無法反映實際工作電容。在這種方法中,不會對輸入進行過度分離,以避免輸入級的非線性以及過多的輸出擺幅或削波。本文將介紹一種簡單直接的CDM測量方法。

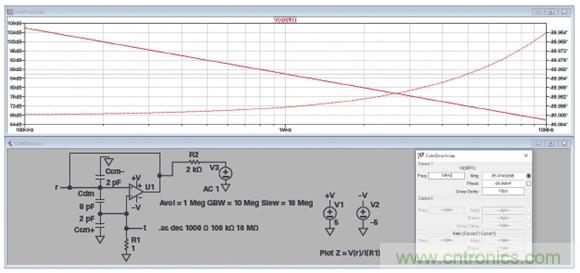

圖1.直接測量LTspice中的CDM阻抗。繪制V(r)/I(R1)曲線以獲得阻抗。在本例中,在1 MHz頻率下,-89.996°時Z為19.89437kΩ (10(85.97/20)),利用公式C = 1/(2π× Z × Freq),Z正好為8 pF。

測量CDM的新方法

作者決定只使用增益為1的緩沖電路,并使用電流源激勵輸出和反相輸入。輸出和反相輸入將僅在運算放大器允許的范圍內變動。在低頻下,輸出的變動很小,因此通過CDM的電流會很小。而在過高頻率下,測試可能會無效,況且結果也沒用。但在中頻下,運算放大器的增益帶寬會下降,但不至于太低,輸出變動仍可提供足夠大的電壓激勵和可測量的通過CDM的電流。

LTspice®的本底噪聲幾乎不受限制,因此可以進行簡單的測試仿真,如圖1所示。當發現該技術在LTspice中相當準確有效后,接下來的問題就是“我可否在現實世界中獲得足夠的SNR以進行良好的測量?”

該相位角幾乎等于-90°,這表明阻抗是容性的。2 pF共模電容不會破壞測量,因為CCM–不在路徑中,且1/(2 ×π× Freq × CCM+) >> 1 Ω。

挑戰:找到合適的設備和實際測試設置

如圖1所示,將2 kΩ電阻串聯在運算放大器的輸出端,以將激勵從電壓源轉換為電流源。這將允許節點“r”中存在小電壓(它不會與在運算放大器的同相引腳中所看到的電壓相差太遠),并將導致小電流流入待測CDM的輸入端之間。當然,現在的輸出電壓很小(由待測器件(DUT)進行緩沖),而且CDM中的電流也很小(在本仿真中為57 nA),因此在工作臺上使用1 Ω電阻進行測量將很困難。LTspice.ac和LTspice.tran仿真沒有電阻噪聲,但現實世界中的1 Ω電阻具有130 pA/√Hz的噪聲,從我們預期的57 nA電容電流中只能產生57 nV信號。

進一步的仿真表明,用50Ω或1 kΩ代替R1不會導致在目標帶寬范圍內的頻率下流入CCM+的損耗電流過大。為了獲得比簡單電阻更好的電流測量技術,可使用跨阻放大器(TIA)代替R1。TIA輸入會連接到運算放大器的同相引腳,在該引腳上需要電流,同時電壓固定為虛地以消除CCM–中的電流。事實上,這正是Keysight/Agilent HP4192A等四端口阻抗分析儀的實現方式。HP4192A可以在5 Hz至13 MHz的頻率范圍內進行阻抗測量。市場上采用相同阻抗測量技術的一些新設備包括具有10 Hz至120 MHz范圍的E4990A阻抗分析儀和具有20 Hz至2 MHz范圍的精密LCR表(如Keysight E4980A)。

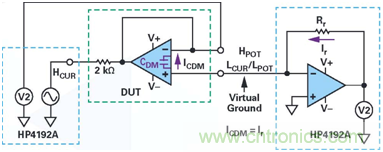

如下面圖2測試電路所示,由于阻抗分析儀內部的TIA,運算放大器的同相引腳保持虛地狀態。正因如此,CCM+的兩個端子都被視為處于地電位,因此不會影響測量。DUT的CDM兩端產生的小電流將流經TIA的反饋電阻Rr,然后由內部電壓表進行測量。

圖2.CDM測試電路。

任何使用自動平衡電橋1阻抗測量方法的四端口設備都是測量CDM的合適選擇。它們設計為從內部振蕩器產生正弦波,該內部振蕩器以零為中心點,具有正負擺幅,可用于雙電源供電。如果運算放大器DUT由單電源供電,則應調整偏置功能,以使信號不會發生對地削波。圖3中使用了HP4192A,并顯示了與DUT的詳細連接。

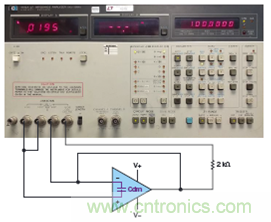

圖3.CDM直接測量方法的測試設置。

圖4顯示了確切的測試設置,以使電路板和連線對CDM的寄生電容貢獻極小。任何通用電路板均可用于低速運算放大器,而高速運算放大器則需要更嚴格的PCB板布局。垂直接地的銅分隔板能確保輸入端和輸出端看不到與DUT CDM平行的其他場路徑。

圖4.HP4192A設置電路板演示。右側為通過2 kΩ的激勵和電壓回讀。所用DUT是貼于LB2223實驗板上的8引腳SO封裝的LT1792。TIA位于HP4192A內部的左側。

結果與討論

首先,在測量電路板的板電容時沒有使用DUT。圖4所示電路板的測量條件是16 fF電容且沒有DUT。這是一個相當小的電容,可以忽略不計,因為通常CDM的預期值為幾百至幾千fF。

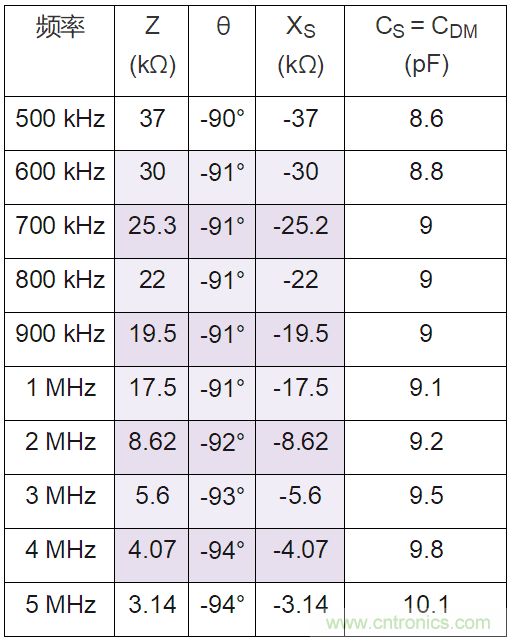

Most JFET and CMOS input op amps were measurable using this new CDM measurement使用這種新的CDM測量技術,可以測量大多數JFET和CMOS輸入型運算放大器。為了說明該方法,以測量低噪聲精度JFET運算放大器LT1792為例。下表列出了在一定頻率范圍內的阻抗(Z)、相位角(θ)、電抗XS和CDM的計算值。當相位角為-90°時,阻抗表現為純容性。

表1.電源為±15 V時,LT1792在不同頻率下的阻抗測量

上述表1給出了在500 kHz至5 MHz頻率范圍內的測量結果。在該頻率范圍內的相位接近于純容性(相位角為-89°至-90°)。同時,電抗XS決定了總輸入阻抗,即Z≈XS。CDM的計算平均值約為10.2 pF。最高測量頻率為5 MHz,因為該器件帶寬僅可達5.6 MHz。更低頻率下的結果變得非相干。推測這是由于運算放大器的行為使輸出電壓降低,CDM電流迅速消減,同時XS阻抗在低頻時變大。

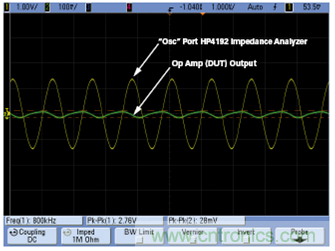

還應在每個階躍頻率處檢查運算放大器的輸出,以確保它不會被阻抗分析儀產生的信號過驅。來自HP4192A的該信號的幅度可在0.1 V至1.1 V范圍內調節,這剛好足以在運算放大器的輸出中產生擺動,并使反相輸入引腳中的電壓電平略微發生變動。圖5顯示了頻率為800 kHz時,運算放大器輸出端的峰峰值無失真信號(綠色信號)為28 mV。2.76 V峰峰值幅度(1 V rms)的黃色信號是直接從分析儀的振蕩輸出端口探測得的。公平起見,可以任意決定不允許輸出失真,不論是對DUT還是對HP4192A檢波器。盡管該設置相對來說并不受探頭效應的影響,但在獲取阻抗和相位的實際數據時已經將探頭移除。

圖5.在HP4192A“Osc”輸出端口和運算放大器輸出引腳探測到的輸出。

我們進行了在不同電源電壓下測量CDM的測試。CDM對電源和共模電壓的依賴性會隨運算放大器的不同而有所不同;不同的拓撲和晶體管類型預計會導致高壓電源和低壓電源不同的結寄生效應。表2給出了電源穩定在±5 V范圍內LT1792的結果。CDM的測量平均值為9.2 pF,與采用±15 V電源時的結果10 pF相當接近。因此,可以得出結論,LT1792的CDM不會隨電源電壓的改變而發生顯著變化。這與其CCM形成了鮮明的對比,后者會隨電源電壓發生顯著變化。

表2.電源為±5 V時,LT1792在不同頻率下的阻抗測量

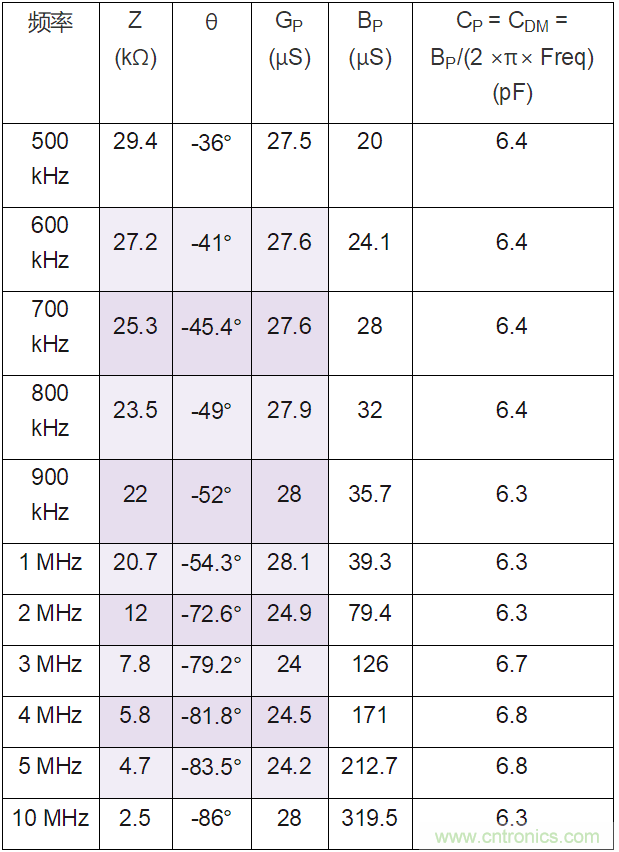

同時,雙極性輸入運算放大器幾乎與其FET同類產品一樣簡單。但是,由于它們與CDM電流并聯,因此它們的高輸入偏置電流和電流噪聲較為明顯。此外,雙極性差分對輸入內在的固有差分電阻RDM也與CDM并聯。表3以低噪聲精密放大器ADA4004為例,顯示了其阻抗測量。顯然,相位并不表示純容性行為,因為它遠離-90°。盡管4 MHz、5 MHz和10 MHz頻率非常接近,但并聯等效阻抗RC模型將適合本例,以便能夠從其他電阻中提取出CDM。因此,表3中顯示了在一定頻率范圍內的并聯電導GP、電納BP和CDM的計算值,其中假定CP等于CDM。

表3.電源為±15 V時,ADA4004在整個頻率范圍內的阻抗測量

根據表3中的結果,可以估算出ADA4004的CDM約為6.4 pF。結果還表明,在表3所示的整個頻率范圍內,CDM具有相當大的并聯電導GP,并非純容性CDM。測量顯示該雙極性運算放大器的實際輸入差分電阻約為40 kΩ (1/25 μS)。

附注:我們嘗試了對其他類型運算放大器進行測量,例如零漂移運算放大器(LTC2050)和高速雙極性運算放大器(LT6200)。結果非相干,推測原因是零漂移運算放大器中的開關偽現像以及高速雙極性運算放大器中的過大電流噪聲。

參考結論

測量CDM 并不困難。需要注意的一點是,HP4192A以幅度和角度報告阻抗。電容讀數假定為簡單的串聯RC或并聯RC,而運算放大器的輸入阻抗可能要復雜得多。電容讀數不應僅使用表面標稱值。每個運算放大器均具有各自的獨特情況。輸入阻抗由容性電抗主導的頻率范圍可能因設計而異。輸入級設計、所用器件和工藝、米勒效應以及封裝都可能對差分輸入阻抗及其測量產生很大的整體貢獻。我們對JFET輸入運算放大器和雙極性輸入運算放大器進行了測量,展示了CDM結果以及雙極性輸入運算放大器的RDM結果。

References

參考文獻

1 Gustaaf Sutorius.“阻抗測量的挑戰和解決方案”,是德科技,2014年3月。

致謝

Glen Brisebois感謝Brian Hamilton提出這一挑戰,感謝Aaron Schultz和Paul Henneuse的支持以及Henry Surtihadi、Kaung Win、Barry Harvey和Raj Ramchandani的意見。

Arthur Roxas感謝Paul Blanchard、Matt Duff、Jess Espiritu和Kristina Fortunado提供與Glen一起完成該項目的機會。

作者簡介

Glen Brisebois是硅谷ADI公司信號調理部門的一名應用工程師。他曾就讀于加拿大阿爾伯塔大學,獲得物理學和電氣工程學士學位。他曾與特拉普派教徒和加爾都西會教徒一起隱修數年,但無法停止對電路的思考。現在,他擁有幸福的婚姻和孩子的陪伴。他從事大量電路相關工作,但有時也會提倡ADC。他在EDN雜志上發表的文章《高阻抗傳感器的信號調理》榮獲2006年最佳論文獎。聯系方式:[email protected]。

作者簡介

Arthur Alfred Roxas是線性產品和解決方案部門的產品應用工程師。他于2017年加入ADI公司。在此之前,他曾在一家日本半導體公司從事設計和布局工作。他畢業于馬尼拉市大學,擁有電子和通信工程學士學位,并獲得馬布亞科技學院(位于馬尼拉)電子工程專業碩士學位,主修微電子。

推薦閱讀: