【導讀】本文是兩篇系列文章的第2部分。 第1部分 介紹了在電機控制 應用中,使用sinc濾波器對∑-?編碼數據進行解調。雖然文中說明了同步sinc濾波器的脈沖響應對脈沖寬度調制(PWM)的重要性,并提出了同步策略,但是,同步方案會導致難以正確配置系統。

作為本系列的第2部分,本文提出一種針對同步優化的新型sinc濾波器結構。該濾波器可在需要嚴格控制反饋鏈時序的應用中提高測量性能。接著,第2部分還將討論采用HDL代碼實現sinc濾波器的方法,以及如何在FPGA實現上優化濾波器。最后,給出在一個基于FPGA的3相伺服驅動器上執行的測量結果。

針對同步優化的sinc濾波器

如第1部分所述,通過正確對齊sinc濾波器對PWM的脈沖響應,可以實現無混疊的∑-?測量。盡管該方法很簡單,但是很難(在很多情況下不可能)找到一個理想的系統配置。為了說明這一點,假設sinc濾波器和PWM模塊共用同一個以 fsys運行的系統時鐘源。調制器時鐘 fmclk則由公式1確定。

其中 Dmclk 是調制器時鐘的時鐘分頻數。同樣,PWM頻率 fpwm由公式2確定。

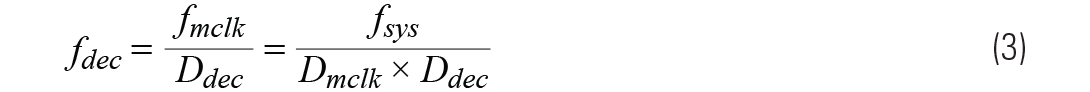

其中 DPWM 是確定PWM頻率的時鐘分頻數。最后,sinc濾波器的抽取率(數據速率)由公式3確定。

其中 Ddec 是抽取后時鐘的時鐘分頻數。為了避免脈沖響應和PWM周期之間的漂移,一個PWM周期內包含的抽取周期數量必須為整數:

其中N為整數。合并公式2、公式3和公式4可得:

顯然,只有有限選擇的時鐘縮放比例 Dx可滿足公式5。此外,時鐘縮放比例的選擇方法往往也受到嚴格限制。例如,系統可能需要以一定的PWM頻率(例如10 kHz)運行或使用一定的調制器 時鐘(例如20 MHz)。另一個麻煩是進行調制器時鐘選擇時,可選數值有限。例如,如果 fsys 為100 MHz,則 Dmclk僅有的合理選 擇應為5到10之間有限范圍內的整數(從20 MHz低至10 MHz)。

考慮到所有這些限制,很難(即便有可能)找到可在脈沖響應和PWM之間實現所需對齊的時鐘縮放比例。通常會發生的情況是,用戶被迫選擇滿足公式5的時鐘縮放比例,而非選擇可產生所需PWM頻率、調制器時鐘和信噪比(SNR)的時鐘縮放比例。而且,如果其中一個頻率隨時間發生變化,則無法找到有效的配 置。這種情況在多軸系統中非常普遍,在這些系統中,單個運動控制器會對網絡中的多個電機控制器進行同步。

雖然對齊方案可提供出色的測量性能,但事實證明它不切實際。以下章節將介紹一種新型sinc濾波器。該濾波器可提供出色的測量性能,同時允許用戶獨立選擇所有時鐘分頻數。

刷新式sinc濾波器

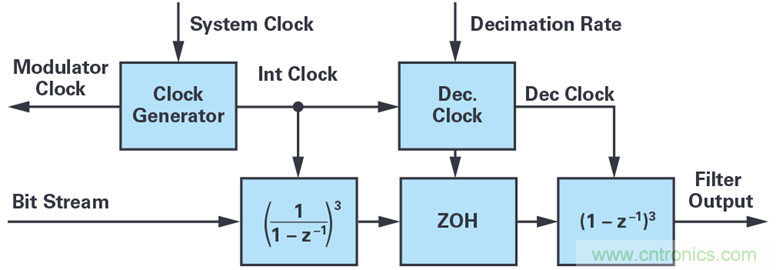

傳統的三階sinc濾波器如圖1所示。濾波器通過按比例縮放系統時鐘來生成ADC的調制器時鐘,而ADC則向濾波器返回一個1位數據流。濾波器功能本身包括三階級聯積分器 1/(1 – z–1)(時鐘速率與調制器速率相同)和三階級聯微分器 1 – z–1(時鐘速率為抽取時鐘)。

圖1. 傳統的三階sinc濾波器。

sinc濾波器和ADC通過施加于其上的同一個時鐘連續工作。因此,濾波器以由抽取時鐘確定的固定速率連續輸出數據。來自濾波器的數據速率通常高于電機控制算法的更新速率,因此許多濾波器輸出被拒絕。只有當脈沖響應以理想測量值為中心時,輸出才會被捕獲并用作反饋。

采用空間矢量調制,在每個PWM周期內僅取兩次相電流平均值。據此,每個PWM周期僅有可能輸出兩個無混疊的sinc數據,因此沒有必要讓濾波器連續運行。實際上僅在需要反饋時啟用測量,然后在所有其他時間禁用測量就足夠了。換句話說,測量以開關模式運行,與傳統的ADC不同。

開關模式運行的問題在于,調制器和濾波器時鐘來源于相同的系統時鐘。這意味著濾波器和ADC均以開關模式運行,我們不建議這樣做,因為這會導致性能下降。其原因是ADC中的調制器是具有一定建立時間和阻尼的高階系統。因此,當將時鐘首次施加于ADC時,需要先建立調制器,然后才能信任其輸出位流。為了解決這些問題,我們提出一種新型濾波器結構(參見圖2)。

圖2. sinc濾波器設計為開關工作模式并對所有狀態進行刷新。

作為標準的sinc濾波器,其核心由三階級聯積分器和三階級聯微分器組成。但是,此濾波器具有一些特性,可以允許新的工作模式。首先,濾波器具有新的時鐘發生器功能,可將調制器時鐘與積分器時鐘分離。這樣就可以連續為ADC提供時鐘,但只在獲取測量值時才啟用積分器時鐘。其次,此濾波器具有新 的濾波器控制功能。以同步脈沖為基準,控制塊處理濾波器工作所需的所有時序和觸發。濾波器控制器的主要功能是刷新濾波器,包括初始化所有濾波器狀態、在開始新測量之前的計時器濾波,以及在適當的情形下啟用/禁用積分器時鐘。最后,濾波器具有一個新的緩沖和中斷控制單元,該單元對所有輸出數 據進行排序并捕獲正確的測量值。當新的測量值準備就緒時,緩沖和中斷單元還會通過中斷來通知電機控制應用。圖3的時序圖顯示了此濾波器的工作方式。

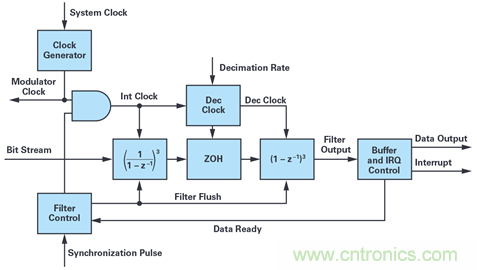

圖3. sinc濾波器在開關模式下的時序圖。

為了開始測量,將同步脈沖(sync pulse)施加于濾波器控制器。通常,此脈沖表示一個新的PWM周期的開始。同步脈沖啟動一個計時器,該計時器被配置為恰好在所需測量點之前1.5個抽取周 期處失效。積分器時鐘和抽取時鐘在這一點啟用,濾波過程開始。經過3個抽取周期(三階sinc濾波器的建立時間)后,緩沖和中斷控制器捕獲數據輸出并置位中斷。請注意在圖3中測量值如何以同步脈沖為中心。該序列在下一個同步脈沖處重復,但是調制器時鐘在濾波器開始工作后就一直保持開啟狀態。

上述sinc濾波器解決了常規sinc濾波器的同步問題。該濾波器及其工作模式無需對PWM頻率、調制器時鐘或抽取率做出任何假設。即使PWM頻率隨時間變化,它也可以與所有系統配置同樣配合良好。由于每次測量都會有效重置濾波器,因此它對時鐘之間的漂移也不敏感。

sinc濾波器的HDL實現

作者發現,一些公開可用的sinc濾波器HDL示例具有一些缺點,會對濾波器的性能產生負面影響或導致意外行為。本章節將討論一些實現問題以及如何設計HDL代碼以在FPGA上獲得最佳性能。

積分器

最純正的sinc3濾波器由三階級聯積分器和三階級聯微分器組成(參見圖1)。首先,考慮z-domain2中的純積分器:

其中u是輸入,y是輸出。積分器的差分方程為:

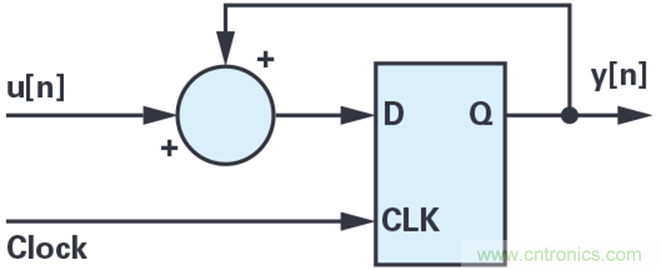

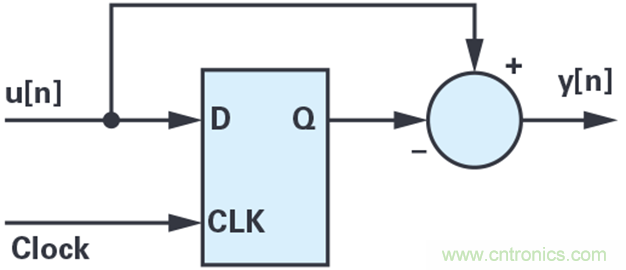

這個一階方程等于一個累加器,非常適合在FPGA等時鐘邏輯中實現。一種常見的實現方法是D型觸發器累加器,如圖4所示。

圖4. 采用D型觸發器的累加器實現。

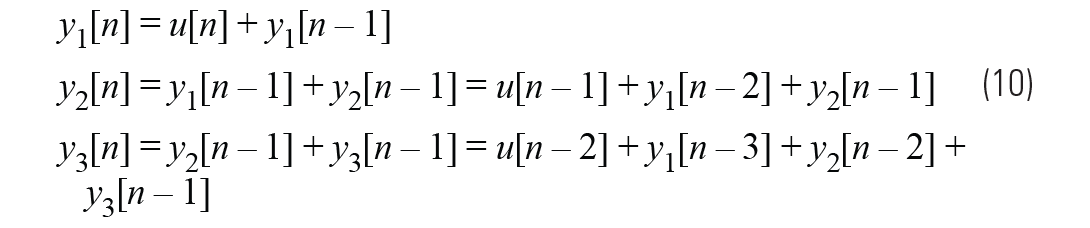

該電路在FPGA上只需幾個邏輯門即可實現。于是,當三個純積分器級聯時,z域中的轉換函數由公式8確定。

公式9顯示了該三階級聯積分器的差分方程:

請注意樣本 n 的輸入如何影響樣本 n 的輸出。

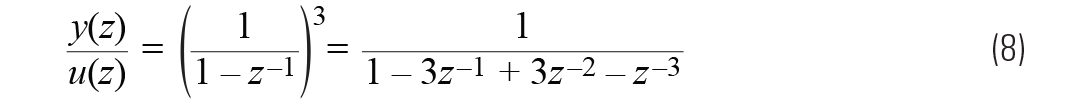

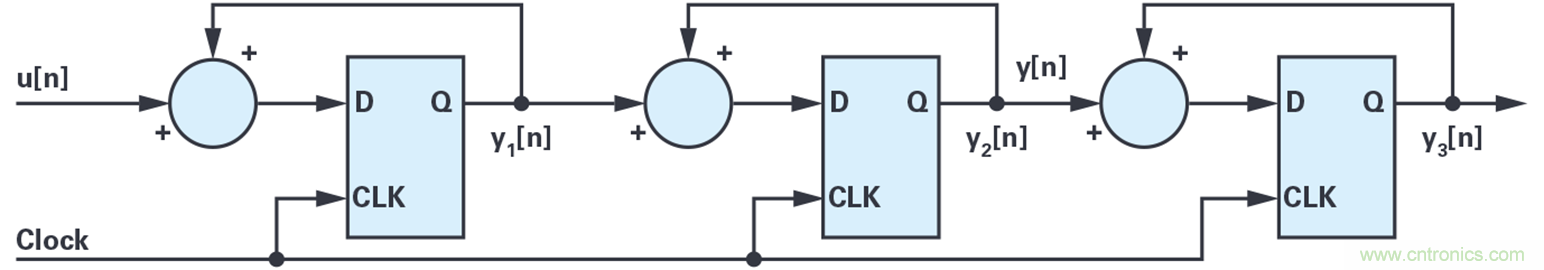

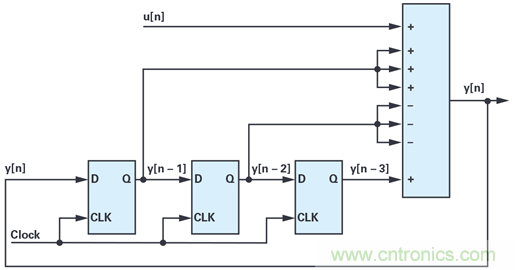

如果使用圖4所示的D型觸發器累加器來實現該三階積分器,則結果如圖5所示。

圖5. 采用D型觸發器實現的三階級聯累加器。

由于這是時鐘電路,因此輸入變化需要經過幾個時鐘周期才會影響到輸出。這一點在查看級聯累加器的差分方程(參見公式10)時會變得更加清晰。

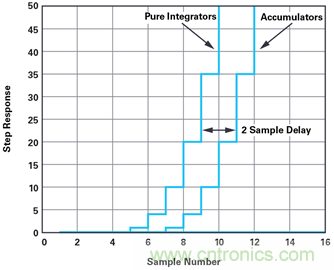

此差分方程與純積分器的差分方程完全不同(參見公式9)。對于累加器,輸入需要兩個時鐘周期才會影響輸出,而對于純積分器,輸入會立即影響輸出。為了說明這一點,圖6分別顯示了在5號樣本處施加單位階躍時公式9和公式10的階躍響應。正如預期的那樣,累加器相較于積分器延遲了兩個樣本。

圖6. 三階級聯積分器和三階級聯累加器的階躍響應。

大多數公開可用的sinc濾波器示例建議使用D型觸發器累加器實現積分器。這樣做的主要理由是其所需門數較少,但是這種簡單的做法也需要付出一定的代價。與濾波器的群延遲相比,兩個調制器時鐘的額外延遲看似微不足道,但該延遲影響了濾波器高頻衰減能力,因此,累加器實現相較于純積分器可提供的 有效位數更少。此外,上述刷新式sinc濾波器需要理想的轉換函數才能正常工作。鑒于這些原因,任何sinc濾波器實現都不應該依賴累加器來實現積分器級。

為了獲得理想的sinc3響應,建議按照公式9直接實現差分。結果如圖7所示。請注意功能框圖包含兩個組成部分:時鐘邏輯部分(觸發器)和組合部分(求和)。此實現需要更多門數,但是它可以提供所需的濾波器性能和延遲。

圖7. 三階級聯積分器的實現。

微分器

與積分器類似,許多公開可用的sinc濾波器示例以錯誤的方式實現微分器級,從而導致濾波器性能下降和意外延遲。本章節討論了微分器級,并就如何通過FPGA實現獲得最佳性能提出了建議。首先,考慮公式11中z域的純微分器以及公式12中相應的差分。2

要在FPGA上實現微分器,最常用的方法是采用D型觸發器(參見圖8)。

圖8. 采用D型觸發器實現的微分器。

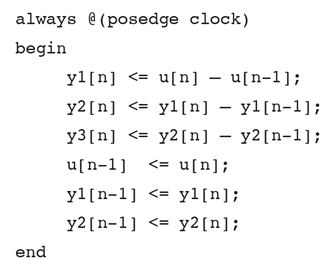

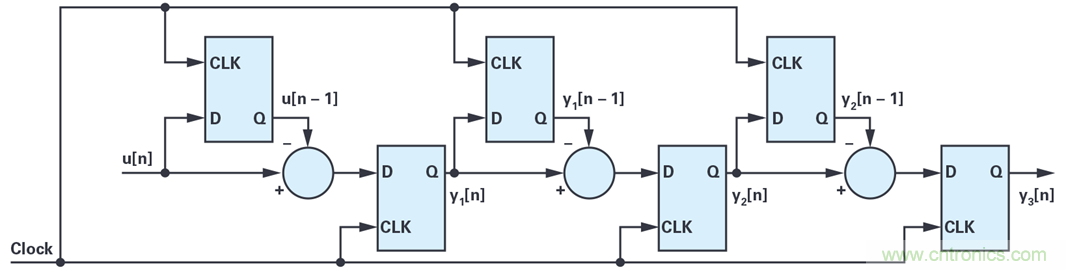

下述HDL代碼片段說明了實現三階D型觸發器微分器的常見方法。這里使用的是Verilog偽碼,但其原理也適用于其他語言。

圖9. 以時鐘邏輯方式實現的三階微分器。

與任何時鐘賦值一樣,先計算所有右邊的語句,并將其賦值給左邊的語句。3為所有語句提供時鐘,并對所有賦值進行并行更新。這會產生一個問題,因為輸出項 (yx[n])依賴于延遲項(u[n-1] 和 yx[n-1]),后者需要率先更新。因此,上述Verilog代 碼片段的邏輯實現如圖10所示。

圖10. 通過時鐘賦值實現的微分器。

由于采用時鐘賦值,微分器的延遲為6個時鐘周期,而不是預期的3個時鐘周期。由于微分器由抽取時鐘提供時鐘,因此濾波器的群延遲和建立時間實際都增加了一倍。但是,這也會影響濾波器的衰減,而且頻率響應不是理想的三階sinc。在已發布的sinc濾波器示例中經常可以看到圖10所示的實現方式,但是我們強烈建議選擇一種模擬理想微分器級的方法。

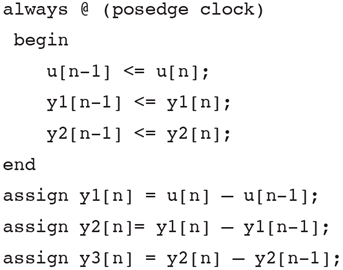

上述Verilog代碼片段可分為兩部分:計算電流輸出的組合部分和更新延遲狀態的時鐘邏輯部分。這種分離使得組合部分可被移至始終受時鐘控制的功能塊之外,如圖11代碼片段所示。

圖11. 以時鐘邏輯與組合邏輯混合方式實現的三階微分器。

使用組合賦值時,沒有與yx計算相關的額外延遲,總延遲從6個時鐘周期降低到理想的3個時鐘周期。推薦的微分器實現功能框圖如圖12所示。

圖12. 采用時鐘邏輯和組合邏輯混合實現的三階級聯微分器。

將上述級聯積分器與微分器實現結合在一起,可使sinc濾波器在衰減和延遲方面獲得理想特性。所有基于∑-?的測量都將受益于這種優化濾波器的實現,尤其是需要知道濾波器確切延遲的刷新式sinc。

測量

T本文提出的∑-?測量系統已經結合基于Xilinx ® Zynq®-7020 SoCC的伺服電機控制器進行了實施和測試。4該系統由60 V 3相永磁伺服電機(Kinco SMH40S5)和3相開關電壓源逆變器組成。SoC運行磁場 定向電機控制算法和用來實時捕獲測量數據的軟件。

對于相電流測量,該系統采用兩個隔離式∑-? ADC (ADuM7701) 跟 隨兩個三階sinc濾波器。該sinc濾波器的實現采用了本文所討論的設計建議,包括刷新式sinc工作模式。為了進行對比,將顯示傳統的連續工作模式濾波器和刷新式濾波器的兩種測量結果。

雖然控制系統具有閉環磁場定向控制,所有測量均通過開環控制進行。閉合電流環路對測量噪聲很敏感,并且噪聲會通過電流環路發生耦合。通過開環工作,可以消除電流控制器產生的任何影響,從而可以對結果進行直接比較。

除模式配置和PWM對齊外,均使用相同的配置(包括抽取率均設置為125)進行測量。因此,測量結果的任何差異都會是影響sinc3脈沖響應能否與PWM正確對齊的因素。控制算法的執行頻率為10 kHz,調制器時鐘為12.5 MHz。

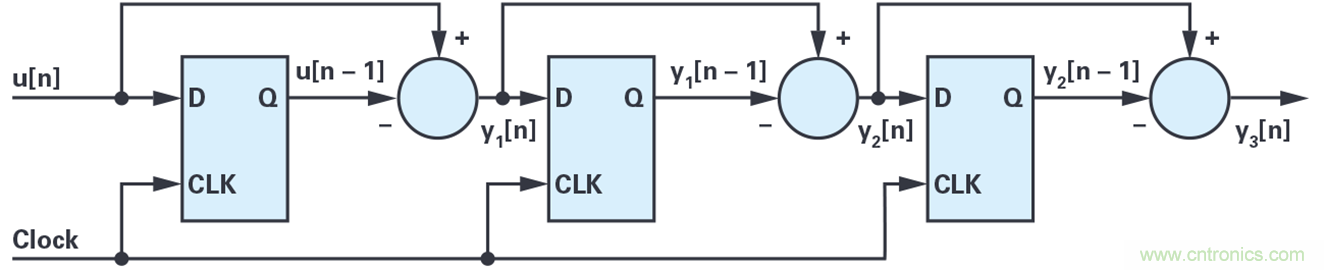

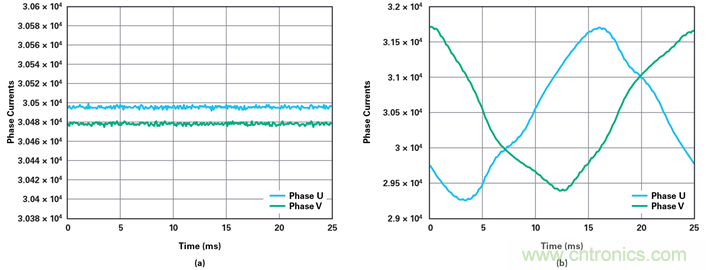

采用連續工作模式sinc濾波器,未對齊脈沖響應

在第一個示例中(參見圖13a),脈沖響應與PWM波形不相關。圖13b顯示了電機停止但功率逆變器在所有相上以50%的占空比切換時兩相電流的測量結果。在此工作模式下,測量顯示了測量結果的噪聲水平。圖13b顯示了電機以600 rpm開環運行時的相電流。電機有四個極點對,因此電氣周期為25 ms。這兩個圖都 顯示出明顯的噪聲,它將嚴重影響任何閉環電流控制器的性能。噪聲電平與基波相電流的幅度無關,因此在輕負載時噪聲性能相對更差。在此示例中,噪聲是由sinc濾波器脈沖響應未對齊引起的,因此對sinc濾波器的抽取率(衰減)幾乎沒有或完全沒有任何增加。

圖13. sinc濾波器脈沖響應與PWM未對齊的連續工作模式。

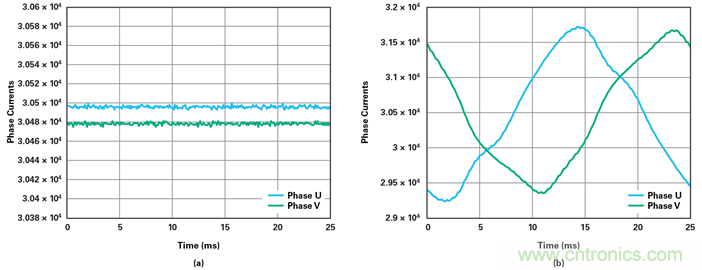

采用連續工作模式sinc濾波器,對齊脈沖響應

圖14顯示了當每個PWM周期中的抽取周期數量為整數,并且脈沖響應與理想測量點對齊時的測量結果。將圖14中的結果直接與圖13中的結果進行比較。

比較圖13和圖14可知,雖然濾波器使用的抽取率相同,但噪聲水平已大大降低。這些示例說明系統配置和同步對于充分利用基于∑-?的信號鏈性能的重要性。

圖14. sinc濾波器脈沖響應與PWM對齊的連續工作模式。

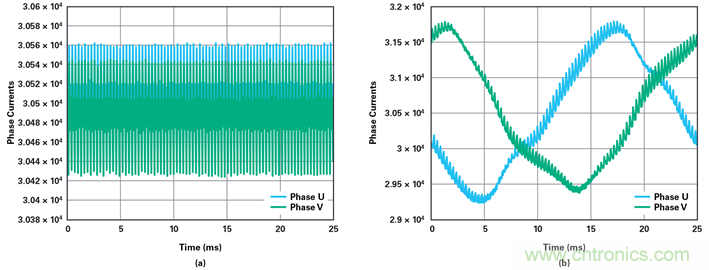

刷新式sinc濾波器

盡管圖14所示的連續工作模式sinc濾波器的結果令人滿意,但該濾波器的挑戰仍然在于如何找到可實現同步的配置。雖然有可能實現連續工作模式sinc濾波器與PWM同步,但這通常并不切實際。采用刷新式sinc濾波器可以解決該問題。

圖15顯示了刷新式sinc濾波器的測量結果。該濾波器配置為在理想測量點附近僅運行3個抽取周期。正如預期的那樣,其性能類似于圖14中的連續工作模式濾波器。

為方便對比,刷新式濾波器使用的配置與連續工作模式濾波器完全相同。不同之處在于,連續工作模式濾波器必須使用此配置,否則性能會降低,如圖13結果所示。與之相反,刷新式濾波器可以在任何系統配置下保持最佳性能。

圖15. sinc濾波器脈沖響應與PWM對齊的刷新式sinc濾波器。

采用未對齊的連續工作模式sinc濾波器(圖13a),其噪聲大小約為一個16位信號中120 LSBs。這相當于噪聲導致近低7位信號的丟 失。刷新式sinc濾波器(圖15a)的噪聲電平大約是一個16位信號中5 LSBs,相當于噪聲導致的信號丟失少于3位。

小結

基于∑-?的相電流測量已廣泛用于電機驅動中,但是要獲得最佳性能,還需正確配置整個系統。本文討論了可能會導致性能不佳的原因以及如何正確設置系統。

配置系統以獲得最佳電流反饋性能往往極具挑戰性,在某些情況下甚至是不可能的。為了解決這個問題,本文提出了一種新型sinc濾波器。該濾波器以開關模式工作,并保證在任何系統配置下均具有出色的性能。

在FPGA上實現sinc濾波器需要進行HDL代碼開發。本文討論了降低濾波器延遲并增加衰減的幾種實現技術。

最后,本文展示了幾種測量結果,這些結果說明了刷新式sinc濾波器同步的重要性及其性能。

參考電路

1作者: Dara O’Sullivan, Jens Sorensen 和 Aengus Murray, AN-1265: 使用ADSP-CM402F/ADSP-CM403F/ADSP-CM407F/ADSP-CM408F sinc 濾波器和AD7403實現隔離式電機控制反饋, ADI公司,2015年4月。

2作者:Alan Oppernheim和Ronald Schafer, 離散時間信號處理, 第3版,Prentice Hall Inc.,2010年。

3 Rajeev Madhavan. ““Verilog HDL快速參考手冊”,Automata Publishing Company,1995年。

4 “Zynq-7000 SoC數據手冊:概述”, Xilinx, Inc.,2018年7月

5 ““KNC-SRV-SMH40S伺服”, Anaheim Automation, Inc.,2019年4月。

推薦閱讀: