【導讀】知道“場效應晶體管”的專利至少比雙極晶體管的發明早了20年,這可能會令人驚訝。然而,雙極型晶體管在商業上的普及速度更快,第一塊由雙極晶體管制成的芯片出現在20世紀60年代,隨著MOSFET制造技術在80年代得到完善,并很快超過了雙極晶體管。

1947年點接觸晶體管發明后,事情開始迅速發展。第一個雙極晶體管是在第二年發明的。然后在1958年,杰克·基爾比發明了第一個集成電路,在同一個芯片上安裝了一個以上的晶體管。11年后,阿波羅11號登陸月球,這要歸功于革命性的阿波羅制導計算機,這是世界上第一臺嵌入式計算機。它是用原始的雙三輸入非柵集成電路制成的,每個門僅由3個晶體管組成。

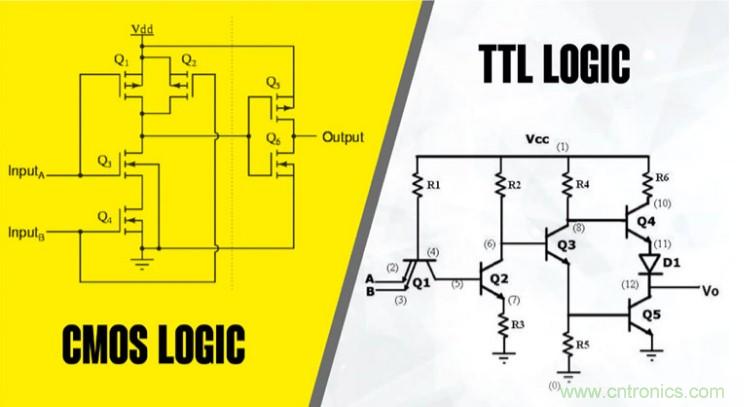

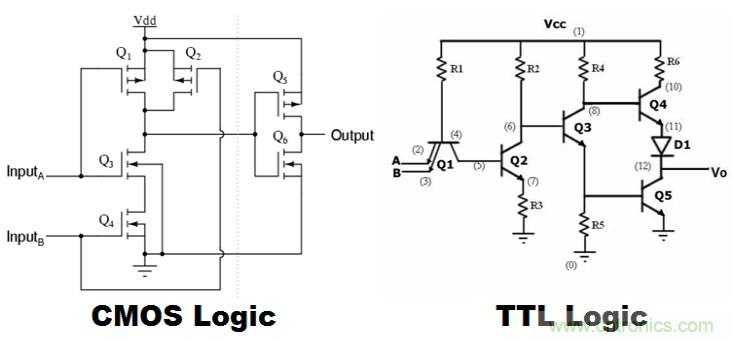

這就產生了流行的TTL(晶體管-晶體管邏輯)系列邏輯芯片,它們是用雙極晶體管構造的。這些芯片的工作電壓為5伏,最高可運行到25兆赫。

這些很快就被肖特基箝位晶體管邏輯所取代,肖特基箝位晶體管邏輯在基極和集電極上增加了一個肖特基二極管以防止飽和,從而大大減少了存儲電荷和減少了開關時間,進而減少了由存儲電荷引起的傳播延遲。

另一系列基于雙極晶體管的邏輯是ECL(發射極耦合邏輯)系列,它在負電壓下運行,與標準的TTL同類產品相比,ECL可以運行到500MHz。

大約在這個時候,CMOS(互補金屬氧化物半導體)邏輯被引入。它同時使用N通道和P通道設備,因此名稱互補。

TTL與CMOS的優缺點

第一個也是最常被談論的是功耗-TTL比CMOS消耗更多的電能。

這在某種意義上是正確的,TTL輸入只是雙極晶體管的基礎,雙極晶體管需要一些電流來打開它,輸入電流的大小取決于內部的電路。當許多TTL輸入連接到一個TTL輸出時,這就成了一個問題,而TTL輸出通常只是一個上拉電阻或一個驅動性能較差的高壓側晶體管。

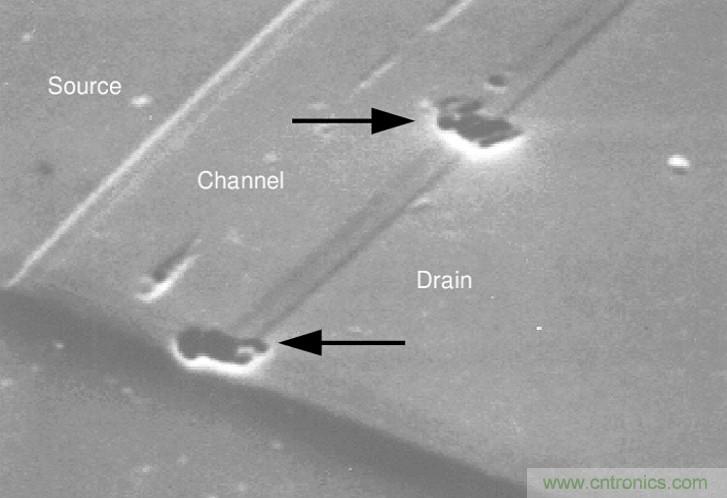

另一方面,CMOS晶體管是場效應的,換句話說,柵極處的電場足以影響半導體通道的傳導。理論上,除了柵極的小漏電流(通常為皮卡或毫安量級)外,不會產生電流。然而,這并不是說即使在更高的速度下,同樣的低電流消耗也是正確的。CMOS芯片的輸入具有一定的電容,因此上升時間有限。為了確保在高頻下上升時間很快,需要一個大電流,在MHz或GHz頻率下可以達到幾安培。這種電流只在輸入必須改變狀態時才被消耗,而TTL的偏置電流必須與信號一起存在。

在輸出方面,CMOS和TTL各有優缺點。TTL輸出要么是圖騰柱,要么是上拉。有了圖騰桿,輸出只能在軌道0.5V范圍內擺動。然而,其輸出電流遠高于CMOS芯片。同時,CMOS輸出可以與電壓控制電阻器相比較,根據負載情況,可以在電源軌的毫伏范圍內輸出。然而,兩個led的輸出電流往往很有限。

由于其較小的電流要求,CMOS邏輯非常適合小型化,數百萬個晶體管可以封裝到一個小區域,而不需要過高的電流。

與CMOS相比,TTL的另一個重要優勢是其耐用性。場效應晶體管依賴于柵極和溝道之間的薄氧化硅層來提供它們之間的隔離。這種氧化層厚度為納米,擊穿電壓很小,即使在高功率fet中也很少超過20V。這使得CMOS對靜電放電和過電壓非常敏感。如果輸入是浮動的,它們會慢慢積累電荷并引起輸出狀態的假變化,這就是為什么CMOS輸入通常被上拉、下拉或接地。TTL在很大程度上不受這個問題的影響,因為輸入端是一個晶體管基極,它的作用更像一個二極管,由于它的阻抗較低,對噪聲不太敏感。

TTL還是CMOS?哪個更好?

CMOS邏輯幾乎在所有方面都取代了TTL。雖然TTL芯片仍然可用,但使用它們并沒有真正的優勢。

然而,對于TTL級的輸入,TTL仍然是標準化的,因此對于TTL級的輸入,TTL仍然不兼容。在實用性方面,CMOS是明顯的贏家。

TTL邏輯家族使用雙極晶體管來執行邏輯功能,CMOS使用場效應晶體管。盡管CMOS比TTL更靈敏,但它的功耗通常要小得多。CMOS和TTL并不是真正的可互換的,隨著低功耗CMOS芯片的出現,TTL在現代設計中的應用非常少。

推薦閱讀: