【導讀】當今世界,設計師們似乎永遠不停地追求更高效率。我們希望以更低的功率輸入得到更高的功率輸出!更高的系統效率需要團隊的努力,這包括(但不限于)性能更高的柵極驅動器、控制器和新的寬禁帶技術。

特別是高電流柵極驅動器,其能夠通過降低開關損耗幫助提升整體系統效率。當FET開關打開或關閉時,就會出現開關損耗。為了打開FET,柵極電容得到的電荷必須超過閾值電壓。柵極驅動器的驅動電流能夠有助于柵極電容的充電。驅動電流能力越高,電容的充放電速度就越快。拉灌大量電荷的能力可以降低功率損耗和畸變。(傳導損耗是另一種FET開關損耗,傳導損耗取決于內部電阻或FET的RDS(on)值,其中,隨著電流通過,FET也會耗散功率。)

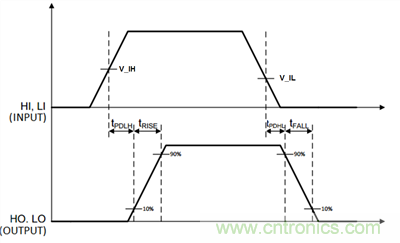

換言之,目標便是降低系統內需要高頻率功率轉化的開關過渡時間。突出該類性能的柵極驅動器規格為上升和下降時間。參見圖1。

圖1:典型的上升和下降時間圖

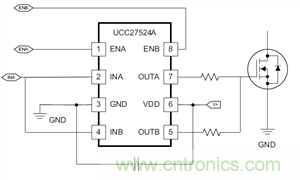

如果您想更進一步,諸如延時匹配等柵極驅動器特性,能有效地讓驅動電流能力翻番。延時匹配指兩個通道之間內部傳播延遲的匹配,可以通過雙通道柵極驅動器的并聯輸出或將兩個通道捆綁在一起實現。例如,TI的UCC27524A具有極其精確的1ns(典型)延遲匹配,可以將驅動電流從5A提升到10A。

圖2所示為UCC27524A的A通道B通道結合在一個驅動器中的范例。INA和INB輸入以及OUTA及OUTB分別為串聯結構。由一個信號控制該并聯組合。

圖2:串聯輸出UCC27524A以使雙驅動電流能力翻番

系統效率提升帶來的結果之一便是功率密度的提升。在隔離電源的功率因數校正(PFC)及同步整流塊、直流/直流模組及太陽能逆變器等應用中,設計師需受到以相同尺寸(或更小尺寸)實現相同輸出功率量的約束,因此,對更高功率密度的需求已經成為一種趨勢。

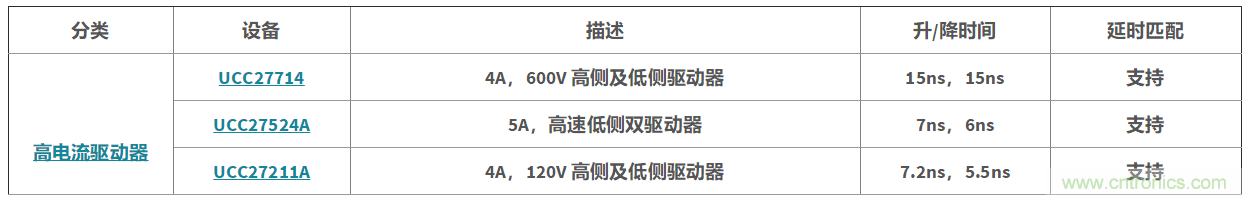

TI的產品組合包括帶高電流、快速升降時間和延時匹配的柵極驅動器。參見表1。

表1:高電流柵極驅動器

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀: