【導讀】作為高速接口IP新銳企業,芯耀輝對USB接口的發展歷史、未來趨勢和設計挑戰等有深刻洞察,并基于多年設計積累和優秀架構提供靈活易用的完整解決方案,幫助設計人員應對挑戰,實現設計目標。

我們對速度的不懈追求,使得終端產品升級換代的節奏越來越快。如何面向未來需求加快產品上市?如何應對高速接口設計及測試挑戰?近日,由全球測試測量行業領先者安立公司、泰克公司及GRL,共同舉辦的2021高速接口聯合測試論壇,針對行業熱點關切,特邀芯片設計、IP及設備相關領導廠商進行深入探討。

作為高速接口IP新銳企業,芯耀輝科技受邀出席本次盛會。芯耀輝科技技術支持總監劉好朋以“消費類電子接口發展展望——USB會一統天下嗎?”為主題進行精彩分享,并深入介紹了芯耀輝USB PHY IP方案,現場反應熱烈。

圖:芯耀輝科技技術支持總監劉好朋

發展歷史丨30年風云,USB王者之氣漸顯

USB全稱是Universal Serial Bus,名稱體現了其通用性強、傳輸率高、兼容性好和即插即用的初心。迄今,USB接口標準已經歷了3個階段。第一階段始于1995年,為解決接口通用性問題,第一代USB標準問世,傳輸速度僅為1.5Mbps,業內反響平平。第二階段自2000年始,USB 2.0傳輸速度達到480Mbps,被廣泛應用于各種數據傳輸應用。但在隨后5年多間,USB標準并無新的亮點。

新的突破在第三階段,以2008年發布USB 3.0、傳輸速度突破至5Gbps為標志。隨后,2013年傳輸速度為10Gbps的USB3.1,2017年傳輸速度達20Gbps的USB3.2陸續發布。2019年發布的最新的USB4,最高速度可達40Gbps,終端產品于2020年底陸續面市,特別是英特爾酷睿11代產品集成了支持USB4的Thunderbolt 4,被業內視為USB4標準開始普及的標志性事件。

圖:USB標準發展史

未來趨勢丨USB技術演進瞄準高速、兼容

多年來,USB接口標準不斷更新升級,得益于強大的兼容性,不同代際共存于市的情況很普遍。劉好朋從USB應用市場采納角度分析,呈現兩種趨勢:一個是傳統應用中,新標準普及節奏快慢不一;另一個是新興應用中,新標準起驅動作用。

舉例而言,游戲、VR/AR等設備對新的USB標準采納最為保守。雖然需求量很大,但它們更渴盼統一接口,整合所有電源線、控制線、數據線、音視頻線等。USB4等新一代USB標準符合以上的需求,更適合這個場景,可支持4K、8K甚至未來的10K視頻傳輸,再加持低延時、可變刷新率等先進特性給用戶帶來更好的使用體驗,將加快該類應用對USB新標準的采納進程。

他還提到應用市場的發展,促使USB接口技術演進呈現以下趨勢:持續挑戰更高傳輸速度;不斷兼容多種協議等。

預計2025年前后,USB接口的傳輸速度有望達到近80Gbps,繼續保持相對Thunderbolt的競爭力。同時, Type-C作為大一統的接口形態,其機械特性和電氣特性會有進一步優化設計;而連接線纜可能全部被主動式線纜取代,來適配長度要求。

USB也將繼續保持對多協議的兼容,包括對不同代際的USB標準,如USB 3.1、USB 3.2和USB4等,以及快充標準USB PD,還有DisplayPort、PCIe、Thunderbolt,未來甚至 HDMI 和 以太網等都有可能將納入USB接口支持范圍,成為名副其實“一統天下”的王者。

挑戰及應對丨芯耀輝先進USB IP,破解高速接口設計挑戰三大難

USB市場空間可觀,但產品快速落地和迭代,給芯片設計和測試提出了更多挑戰:傳輸速度極高,接口協議極多,快充協議極多,協議升級加快。作為高速接口IP供應商,芯耀輝對此有如下洞察,并基于USB PHY IP多年設計積累和優秀架構提供靈活易用的完整解決方案。

● 挑戰一:需要適配各種復雜應用場景。

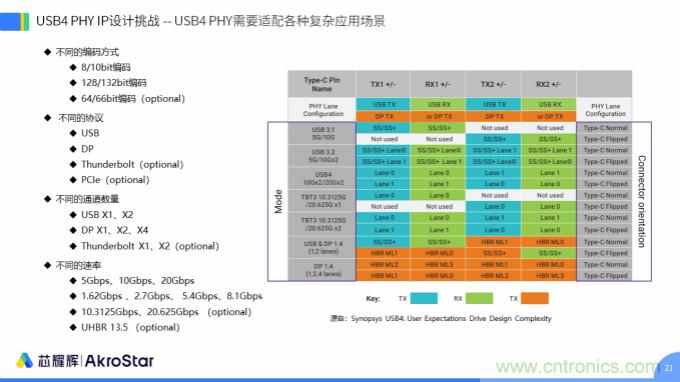

如圖,為支持不同的編碼,包括8/10bit,128/132bit,還有可選的64/66bit;不同的協議,USB、DP,以及可選的Thunderbolt、PCIe等,以及繁多的傳輸速率和協議電氣特性等。IP設計上需要通盤考慮、逐個優化。

圖:USB PHY IP設計挑戰——適配復雜應用場景

● 挑戰二:更加嚴苛的信道插損預算。

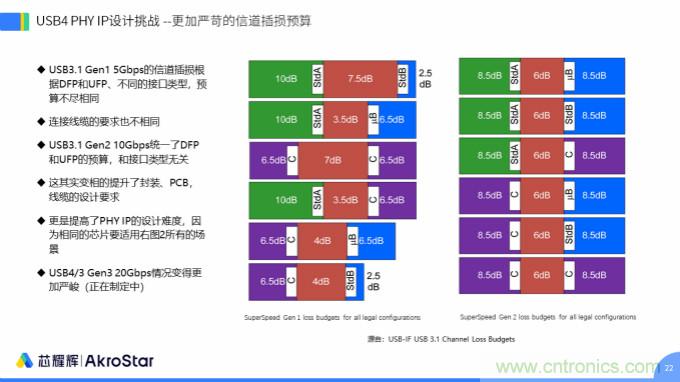

USB3.1 Gen1 5Gbps的信道插損根據DFP和UFP不同、接口類型不同,預算不盡相同,連接線纜的要求也不相同。而USB3.1 Gen2 10Gbp,統一了DFP和UFP的預算,和接口類型、線纜無關。但這其實變相提升了對封裝、PCB、線纜的設計要求,更是提高了PHY IP的設計難度。因為一顆芯片必須要適配多種不同應用場景,對IP設計、整個芯片系統設計和測試提出了更高的要求。

圖:USB PHY IP設計挑戰——嚴苛的信道插損預算

● 挑戰三:USB4復雜的發送端和接收端均衡與嚴格的誤碼率要求。

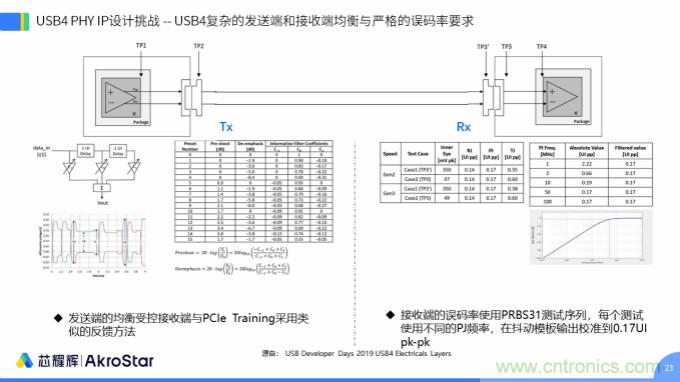

USB4鏈路訓練采用和PCIe Training類似反饋方法,發送端在發送訓練序列的同時,將自身接收端對于對接發送端的FFE請求反饋,在預設值中找到適應的最優均衡值。USB4要支持多達16個預設值的快速遍歷。接收端要適應不同頻率的周期抖動,每一個周期抖動都要通過PRBS31的低誤碼率測試,協議要求誤碼率1e-12,為了盡可能增加系統設計的裕量,通常IP在設計中會把目標誤碼率降低到1e-13,甚至更低水平。

圖:USB4 PHY IP設計挑戰 -- USB4復雜的發送端和接收端均衡與嚴格的誤碼率要求

● 芯耀輝先進USB PHY IP解決方案

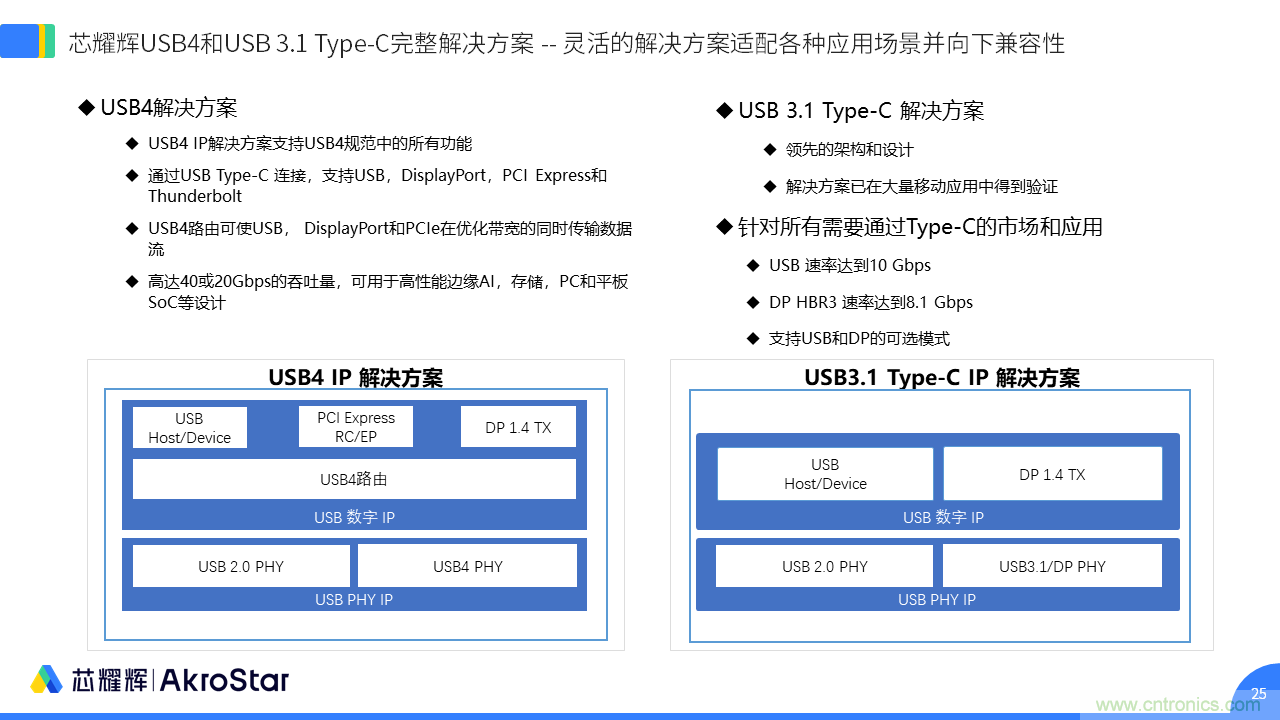

針對這些設計挑戰,芯耀輝提供極具靈活性的完整解決方案適配各種應用場景并向下兼容,包括USB4和USB 3.1 Type-C解決方案。

芯耀輝USB 3.1 Type-C解決方案,具有領先的架構和設計,已在大量移動應用中得到驗證。針對所有需要Type-C的應用,USB速率達到10Gbps,DP HBR3速率達到8.1Gbps,并具有HDCP 2.3 內容保護。

芯耀輝USB4 IP解決方案,支持USB4規范中所有功能;通過Type-C連接,支持USB4、DisplayPort、PCIe和Thunderbolt3;新的Router IP可使USB、PCIe和DisplayPort在優化帶寬的同時傳輸數據流;高達40Gbps(或20Gbps)的吞吐量,可用于高性能AI、高速存儲、PC、筆記本、手機和平板SoC等設計。

圖:芯耀輝USB4和USB 3.1 Type-C完整解決方案優勢

在演講的最后,劉好朋向到場嘉賓介紹稱,芯耀輝科技是一家擁有行業“夢之隊”的初創IP公司,致力于通過先進半導體IP研發服務,賦能客戶的芯片設計和系統應用。芯耀輝科技創始團隊是來自IP設計、芯片設計、軟件等行業頂尖人才,曾與國內外具備量產能力的頂尖和主流客戶一同打造全球領先產品,并長期共同迭代,有著超過20年的深厚積累,深諳芯片設計的痛點,還可提供一系列定制的IP升級服務。芯耀輝科技愿意與更廣泛的客戶攜手合作,助力芯片設計廠商取得更大成功。

推薦閱讀: