【導讀】如果我的模擬設計中包含開關和多路復用器,那么還能改進開關/多路復用器LTspice?模型嗎?當然能,要生成自己的模型并不困難。本文將以工程師角度為您詳細介紹如何為特定的模擬開關構建不錯的宏模型,以及如何獲取參數,為實現物理器件的多個不同的半導體工藝提供支持。

如果我的模擬設計中包含開關和多路復用器,那么還能改進開關/多路復用器LTspice?模型嗎?當然能,要生成自己的模型并不困難。本文將以工程師角度為您詳細介紹如何為特定的模擬開關構建不錯的宏模型,以及如何獲取參數,為實現物理器件的多個不同的半導體工藝提供支持。

我在測試電路之后,發現實際電路與其設計圖之間存在很多差異,電路的動態特性有點出乎意料,其噪聲水平超出要求很多。我需要用仿真器來仿真該電路才能完全理解。

此電路中用到了模擬開關和運算放大器。采用的運算放大器已有完善的宏模型,但是模擬開關宏模型采用的并不是常見類型。開關宏模型文件的標題已經指出,模型參數僅對特定電源和溫度有效。嗯,您可能不知道:我的電路的運行條件與電路模型不一樣。關于模擬開關,它們太過通用,所以一個特定參數模型是不夠的。現有的行業標準模型提供了一個不錯的起點,但是涉及到模擬性能領域時,您可能需要采用新宏模型方法來提高仿真水平。

當我開始研究ADI和其他IC公司提供的多種模擬開關宏模型時,我發現這些宏模型建模時都沒有考慮與電源或溫度的相關性。所以,我必須自行構建宏模型。

構建期間,我認為應由使用最簡單的器件模型的模擬開關中的所有晶體管來提供要仿真的所有行為,但是連接控制引腳和MOS柵級的接口應是最簡單的行為元件。這些都通過使用LTspice仿真器完成,只要將LTspice行為器件轉化為類似SPICE的多項式函數,這些代碼也可以在其他仿真器上使用。我們會按照特定的順序進行仿真。

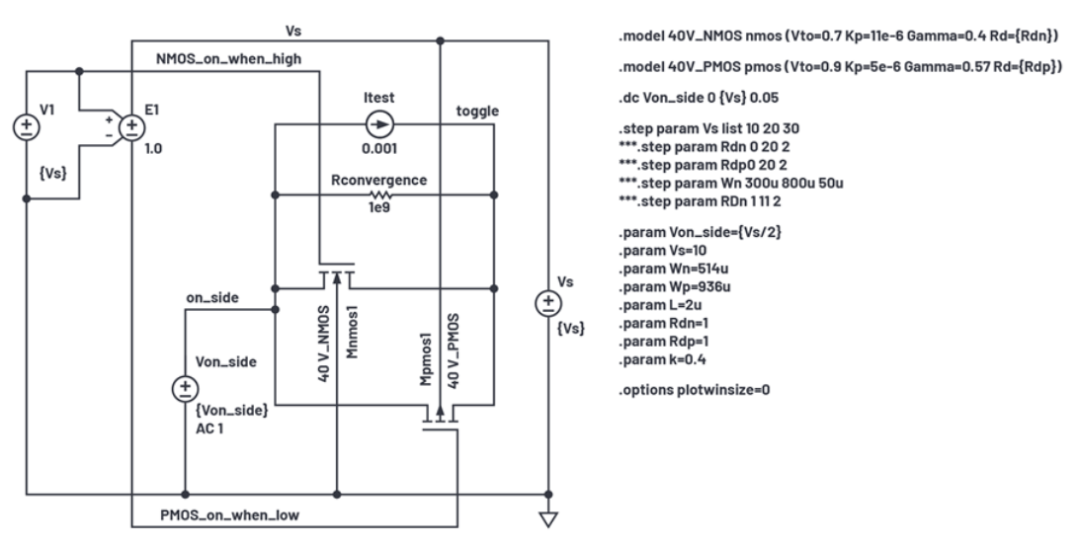

我們將使用最簡單的模型來仿真實際的MOS器件。為了針對導通電阻建模,我們將使用:

W/L,寬度(W)/MOS器件的長度(L)。W/L表示器件的尺寸或相對強度。

VTO, 閾值電壓;gamma(γ),利用器件的反饋偏壓來更改VTO 。反饋偏壓是開啟器件和其主體電壓之間的壓差;主體一般連接到開關中PMOS的正電源和NMOS的負電源。

KP,在模型中,也被稱為K’或K-prime。這個參數模擬工藝的強度,乘以W/L之后,用于調整MOS電流。在給定的工藝中,NMOS的 KP一般為PMOS的約2.5倍。

RD, 器件漏極的寄生電阻。

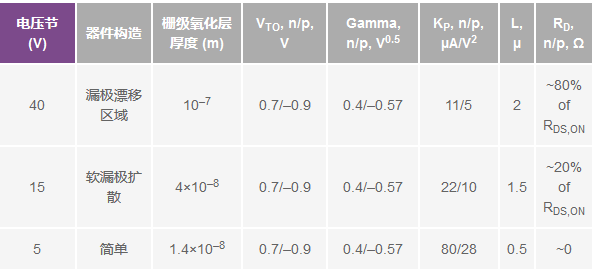

不同的MOS工藝采用不同的內部參數。表1匯總了常見的CMOS工藝、其特性以及和導通電阻相關的內部參數估算值。

表1. 典型半導體工藝參數

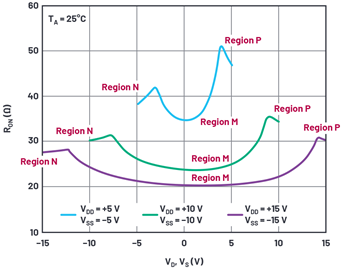

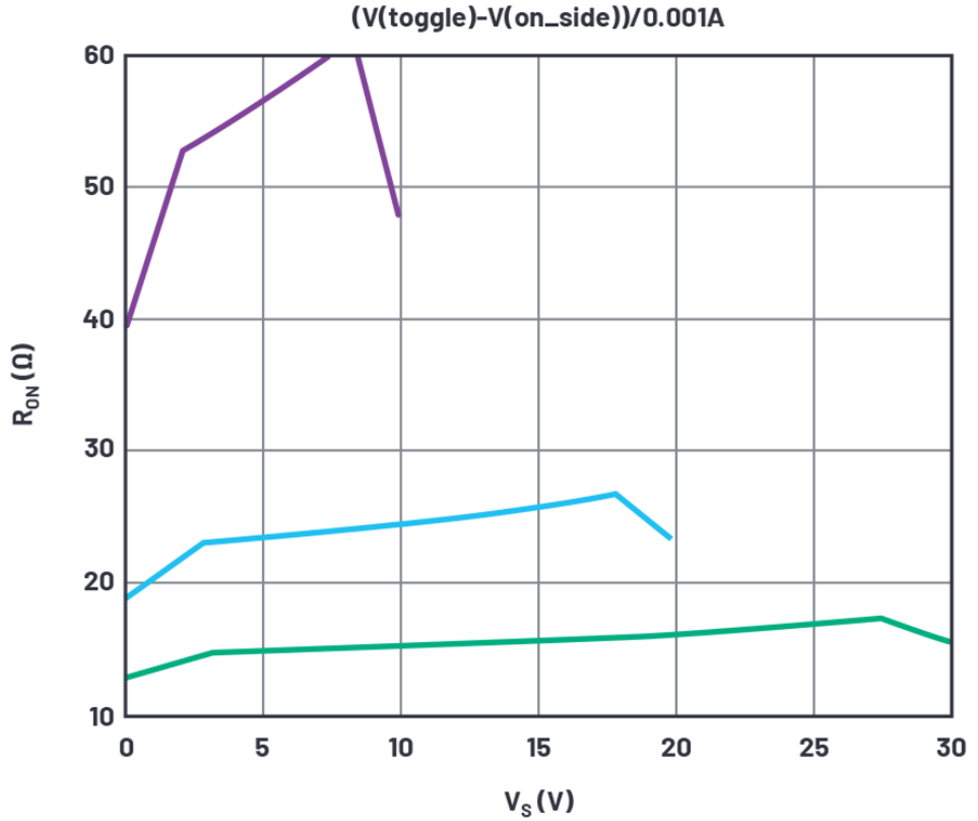

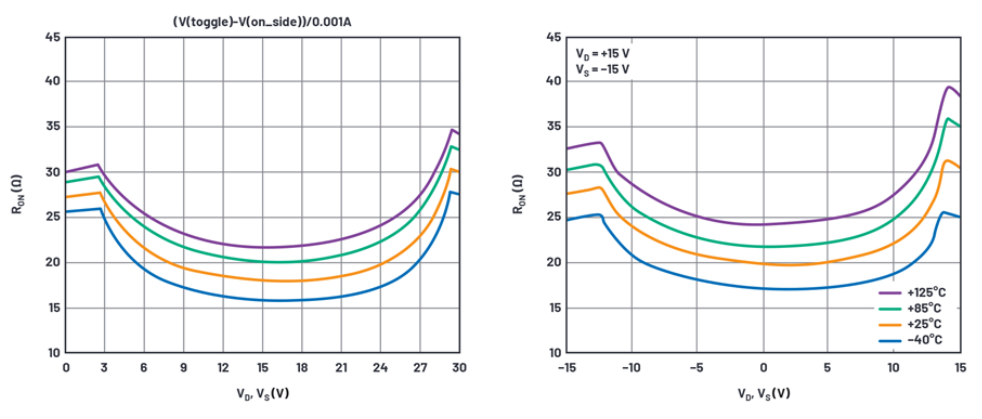

來看一下圖1中我們想要再現的ADG333A RON曲線。

圖1. RON與VD(VS)呈函數關系(雙電源)。

在這個和其他模擬開關中,我們發現一個普遍趨勢:更高的電源電壓會降低導通電阻。對開關MOS柵級施加更高電壓時,導通電阻會降低。我們也發現導通電阻會隨輸入模擬信號電平發生明顯變化。在N區中,開關中的NMOS晶體管完全開啟,且當模擬電壓高于負電源軌時,PMOS晶體管開啟,有助于降低總體導通電阻。區域N的轉折點大致在高于負電源的 PMOS VTO處。

同樣,在區域P中,開關的PMOS器件完全開啟時,大致在低于正電源的 NMOS VTO,NMOS器件開始協助PMOS晶體管。

區域M在區域N和P中間,NMOS和PMOS并行作用,但彼此之間的導通電阻存在差異,具體由電源軌內的模擬信號電平決定。

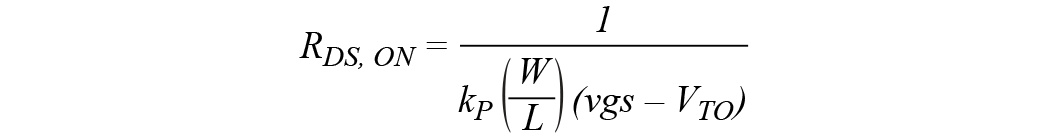

要啟動曲線擬合流程,我們先要估算每個晶體管的尺寸。低壓曲線能夠為晶體管RDS,ON提供最佳曲線擬合。在區域N中,在模擬信號位于負電源電壓范圍內時,PMOS器件關閉,部件的 RON相當于NMOS晶體管的RON 。其中

我們使用40V NMOS典型工藝值,按照圖1中的曲線設置 RDS,ON=38Ω,使用給定的工藝數值,發現WNMOS=2μA/(38Ω×(11×10–6μA/V2)×(10V–0.7V))=514μm。PMOS開關在上方曲線上的導通電阻為47Ω,寬度為936μm。

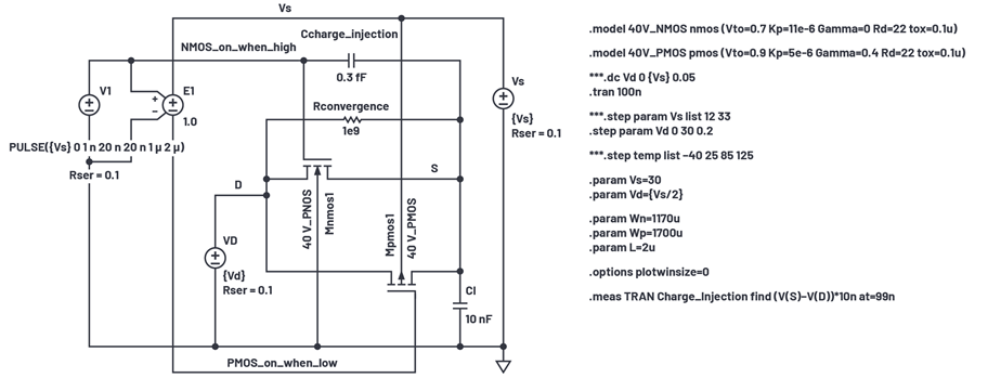

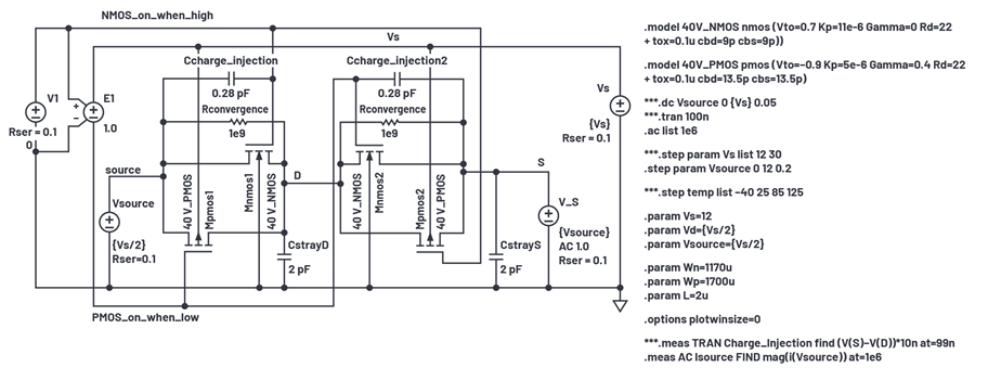

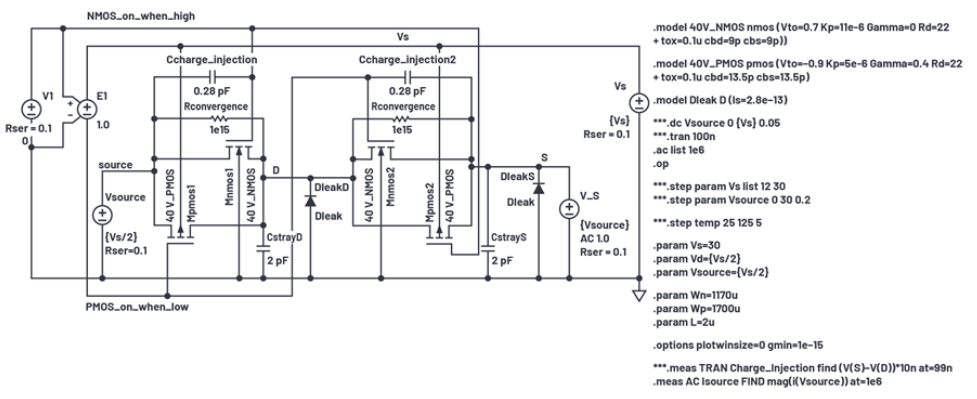

我使用圖2中的LTspice測試電路。注意,參數RDN和RDP、寄生漏極電阻都是中等值。我最開始使用的值為1μ,這導致仿真器收斂變慢。RDN值為1時,仿真速度正常。添加RCONVERGENCE會為開關節點提供可收斂的電導,從而改善仿真器噪聲和速度。我測試了一個浮動電流源,用于測量導通電阻。

圖2. 導通電阻測試電路。

圖3顯示了多種電源供電條件下的仿真結果。

圖3. 采用初始模型值的導通電阻仿真結果。

這個開端相當不錯。低壓端在VS=30V時,仿真的扭結點為3.6V,在數據手冊中為2.7V。從中可以看出,我們應該降低PMOS VTO,但0.9V實際上已經是最小值。最好是可以調節PMOS的gamma,但這只是猜測。

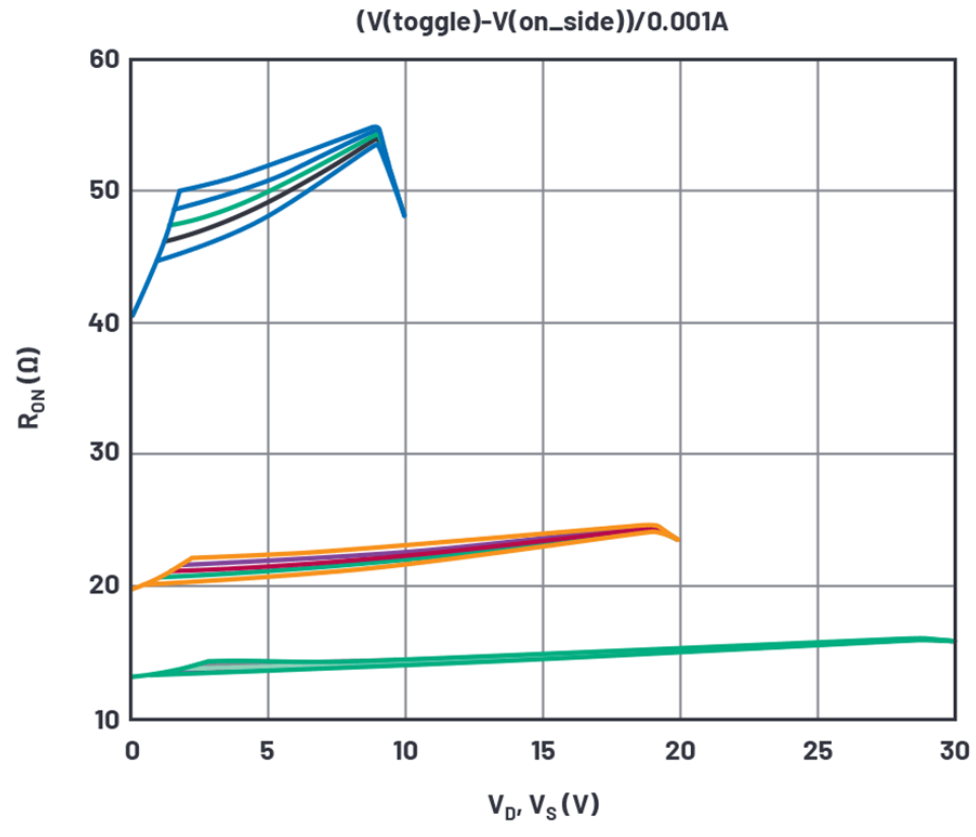

接近最大電源時的扭結點為低于30V電源軌2.5V,在數據手冊中應為~1V。各種gamma值會放大來自電軌的扭結電壓;我們會將NMOSVTO設置為1V,將其gamma設置為0。gamma為0有些出乎意料,但我們只是嘗試進行曲線擬合。圖4所示為PMOS的gamma在幾種電源值條件下步進變化時,得到的仿真結果。我們主要研究一下30V曲線,與較低電源相比,它最大化了gamma的影響。

圖4. gamma-p不同時的導通電阻仿真結果。

根據階梯曲線,我們選擇PMOSgamma=0.4。

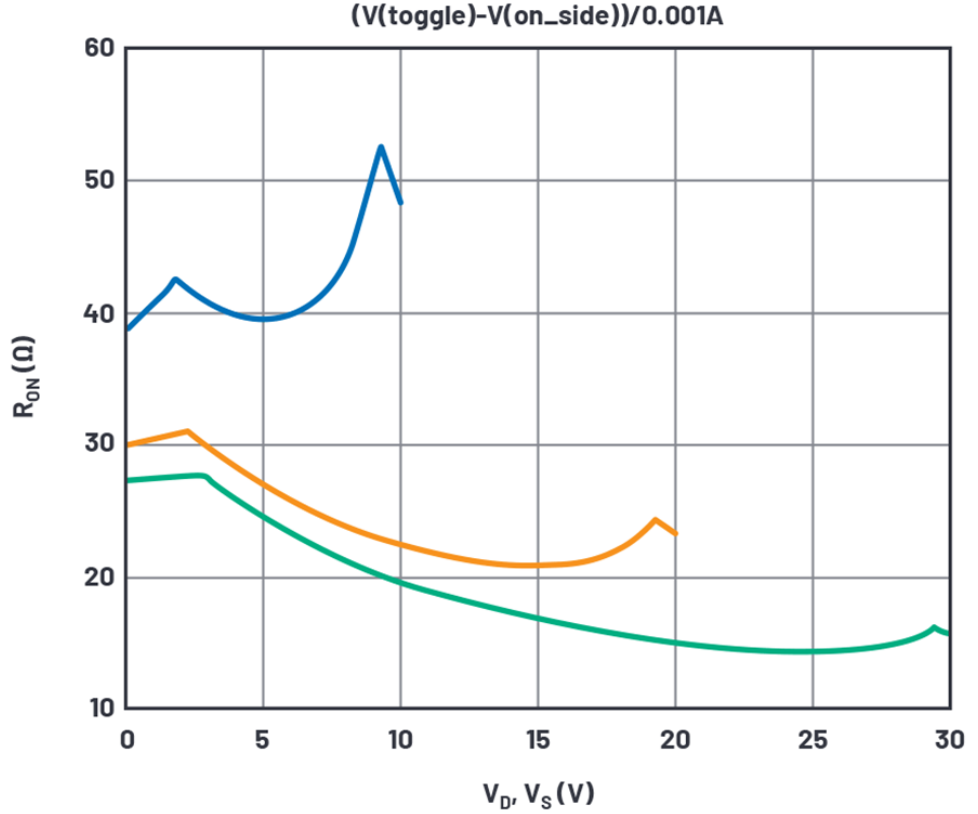

關于RON,可以看出,10V曲線可以表示電源極端(限值)時對應的數據手冊曲線,但對于20V和30V曲線,仿真產生的RON過低。在負電源極端,RONs= RDS,ON(NMOS)+RD(NMOS),在正電源極端,RONs=RDSON(PMOS)+RD(PMOS)。對于高壓電源,RD參數比W/L更重要,對于低壓電源,W/L起決定作用。我們在此會使用兩個變量;這非常費時費力。我們將假設RON隨電源變化,這是因為會對NMOS實施不同程度的增強,但是,RD值不會隨電源電壓變化(好吧,在漏極漂移中,它可能會變化,但是我們還是讓問題保持簡單一些)。如果我們注意到數據手冊中RON在10V和30V電源之間的差異(11.4Ω),我們可以與上方僅采用WN(開關中NMOS的寬度)的曲線比較。在仿真中對WN實施一定的迭代之后,很明顯可以看出我們需要WN=1170μm才能獲得所需的ΔRON,明顯高于最初的猜測值。圖5顯示了我們當前的結果。

圖5. WN 確定時的導通電阻仿真結果。

雖然NMOS的RON具備正確的電源靈敏度,在0V時,曲線的值仍然過低,我們必須增加固定RDN。在增加和迭代RDN之后,我們獲得了最佳值,即RDN=22Ω,對應曲線如圖6所示。

圖6.RDN 確定時的導通電阻仿真結果。

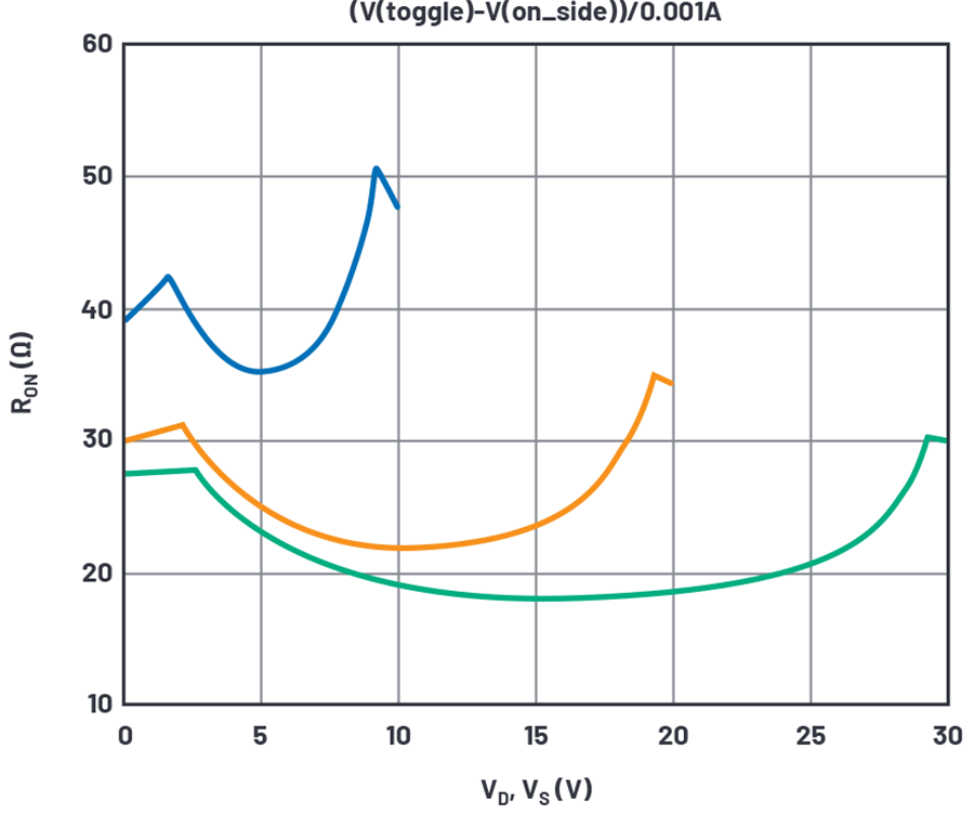

然后,我們確定WP(開關中PMOS的寬度),以仿真最大電壓下的RON,得到WP=1700μm,,也遠高于最初的猜測值。將RDP也設置為22Ω,我們獲得了圖7所示的最終RON曲線。

WP和RDP確定時的導通電阻仿真結果。

一致性非常不錯;只有幾個特性和數據手冊不同。一是轉折點在數據手冊曲線中非常平緩,在仿真中則相當尖銳。這可能是因為使用的簡單MOS模型不支持亞閾值導電性,且仿真器件在與電源軌相差VTO時會真正關閉。實際器件在VTO時不會關閉,而是平緩地降低該電壓下的電流。

另一個錯誤在30V曲線中非常明顯。與數據手冊相比,RON在中等電壓下要低15%。這可能是因為漏極漂移區域的JFET效應,這個效應也沒有在模型中仿真出來。

至于溫度,相對比較符合,但符合程度不是很高,具體參見圖8。

圖8. 各種溫度下的導通電阻仿真和數據手冊結果。

仿真結果與溫度相關,但溫度相關性不如數據手冊曲線高。在仿真模型中,RD沒有溫度系數。RDS可以通過外部電阻和正確的溫度系數模擬,但為了保持簡單性,我們不予考慮。

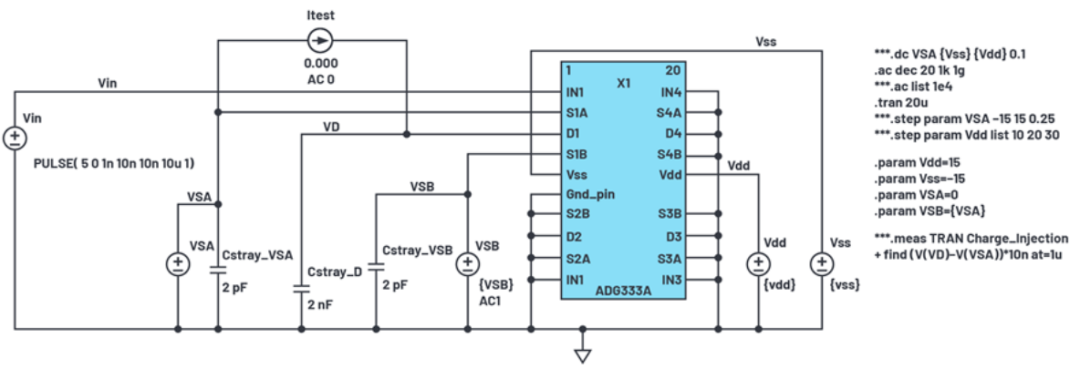

當MOS晶體管關閉時,通道中的電荷必須去往某處,所以會從漏極和源極端逸出。模擬開關關閉時,電荷也會外泄,這被稱為電荷注入。常用的測量方法是:在開啟的開關的一端設置固定電壓,在另一端設置大電容。關閉時,電容會捕捉電荷,并發生小電壓階躍。現在,我們在MOS模型中添加柵級氧化層厚度TOX=1×10–7(柵級電容是最大的電荷注入源)。仿真設置如圖9所示。

圖9. 電荷注入仿真設置。

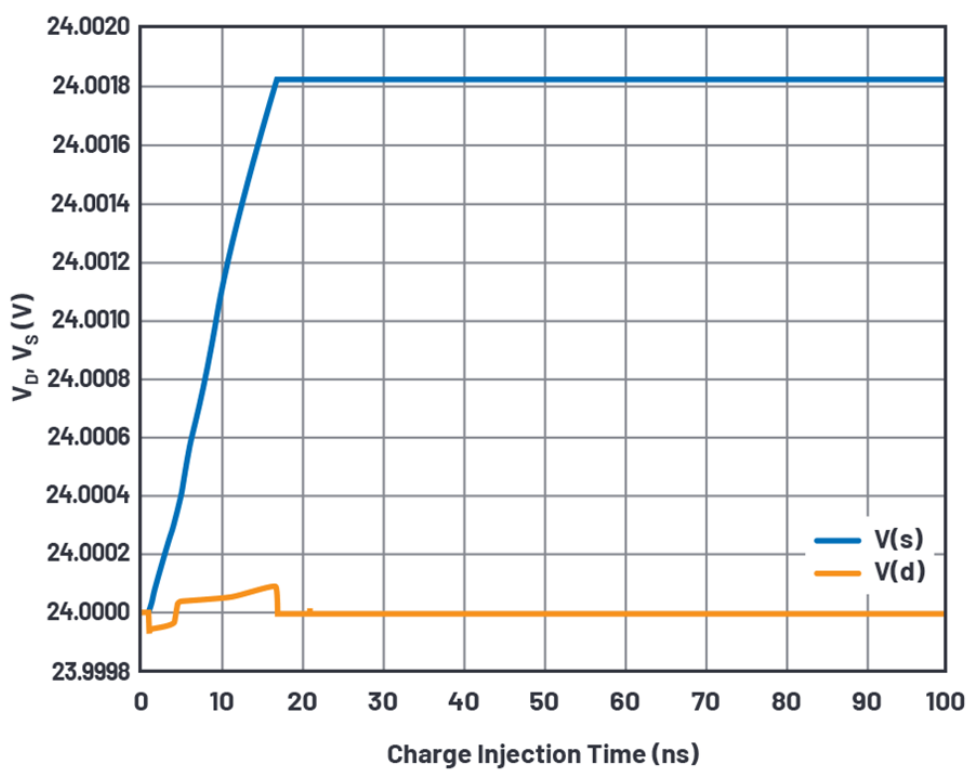

數據手冊電荷注入測試電路在開關的D端設置電壓源,在開關的S端設置電容Cl。開關晶體管關閉時,Cl被隔離,通過開關集成注入其中的電荷。在這種情況下,VD波形在電源為30V時保持在24V,如圖10所示。

圖10. 電荷注入仿真波形。

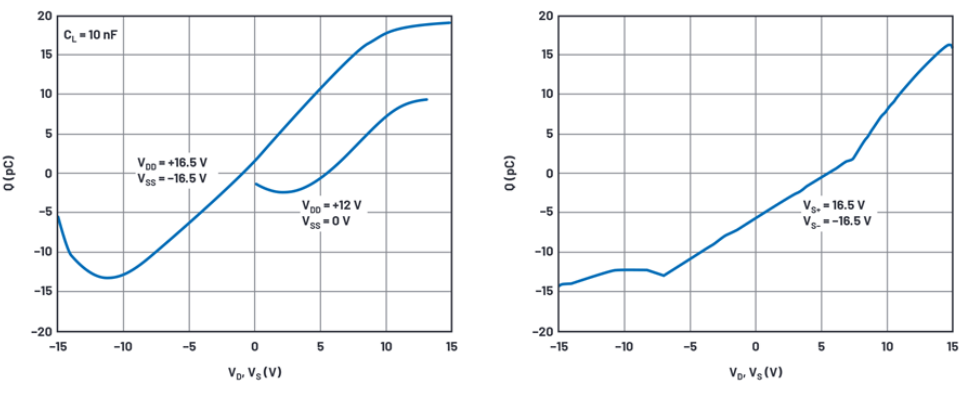

注入的電荷是V(S)和V(D)之間的電壓跳變乘以10nF保持電容。我們可以在電源電壓范圍內實施開關電壓VD階躍,并且使用.meas語句來捕捉各個電壓下的電荷注入值。圖11顯示了數據手冊曲線結果和仿真結果。

圖11. 電荷注入數據手冊和仿真波形。

我們簡單的MOS模型不能很好地模擬數據手冊曲線波形,但在數據手冊曲線中,峰值電荷注入值為32pC,在仿真中為31pC。讓人意外的是,這兩個值非常接近,如果有必要,我們可以調節TOX來完善仿真結果。

兩個曲線之間存在偏移,我們可以使用CCHARGE_INJECTION來進行補償。使用某些值調整后,我們選擇最優值CCHARGE_INJECTION=0.28pF。如果需要反向極性偏移, CCHARGE_INJECTION會重新連接至PMOS_on_when_low節點。

調節電容CCHARGE_INJECTION是一種使電荷注入與模擬電壓的關系仿真曲線偏移的簡便方法。如果仿真的峰值注入值太小,怎么辦?嗯,大部分電荷注入會產生開關的柵級電壓擺動,通過開關晶體管的柵級通道電容發送電荷。如果仿真的注入太少,我們可以直接增加一個或兩個柵級面積。為此,我們需要按同樣的系數提高開關器件的參數值L和W,且要保證不改變設置導通電阻的W/L比。相比使用CCHARGE_INJECTION,我們會選擇增加NMOS W和L。

或者,我們可以調節每個器件的TOX,以獲得更好的電荷注入關聯結果。這實際上不可行,但是,我們這只是仿真。在我們使用的簡單模型中,TOX不會影響到其他仿真參數。

在已經設置參數,以獲得出色的RON和電荷注入仿真結果的情況下,我們現在可以仿真S和D端電容。

重要的一點是,高壓MOS開關的漏極和源極區都必須具有偏移區。對于開關,您無法區分源極和漏極之間的功能差異,但是漏極和源極的體電勢都需要用到各自的偏移區。對于中等電壓 軟擴散,這也是正確的,但在低壓MOS中,這不合理。我們已將漏極和源極中存在的偏移區電阻匯總到RD,在飽和情況下,這對開關有效,對晶體管則無效。

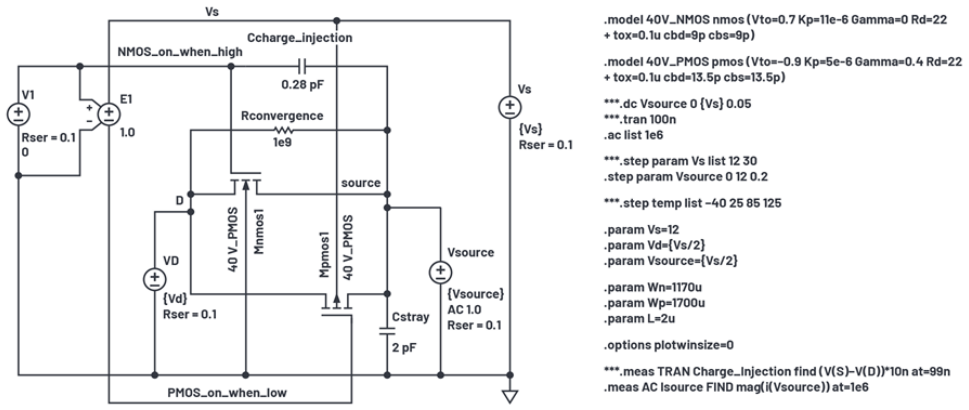

圖12顯示了仿真設置。

在LTspice中,您可以按一種頻率運行.ac(使用.ac中列出的選項),但也只能提供一種頻率參數(此情況下為1MHz)。然后,在整個電源范圍內運行.step VSOURCEdc電壓,以獲取電容與電壓范圍的關系曲線。

關閉的開關器件的D端保持中等電壓。S端(此處對源極重命名以防與VS混淆)由直流值范圍在0V至VS內、交流驅動電壓為1V的電壓源驅動。電容計算公式為I(VSOURCE)/(2×π×1MHz×1V)。邏輯驅動V1變更為0V,以關閉晶體管。

在模型說明中,漏極電容和源極電容分別為CBD和CBS。模型中包含內置默認集中度、內置電壓和指數,使CBD和CBS電壓可變。因 為它們是對稱的,所以漏極和源極電容可能相等。此外,由于PMOS的寬度與NMOS不同,CBD,NMOS/CBD,PMOS=CBS,NMOS/CBS,PMOS≡WN/WP的比率會在導通電阻模型中確定。圖13顯示了仿真結果。

圖13. VS = 12 V(左側)和30 V(右側)下的關閉電容和直流電壓關系曲線。

顯示的結果是I(VSOURCE)/(2×π×1MHz), 這表示電容。LTspice不知道這 個值的含義,因而顯示pA而不是pF。

遺憾的是,我們沒有數據手冊曲線來進行比較。從數據手冊的規格表中可以看出,電容(可能是在中等電壓下,數據手冊中沒有指明)在30V電源電壓下一般為7pF,在12V電源電壓下為12pF。我通過調節CB, 獲取30V電壓下的7pF曲線,但在12V電壓下只能仿真10pF曲線。調節內部電勢和電容公式指數后,使用的模型便無法再改善12V/30V符合性。

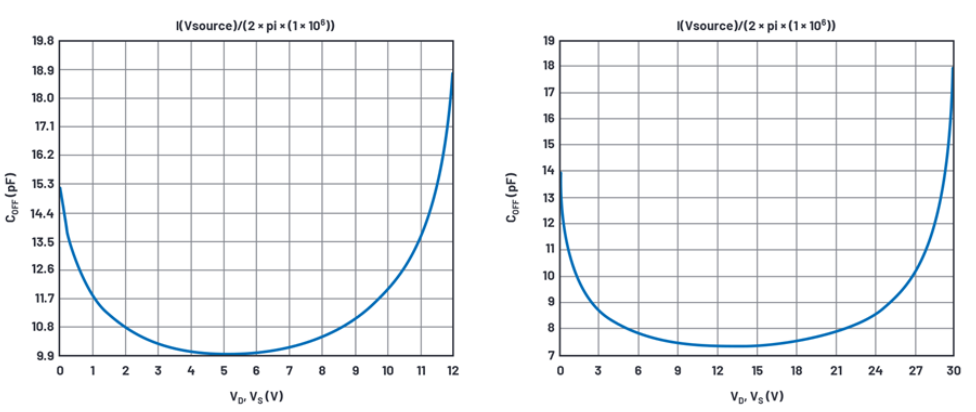

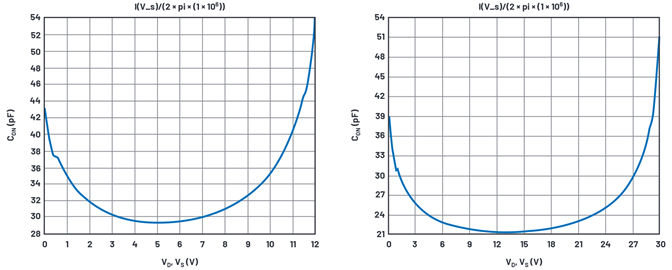

圖14顯示了開啟狀態的電容仿真設置。

圖14. 開啟狀態的電容測試仿真設置。

從中可以看出,完整的單刀雙擲開關的右側開關已經開啟,左側開關關閉,并連接至Vs/2源。左側開關的右半部電容和右側開關的總電容,以及D和S端存在的寄生電容并聯,由V_s源的1MHz測試信號驅動,后者的直流電平從接地階躍至Vs。圖15顯示了其仿真結果。

圖15.VS=12 V(左側)和30V(右側)下的開啟電容和直流電壓關系曲線。

仿真得出的值是29.5pF和21.4pF,數據手冊給出的值是26pF和25pF。考慮到電路板布局電容的變化,我們認為這些值已經非常接近。

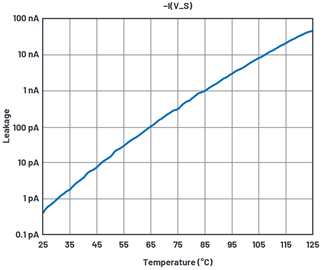

數據手冊曲線顯示25°C時與電壓相關的pA級漏電流,但數據手冊規格只能保證幾百pA。我受25°C下曲線結果的影響更大。對于此器件,沒有正確把握小漏電流的重要性,所以無法保證測試結果。客觀地說,測量一個pA級漏電流需要大量的設計開發工作和較長測試時間。

在85°C下,可保證測出幾nA(可以有效測量),典型值則在幾百pA范圍內。我認為這些典型值相當準確。

漏電流屬于產品缺陷;不存在嚴格的統計數據,且隨溫度變化很大。這不是我們設計要達到的規格,相反,這個數值會干擾與之連接的電路。在宏模型中使用時,適當幅度的泄漏會仿真 為電路缺陷,對于設計人員來說,是不錯的警示。在85°C下,我為開啟狀態開關選擇1nA目標測試值。

我們的模型顯示沒有超過RCONVERGENCE和GMIN電流的漏電流。GMIN是仿真器置于結之間,用于協助收斂的電阻。其電導系數通常為1×10–12但在電源電壓為30V時,得出的值可能是30pA電流的幾倍,遠高于測試需求。在仿真的一系列選項中GMIN會降低至1×10–15,RCONVERGENCE上升至1×1015。

這些泄漏大部分可能實際來源于連接至每個引腳的靜電放電(ESD)保護二極管。我們會將這一點納入圖16的仿真設置中。

圖16. 泄漏測試仿真設置。

調節了二極管模型中的ls后,我們獲得了泄漏電流與溫度關系曲線,如圖17所示。

圖17. 溫度范圍內泄漏測試仿真結果。

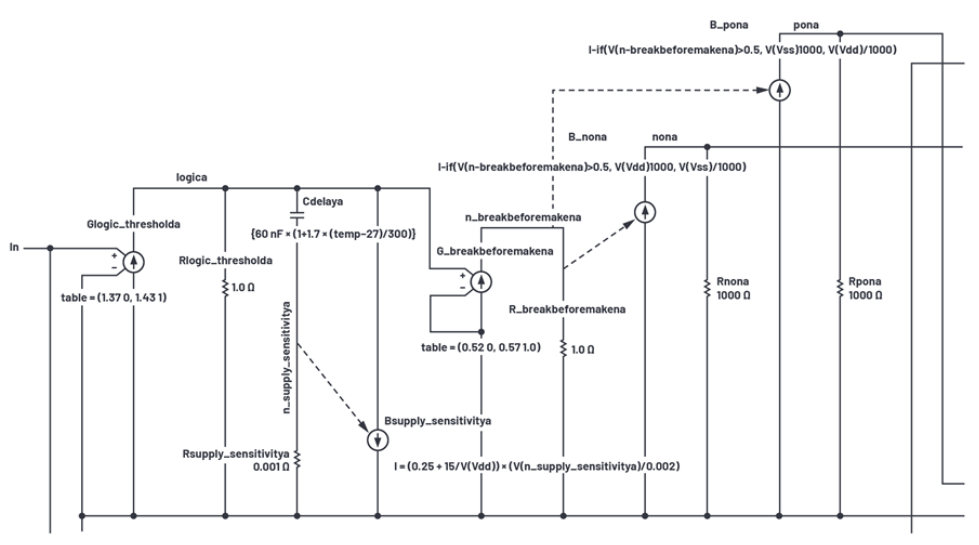

單純的行為邏輯-柵級驅動電路如圖18所示。

圖18. 行為邏輯-柵級接口。

外部邏輯輸入位于圖18左側的輸入端。它是理想跨導Glogic_thresholda的輸入,具有分段線性傳輸函數。對于低于1.37V的邏輯輸入,邏輯節點下的輸出為0V;對于高于1.43V的輸入,邏輯輸出為1V;在1.37V和1.43V之間時,邏輯輸出呈線性從0V過渡到1V。Glogic_thresholda因此會忽略電源差異,提供1.4V輸入閾值。

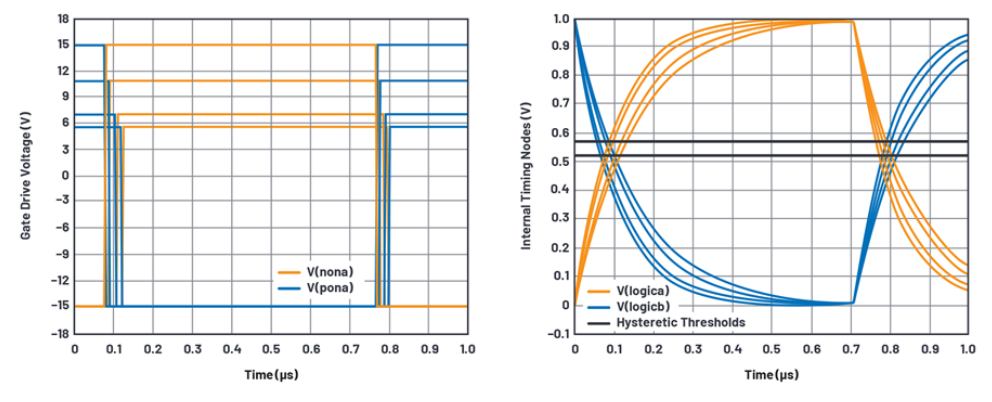

Cdelaya會在瞬間減慢邏輯節點的速度,所以我們能從中截取一些時間點。為了制作比較器,我們再次使用跨導,此時Gbreakbeforemakena的輸出再次從0V過渡到1V,但是閾值的擺幅略高于0.5V。從圖19中可以看出,

圖19. 先開后合式時序。

傾斜的動作電壓為0.52V和0.57V,而不是0.5V,這使得從1V下降的指數信號的關斷速度比從0V上升的指數信號的關斷速度更快。

全柵級驅動電壓由B_non和B_pon行為電流源產生。當節點n_breakbeforemakena>0.5V時,B_nona產生VDD/1000電流,節點nona的電壓在加載1000Ω電阻時達到VDD。當節點n_breakbeforemakena<0.5V時,節點nona被驅動至Vss。所以,我們有不錯的電軌-電軌柵級驅動器,符合電源電壓要求,并且具有1.4V固定輸入閾值。

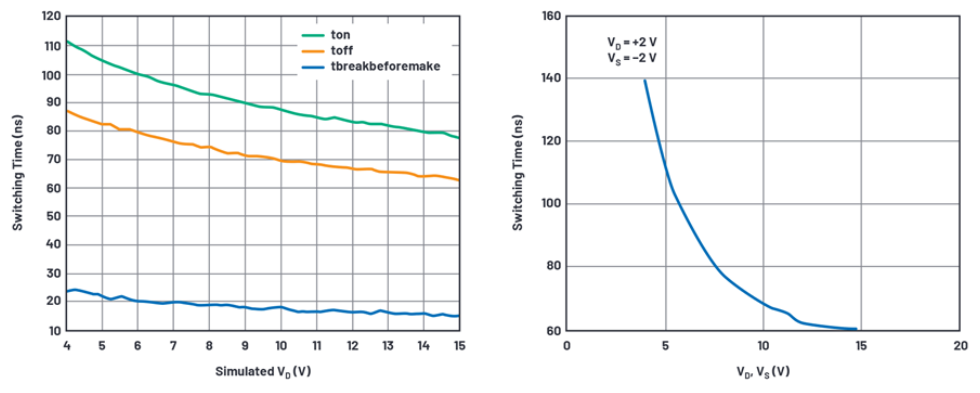

我們還需要說明另一個特性。請注意,在圖20中,更高的電源電壓會縮短延遲時間。這通過B_supplysensitivitya來實現,它向Cdelaya返回自身隨VDD變化的少量動態電流。Rsupply_sensitivitya因為Cdelaya電流會出現少量壓降,使得Cdelaya很大程度上作為純電容使用。將Cdelaya電流的副本返回給Cdelaya實際上會創建一個可控 的可變電容器,Bsupply_sensitivitya內部的數學運算實際上會產生圖20所示的延遲與VDD關系曲線。

圖20. 仿真和數據手冊曲線的先開后合式時序結果。

我們的電路在VDD=4V時,仿真得出的TON延遲為111ns,數據手冊曲線顯示的延遲為140nsVDD=15Vs時,仿真延遲為77ns,數據手冊中的延遲為60ns。并無太大關聯;我會留給讀者來完善Bsupply_sensitivity函數,以實現更好的結果。至少,先開后合式時序的差異在15ns和24ns之間會更好。

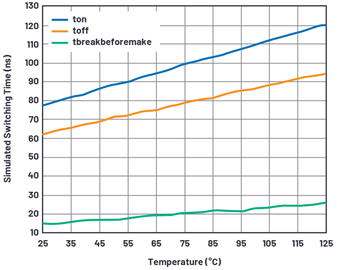

雖然,數據手冊沒有給出太多關于延遲和溫度關系數據,但是我在Cdelaya中增加了溫度項,至少在高溫條件下,模型仿真速度會減慢,如圖21所示。

圖21. 時序延遲與溫度的關系。

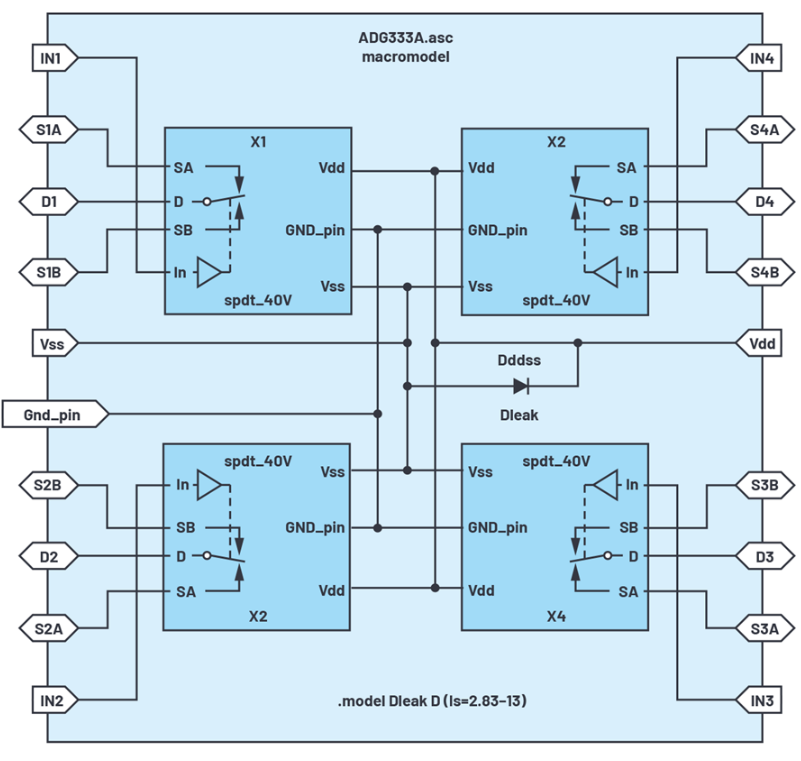

圖22顯示了會成為分支電路的組合模擬開關。在晶體管符號位置為L和W硬度值,而不是參數,并移除了所有激勵和I/O,以便連接引腳SA、D、SB、In、 VDD, Vss和Gnd_pin。

圖22. 組合SPDT分支電路spdt 40V.asc。

還提供了第二個邏輯接口,用于單刀雙擲對的另一個開關。ESD保護二極管置于模擬端口和Vss之間,以及邏輯輸入端和地之間。注意,上部邏輯接口器件和節點名稱中的“-a”后綴在下部接口中用“-b”后綴代替。Glogic_thresholdb接口的輸出與Glogic_thresholda表中的輸出反向,使得一個或另一個開關對能夠運行,而不是同時開啟。

備用ESD保護方案包含受保護的引腳到VDD和Vss的二極管,以及VDD和Vss之間的箝位。數據手冊通常提供保護方案說明,漏電流則 被分配到兩個電源。

在圖23所示的ADG333A.asc主示意圖中,給出了單刀雙擲分支電路的符號并用了四次。

圖23. ADG333A宏模型電路示意圖。

圖24顯示測試結構的示意圖,用于驗證最終的宏模型結果。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀: