- D 類音頻功放的系統設計

- D 類音頻功放單元電路設計實現

- D 類音頻功放單元電路設計

D 類音頻功放具有高效、節能、小型化的優點,廣泛應用于便攜式產品、家庭AV 設備及汽車音響等多個領域。本文設計的D 類音頻功率放大器主要基于以下三個方面考慮:保證高保真度、提高效率和減小體積。文章設計了一款工作于5V 電源電壓并采用PWM 來實現的D 類音頻功率放大器,整個系統包含了輸入放大級、誤差放大器、比較器、內部振蕩電路、驅動電路、全橋開關電路及基準電路。通過引入反饋技術來減小系統的THD 指數,采用雙路反寬調制方案不僅抑制了D 類音頻功率放大器的靜態功耗,而且達到了去除D 類音頻功率放大器輸出端低通濾波器的目的,減小了系統的體積。

1 D 類音頻功放的系統設計

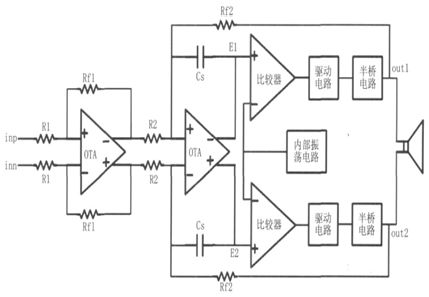

本文所設計的D 類音頻功率放大器的系統結構如圖1 所示。該放大器結構是基于雙邊自然采樣技術方案實現的,在任一時刻輸出所包含的信息量都是單邊采樣方案的兩倍,通過雙邊自然采樣還可以把輸出音頻信號中大量的失真成分移除到人耳所能感應到的音頻帶寬范圍之外,達到去除D 類音頻功率放大器輸出端低通濾波器的目的。

圖1 D 類音頻功率放大器結構

在圖1 中,對電容Cs 充放電的電流I1、I2 由Vout1、Vout2、Vin、R1、Rf1、R2 和Rf2 共同決定,其中電阻和電容必須具有良好的線性度和匹配性,以獲得良好的閉環性能。

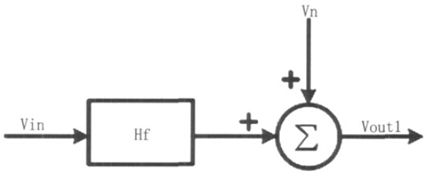

開環D 類音頻功率放大器的模型如圖2 所示。

圖2 開環D 類音頻功率放大器模型

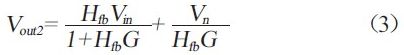

此時系統輸出為:

開環系統的總諧波失真為:

式(2)中的Vin 為放大器的輸入信號,Vn 為引入的諧波失真,Hf 為傳遞函數。

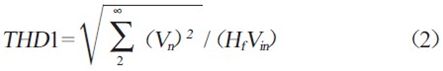

具有反饋環路的D 類音頻功率放大器的模型如圖3 所示。

圖3 閉環D 類音頻功率放大器模型

其中Hfb 為閉環模型的傳遞函數,G 為反饋增益。為了得到相等的放大倍數,設計傳遞函數為:

則式(3)變為:

閉壞系統的總諧波失真為:

比較式(2)和式(6)可以看出,具有反饋環路閉環系統THD 為開環系統THD 的1/(1+HfbG),即通過反饋結構減小了系統的THD。

2 單元電路設計實現

系統單元電路主要包括:輸入放大級、誤差放大器、比較器、驅動電路、全橋開關電路、內部振蕩電路和基準電路。

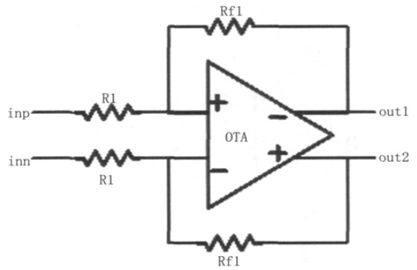

2.1 輸入放大級

D 類音頻功率放大器的輸入放大級是基于運算放大器(OTA)的閉環結構來實現的,其結構如圖4所示,用來根據需要對輸入的音頻信號作電平調整和信號放大處理,使輸入信號在幅度方面能滿足后級電路的要求,輸入放大級的增益可以通過設置Rf1和R1 的阻值來決定。

圖4 輸入放大級電路結構

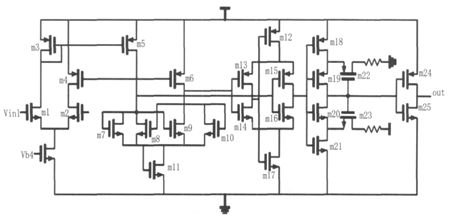

2.2 比較器

本文所采用的比較器電路如圖5 所示,比較器電路由三級構成,即輸入預放大級、判斷級(或正反饋級)和輸出數字整形緩沖級。預放大級采用有源負載的差分放大器來實現,其放大倍數不用很大,用來進行輸入信號的放大,以提高比較器的敏感度,并把比較器的輸入信號與來自正反饋級的開關噪聲隔離開;判斷級用來將預放大級的信號進一步放大,為比較器的核心部分,電路中通過把m8 與m9 的柵極交叉互連實現正反饋,以具備能夠分辨非常小的信號的能力,并提高此級電路的增益;輸出緩沖級是一個自偏置的差分放大器,它的輸入是一對差分信號,用來把判斷級的輸出信號轉化成邏輯電平(0V 或5V),即輸出高電平VOH=VDD,輸出低電平VOL=GND。

圖5 比較器電路圖

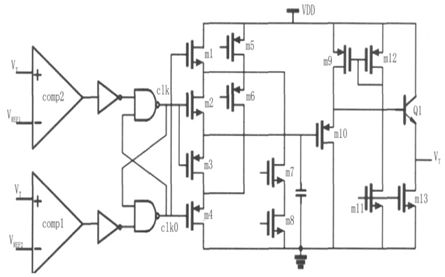

本文采用的三角波產生電路結構如圖6 所示,其中m5、m6 和m7、m8 構成了兩組恒流源,m9~m13 和Q1 構成了輸出級。在電路中,采用將輸出信號VT 分別反饋到比較器comp1 和comp2,與參考電平VREF1 和VREF2(VREF2<VREF1)進行比較,并通過一組數字電路產生兩路反向的時鐘信號clk 與clk0,來控制m2 和m3 的開啟和關斷,從而達到對電容C 進行充放電,產生三角波信號VT 的目的。

圖6 三角波產生電路

2.4 全橋開關電路

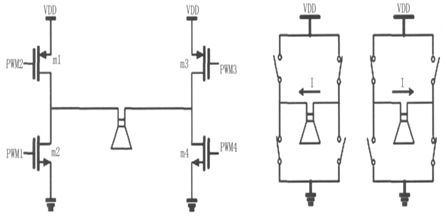

輸出級采用N、P 型功率開關對管組成的全橋開關電路實現,其結構及負載電流流向如圖7 所示。

圖7 全橋電路結構及負載電流示意圖

[page]

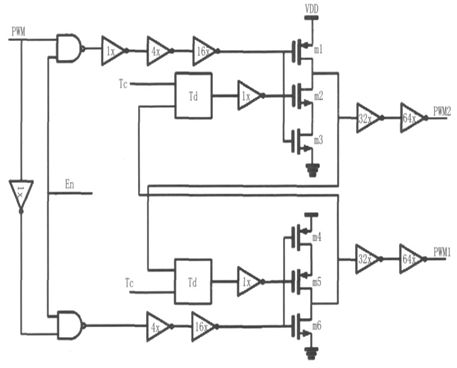

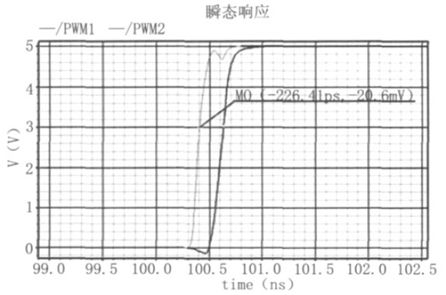

2.5 驅動電路

驅動電路結構如圖8 所示,該電路能有效調節死區時間(N 型、P 型功率開關管同時關斷),防止單臂"shoot- through"現象,并有保護關斷功能。輸入信號為比較器輸出的PWM 脈沖信號,PWM1用來驅動N 型功率開關管,PWM2 用來驅動P 型功率開關管。為了避免全橋開關電路中的單臂"shoot- through"現象,當PWM 信號從低電平變為高電平時,PWM2 應首先變為高電平, 關斷PMOS 功率開關管,隨后PWM1 再變為高電平,開啟NMOS 功率開關管,如圖9 所示;反之,當PWM 信號從高變為低時,PWM1 先變為低電平,關斷NMOS 開關功率管,隨后PWM2 再變為低電平,開啟PMOS 開關功率管。實際電路中,可以根據需要通過控制延遲單元的控制位Tc 來調整死區時間的長短。為減小失真,必須減小死區時間,該驅動電路采用了逐級增加驅動能力的方式來驅動功率管,從而減小了必要的死區時間,保證了低失真度。

圖8 驅動電路結構

圖9 死區時間

[page]

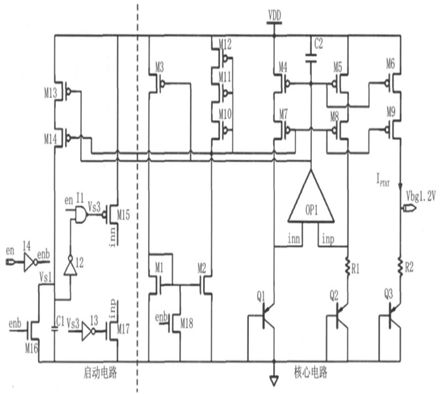

2.6 基準電路

本文所設計的帶隙電壓基準源結構如圖10 所示,主要由核心電路與啟動電路兩部分組成。

圖10 基準電路

電路上電時偏置電路可能會出現零電流的情況,需要啟動電路保證電路能夠正常工作。電路不工作時,EN、Vs1 為0,Vs2、Vs3 為1,M15、M17 不通,運放輸出為高,M3~M6 也不通,整個電路不消耗電流。當EN 由0 變成1 時,由于C1 的作用,Vs1 保持為0,Vs2 為1,Vs3 變為0,此時M15、M17 導通,inp、inn 分別被拉到0、1,運放輸出變為0,M3~M6 導通,M13、M14 支路開始有電流,并對C1 充電,直到Vs1 高過I2 閾值電壓時,Vs2 變為0,Vs3 則變為1,M15、M17 關斷。最終電路偏離零電流狀態,開始正常工作,且Vs1 充至電源電壓,整個啟動電路不再消耗電流。

3 結論

本文研究了基于PWM 調制技術D 類音頻功率放大器的工作原理,通過引入反饋技術減小了D 類音頻功率放大器的THD;通過逐級增加驅動能力的方式減小了必要的死區時間,保證了更低的失真度;采用雙路反寬調制方案,一方面抑制了系統的靜態功耗,另一方面去除了輸出級的LC低通濾波器,達到了減小系統成本和體積的目的。