【導讀】通過對被測信號的實時采樣,利用等效采樣原理,可以將采樣率為1MHz等效為200MHz,提高了被測信號的最高頻率,具有成本低,性能可靠,便易升級的特點。

項目背景及可行性分析

1.項目名稱、項目的主要內容及目前的進展情況

項目名稱: 基于FPGA的高速采樣顯示電路的實現

主要內容:通過對被測信號的實時采樣,利用等效采樣原理,可以將采樣率為1MHz等效為200MHz,提高了被測信號的最高頻率,具有成本低,性能可靠,便易升級的特點。

2.項目關鍵技術及創新點的論述

(1)200MHz脈沖產生電路

直接產生的方波信號,電路復雜,易受外界干擾,性能指標較差,制作難度較大。我們利用晶振產生20MHz方波信號,利用FPGA內部鎖相環電路將其倍頻到200MHz,電路簡單,可靠性高,性能指標好。

(2) 多周期測量技術

利用傳統的測周期方法,測量計數誤差為±1。我們利用增加被測信號周期整倍數來減少測量誤差,測量誤差為原來的1/10n 。

(3) 等效采樣算法

首先對輸入的模擬信號進行整形,在過零點處產生脈沖,利用相鄰兩個過零點脈沖對周期為5ns的周期序列進行計數(計數值為N),由此可產生對被測信號周期的測量,測量誤差不大于5ns。利用等效采樣原理,(T采樣=mT信號+△t), △t=1/200MHZ=5ns, 由于最高實時采樣率為信號最高頻率的十分之一,應取m>=10,故等效采樣周期=10*N△t+△t從而完成200mSaPS的等效速率。

3.顯示技術

根據液晶顯示原理,液晶屏上的每一個點對應著顯示緩沖存儲器的一個bit,通過一定的算法,將顯示緩存的某一bit 置1,就可將被測信號顯示出來。

4.控制模式選擇

控制電路可采用中大規模的集成電路來構成,但結構復雜,移置性差,在此我們選擇VHDL語言,通過編程,完成整個電路的控制。

項目實施方案

1.方案基本功能框圖及描述

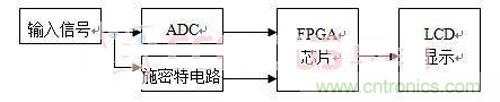

方案基本功能框圖如圖1所示。

圖1.方案基本功能框圖

將輸入的模擬信號分成2路,一路經ADC輸入FPGA 芯片 ,另一路經斯密特電路輸入給FPGA 。FPGA外接20MHz的晶振,通過FPGA 內部的鎖相環倍頻至200MHz,即周期為5ns的方波信號。用此方波信號作為時間基準,對經斯密特電路輸入信號的周期進行測量,得到被測信號周期=N*5ns,則等效采樣的時間間隔=m*(N*5ns)+5ns。根據等效采樣原理,此時的采樣率相當于1/5ns=200MHz,利用LCD顯示技術,可以看到此效果。

2.需要的開發平臺

接口:信號輸入的同軸電纜接口。

輸出:FPGA開發芯片的輸入輸出引腳(至少10根引線)。

所需要的目標FPGA開發平臺:ISE 9.0

3.方案實施過程中需要開發的模塊

在本方案中需要研制模數轉換模塊和LCD顯示接口模塊。若選用初級板Spartan-3E,則無須制作模數轉換模塊。否則,自行開發這些模塊。

4.系統最終要達到的性能指標

等效采樣速率要達到200MHz。利用等效采樣原理,(T采樣=mT信號+△t), △t=1/200MHz=5ns, 若被測信號的最高頻率為10MHz,應取m>=10,故等效采樣周期=10*N△t+△t,從而完成200MSaPS的等效速率。

需要的其它資源

1.設計輸入輸出功能子板

(1)ADC板。將模擬信號通過8位或12位模數轉換器轉換成數字信號,輸入信號幅度1V,最好截止頻率10MHz ,采樣頻率為1MHz,輸出數字信號高電平為3.3V。自行研發。

(2)LCD

規格: 320x240。購買成品。

穩壓電源,液晶顯示屏。

方針、開發工具

ISE9.0綜合開發環境。