【導讀】隨著DSP處理器在現代工業的應用越來越廣泛,DSP的功能不僅只有快速運算處理,還需要與其他處理器或者設備之間進行實時數據交換,以實現資源的共享。因此,針對不同設備的需求,選擇穩定、快速和高效率的接口方式在當今數字信號處理系統設計中關鍵的組成部分。

DSP的應用

針對8核DSP TMS320C6678與外部設備進行數據通信的需求,以片上集成千兆以太網交換子系統為核心,選取芯片88E1111作為PHY設備,設計了千兆以太網通信接口的硬件電路。在嵌入式操作系統SYS/BIOS和網絡開發環境NDK上,完成了以太網底層驅動和TCP/IP協議的程序設計。通過DSP與上位機進行以太網通信測試,證明了以太網接口電路硬件及軟件的正確性和實用性。

隨著DSP處理器在現代工業的應用越來越廣泛,DSP的功能不僅只有快速運算處理,還需要與其他處理器或者設備之間進行實時數據交換,以實現資源的共享。因此,針對不同設備的需求,選擇穩定、快速和高效率的接口方式在當今數字信號處理系統設計中關鍵的組成部分。

TI公司的8核處理器TMS320C6678(以下簡稱C6678)提供豐富的片上接口資源用于處理器與外設之間的通信,這些接口都可以用于DSP與外設之間的通信,但是靈活性有差異,使用SGMII接口來實現千兆以太網通信,可使得通信接口一般化,能夠適用于眾多的設備連接。本文針對C6678的芯片特點以及含有的接口資源,設計實現了千兆以太網通信,主要設計了以太網接口電路、網絡底層硬件驅動、TCP/IP協議的用戶程序,并完成了與上位機以太網通信測試,實現了數字信號高速有效地網絡傳輸。

1.C6678以太網交換子系統

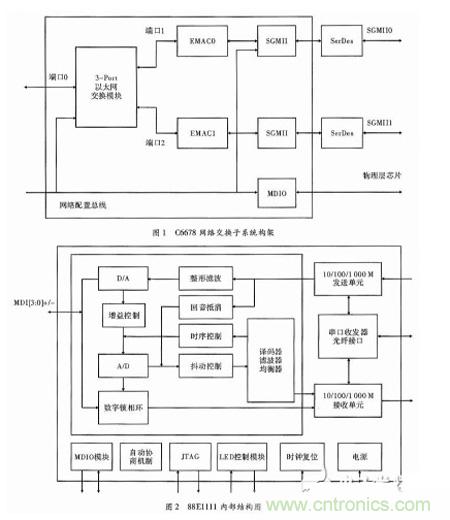

C6678是基于KeyStone I構架的8核高性能、定點/浮點處理器,單核最高工作頻率可達1.25 GHz。C6678的以太網交換子系統包括2個以太網媒體訪問控制(Ethernet Media Access Controller,EMAC)、2個SGMII、1個管理數據輸入輸出(Management Data Input Output,MDIO)、3-Port以太網交換模塊以及網絡配置總線,其網絡交換子系統如圖1所示。

EMAC的作用是將交換子系統的內部信號轉換為GMII信號傳遞給SGMII模塊;MDIO控制物理層芯片執行對多數據流的控制輸入輸出。

2.PHY芯片88E1111

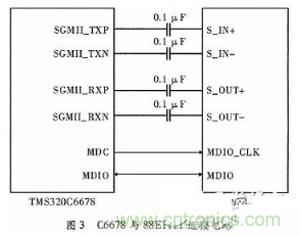

本文選擇C6678作為主芯片,由于C6678的千兆網絡交換子系統只支持SGMII接口,所以本文選擇對SGMII接口的網絡數據傳輸具有較好兼容性的物理芯片88E1111。88E1111芯片的內部結構如圖2所示。

88E1111的介質接口有銅介質接口和光纖接口。銅介質接口為MDI[3:0],通過設置HWCFG_MODE[3:0]來選擇運行模式。 88E1111集成的MDIO模塊與EMAC的MDIO接口相連接,可將方便網絡控制端讀取物理芯片狀態寄存器,達到實時監測的效果。

3.硬件接口設計

本文設計的任務是基于C6678片內以太網交換子系統和片外PHY芯片88E1111及其外圍電路的接口設計。主要包括:C6678與88E1111芯片連接、88E1111芯片配置以及88E1111芯片與網絡介質連接。

3.1 C6678與88E1111芯片連接

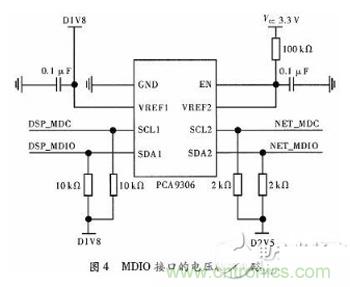

C6678和PHY芯片88E1111的接口電路如圖3所示。88E1111工作在SGMII接口模式下,不需要TXCLK時鐘輸入,更有助于減少電路板上走線的數量,同時也可減少噪聲的產生。

主要的接口信號包括時鐘和數據信號如下:

MDIO_CLK:管理數據時鐘。該時鐘信號由C6678片上的MDIO模塊提供,該時鐘頻率通過配置MDIO的控制寄存器CONTROL中的CLKDIV位來控制實現。

SGMII_TXP和SGMII_TXN:串行發送差分數據線。連接DSP內部SerDes和物理芯片的S_IN管腳,DSP的SerDes通過該管腳向物理層發送串行數據,數據中包含發送數據時鐘信號。

SGMII_RXP和SGMII_RXN:串行接收差分數據線。連接DSP內部SerDes和物理芯片的S_OUT管腳,物理層芯片通過該接口將數據傳送到DSP的SerDes,數據中包含數據接收時鐘信號。

MDIO:管理數據I/O。可最多連接32個PHY設備到DSP的EMAC,并且可以枚舉所有PHY設備,讀取PHY設備狀態寄存器來監測PHY的連接狀態。數據幀結構符合802.3標準,包含讀寫指令、PHY地址、寄存器地址和數據等。

因為88E1111上集成的MDIO與C6678集成MDIO模塊進行連接時,電壓有所差別,前者電壓為2.5 V,后者電壓為1.8 V,所以在二者之間應該添加電壓轉換器。本文采用一片PCA9306,實現2.5 V和1.8 V之間的電平轉換,其連接電路如圖4所示。

3.2 88E1111芯片配置

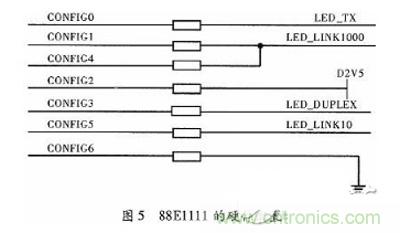

88E1111與C6678的MDIO模塊相連接,MDIO最多可識別32個物理芯片,在使用物理芯片之前需要對其進行配置,配置內容主要包括芯片的地址、模式等。配置CONFTG[6:0]管腳定義可查詢文獻,本文配置的硬件電路如圖5所示,圖5中可以不使用電阻,本文為了測試方便,加一個0 Ω的電阻。

88E1111硬件配置完成后,系統將固定為一種接口方式,按照文獻的定義,物理芯片的地址為:PHY_ADDRESS=0’b00001,芯片模式為:不帶時鐘,自動協商的SGMII模式。

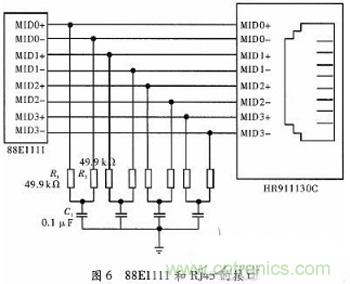

3.3 88E1111芯片與RJ45連接

88E1111和網絡介質之間無法直接連接,因傳輸速度在千兆級,所以更加需要設計合適的網絡隔離變壓器來降低傳輸損耗、回音和串擾。本文選擇千兆網口插座HR911130C,該插座內部自帶變壓器電路,只需在外部連接濾波網絡便可實現網絡信號穩定地傳輸,如圖6所示。88E1111和 HR9111130C采用差分連接,在PCB布線時需要嚴格等長,且一般還需使用阻抗匹配網絡,如圖6中的R1和C1。

4.軟件程序設計

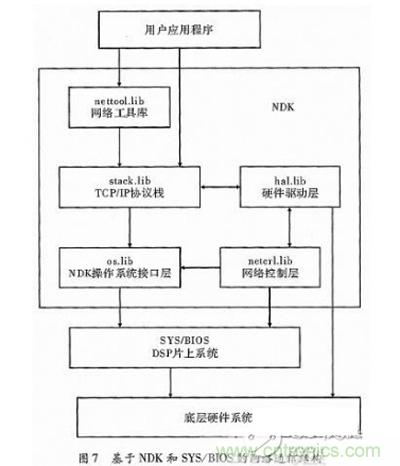

TI針對網絡開發發布了網絡開發套件(Network Development Kit,NDK),能將多個模塊的配置操作交給NDK網絡框架實現,同時數據分包和解析也無需程序員過多考慮,加速了網絡開發進程。NDK構建在實時操作系統SYS/BIOS之上,NDK通過OS抽象層與BIOS進行交互,同時BIOS的cfg配置文件能對NDK各模塊進行可視化查看。

本文基于多核DSP實時操作系統SYS/BIOS上,設計了以太網通信程序。該操作系統能夠提供較多的集成模塊,方便用戶編寫程序,且還有軟硬件中斷管理、多任務同步機制、多核通信機制和存儲器管理機制等,可為用戶進行多線程多任務開發提供模塊化的框架。以太網通信接口的軟件總體結構如圖7所示。

SYS/BIOS為整個軟件提供集成開發環境,不僅擁有適合實時系統的多線程優先搶占機制,還可添加需要的封裝庫,使得編寫程序時可以更加方便地調用庫函數。NDK是DSP的網絡程序開發集成工具,其中,stack.lib給出了從頂層socket到底層PPP關于TCP/IP協議棧的封裝庫;nettool.lib提供用于socket網絡套接字和用于網絡應用開發工具的封裝庫;os.lib提供應用于SYS/BIOS和網絡編程套件之間的系統協調的封裝庫;hal.lib提供外圍設備和網協議棧之間接口的封裝庫;netctrl.lib提供DSP網絡編程的整體控制,可用來配置底層驅動和協議。

本文DSP片上系統軟件分為3部分:SYS/BIOS平臺和NDK的TCP/IP協議棧建立和配置;用戶程序;編制底層驅動程序。

4.1 底層硬件驅動的實現

NDK的基本結構如圖7所示,可看出NDK開發套件與用戶程序、SYS/BIOS操作系統和底層硬件都有密切的聯系。NDK中網絡控制層和操作系統接口層與SYS/BIOS系統相連接,NDK的硬件驅動層用于控制底層硬件驅動的配置,這些操作和配置均可在網絡工具庫中找到相應的驅動函數,并可直接由用戶應用程序來調用實現。

這些功能主要包括:

(1)底層硬件驅動包括:MDIO模塊和EMAC模塊的初始化;PHY芯片搜索配置和狀態監測;EMAC/MDIO中斷使能。(2)TCP/IP協議棧的建立,配置接收和發送緩存區的大小,完成以太網數據的收發任務。(3)利用MDIO模塊,根據MDIO讀取的PHY狀態寄存器來監測其連接狀態,識別可以是CPU產生中斷的狀態變化事件,并將信息反饋。(4)關閉驅動,復位前面對寄存器進行的操作,收回占用資源。

如圖7所示,硬件驅動包含在硬件驅動層hal.lib中,用戶需要對按照系統對驅動函數進行修改。C6000系列NDK的API封裝了許多固定的驅動函數,具有特定的功能,比如_llPacketSerivceCheck()的作用是檢測以太網數據包的結構,且將檢測到的結構信息反饋給協議棧進行分析處理。具體的驅動程序需要按照硬件系統的配置來進行設計,在C6678中,可在集成度較高的片上系統直接對網絡通信模塊的寄存器進行配置查詢,就可以完成硬件底層驅動,使得底層硬件能夠有效地運行。

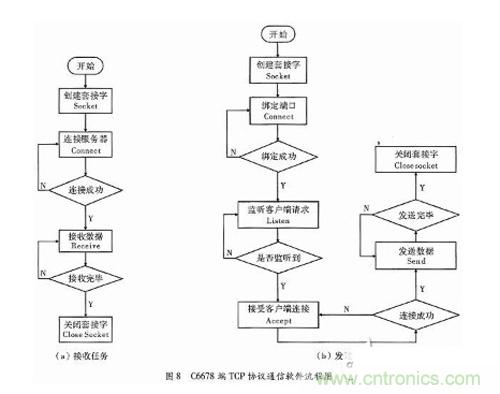

4.2 DSP端網絡應用程序

DSP軟件設計是基于SYS/BIOS實時多任務操作系統和C語言,采用Socket套接字,創建TCP/IP客戶端(Client)和服務器端 (Server),Client負責與外部設備服務器端建立連接并接收數據包,Server用來向PC機發送處理后的數據包。接收任務和發送任務流程如圖 8所示。在C6678的內核Core0中建立兩個同步線程任務,即數據接收和發送任務,分別用來接收TCP服務器發送過來的數據和發送處理后的數據到PC 上位機中進行處理、存儲和顯示。

4.3 上位機測試程序

上位機測試程基于VC++的MFC界面設計,使用套接字Socket進行網絡編程。程序中需設計兩個同步線程,用來實現數據的實時接收和動態顯示功能。使用TCP服務器端發送船體結構應力數據,經過DSP的接接收、處理和發送過程,最后發送到PC上位機進行數據動態顯示,結果如圖9所示。

5.結論

本文以8核處理器C6678為核心,對片上集成的以太網交換子系統接口硬件進行了研究,按照接口的特點設計了包括以太網交換子系統和物理芯片的接口連接、物理芯片與網絡介質接口連接的硬件系統,并完成了千兆以太網驅動,最終實現多核DSP C6678與上位機進行千兆以太網通信。通過與上位機進行網絡通信測試,結果顯示以太網數據通信接口能實時高效地進行網絡數據傳輸。