【導讀】在尋找EMC相關資料時發現某國外emc大神寫的關于ESD的測試報告,該報告對pcb layout非常有參考價值,從實際測試出發,由表象反應理論,因此將該英文測試報告翻譯并提煉出來呈現給大家,希望此文章對各位硬件工程師有所幫助。

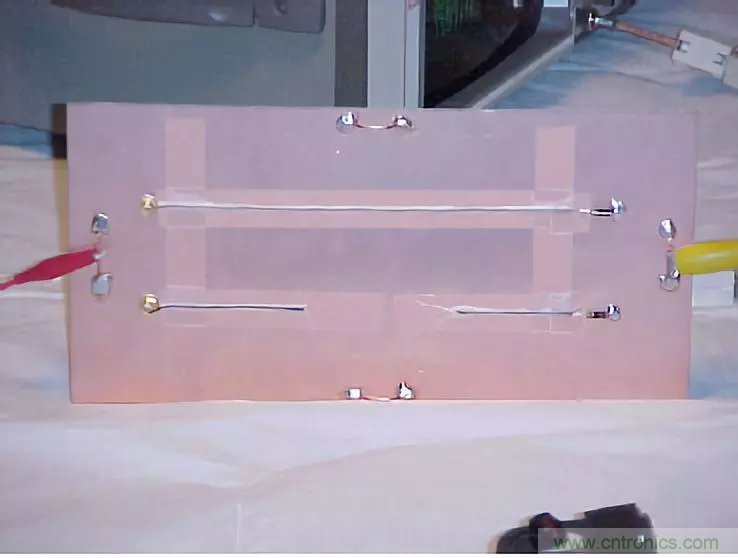

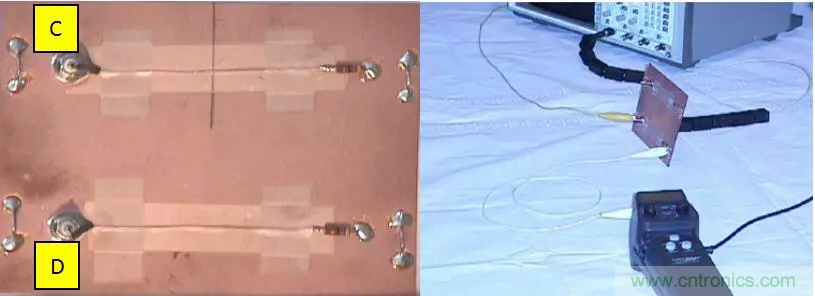

在普通的雙面板子上,焊有兩條導電測試路徑(如圖1),導線A,線路連續,且正下方貼有30cm銅箔。導線B,有1/3段線路走底層,且正下方貼的銅箔不連續。

圖1

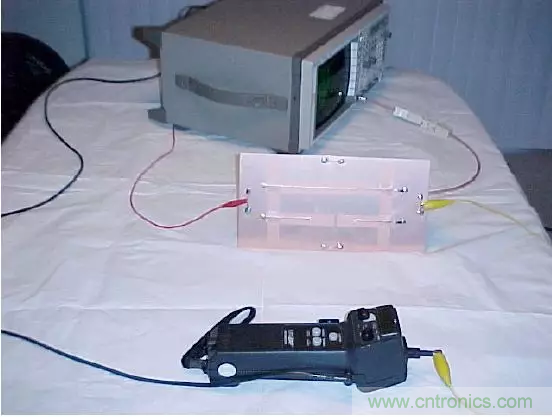

測試板右端為3kv ESD靜電施加放電點(端接47ohm負載阻抗),左端SMA接口與示波器連接,測試布置如圖2。

圖2

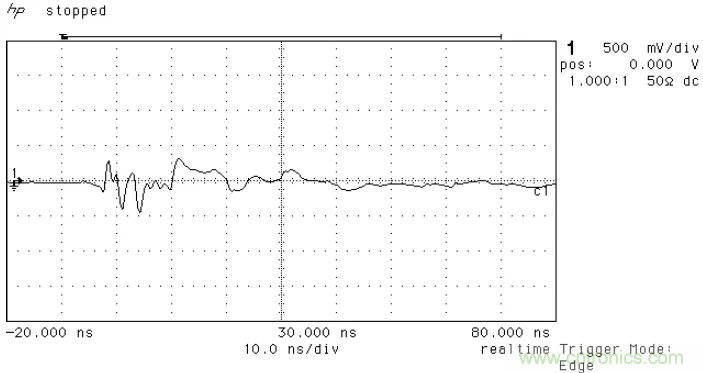

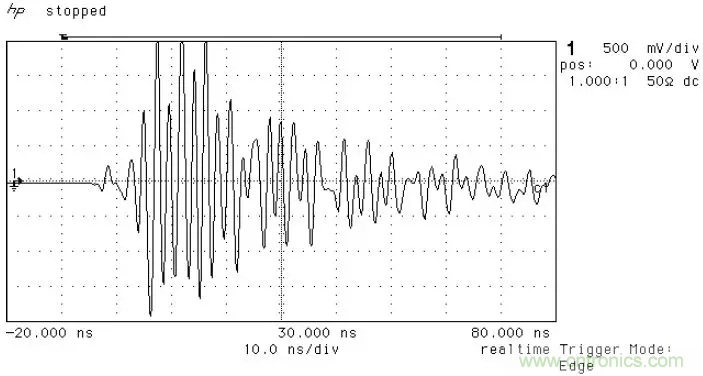

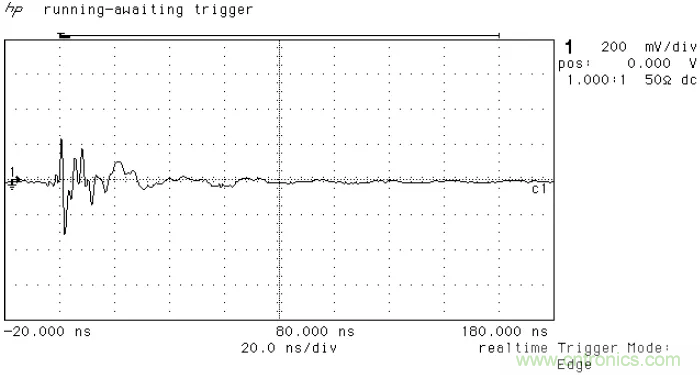

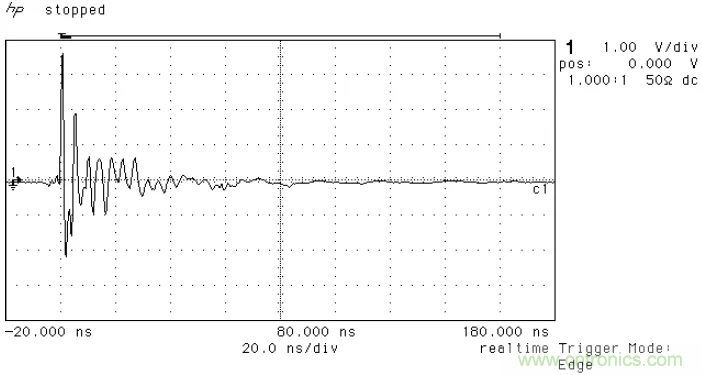

測試結果如圖3,圖4。

圖3

圖4

從圖3和圖4能看出,導線A在負載端接收到的ESD雜訊振幅,比導線B接收到的小很多。

繼續做另一個實驗,同樣是兩條導線,導線C線路連續且下方鋪設銅箔,但在線路下方用刀割出一道劃痕(“地”被割開),導線D線路連續,且下方鋪設銅箔完整。測試布置如圖5。

圖5

相同的測試布置,對兩條導線施加3KV ESD電壓。測試結果如下圖(圖6,圖7)。

圖6

圖7

從圖6和圖7看出,地不連續的路徑,其ESD所產生的噪聲會引發更嚴重的效應。

總結

當系統信號線遭受到ESD噪聲干擾時,必然會產生干擾信號的回流路徑,大部分情況此回流路徑會走低阻抗的參考地,且緊貼著信號線回到源端(最小環路面積)。當地被隔開后,原ESD噪聲的回流路阻抗增大,為了繞開割地凹槽,回流路徑將會改變,回流面積也會增大,根據天線效應,此時ESD回路上感應到的噪聲也會相應的增加,因此大部分情況下PCB割地將會導致ESD測試的惡化。