【導讀】每個人都知道運放應該使用靠近運放供電管腳的去耦電容,但為什么要使用這個去耦電容呢?例如,如果沒有合適的去耦,運放會更容易產生振蕩。了解使用去耦電容的原因,能夠增加對這個問題的理解和認知。

每個人都知道運放應該使用靠近運放供電管腳的去耦電容,對嗎?但為什么要使用這個去耦電容呢?舉個例子,如果沒有合適的去耦,運放會更容易產生振蕩。了解使用去耦電容的原因能夠增加你對這個問題的理解和認知。

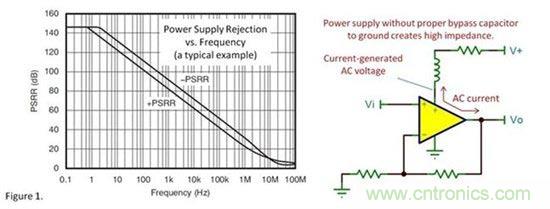

電源抑制比是運放抑制供電發生變化的能力。如圖1所示,在低頻段,運放的電源抑制比是非常高的,但是隨著頻率的增加,電源抑制比會減小。在高頻段,較小的電源抑制比可能會導致運放振蕩。

我們經常認為,外部的供電噪聲會影響運放。但是,運放自身會產生一些問題。例如,負載電流來源于運放的供電。如果沒有合適的去耦,運放的供電端的阻抗就會非常大。這會導致負載的AC電流在供電端產生一個AC電壓,從而構成了一條無意的,不可控的反饋回路。供電端的電感能夠放大該AC電壓。在高頻段,運放的電源抑制比比較低,這條無意的反饋回路能夠引起振蕩。

當然,運放內部電路也會帶來一些影響。如果沒有一個穩定的供電,內部電路的節點之間也可能會產生反饋回路。內部電路的設計是為了使運放工作得更穩定,供電端有較低的電阻。如果沒有穩定的低阻抗的電源供電,運放的工作可能變得特別異常且不可預測。

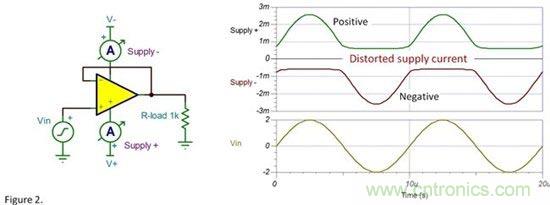

給運放的輸入端加一個干凈的正弦波,較差的去耦產生的反饋回路上可能是一個失真的正弦波。如圖2 所示,在供電端的信號電流經常是失真的,因為它僅僅是正弦信號的一半。如果正端供電和負端供電的電源抑制比不相同,也會使輸出波形失真。

如果負載電流很大,該問題會變得更加嚴重。電抗性負載會產生相位,使負載電流產生相移,這可能會加劇這個問題。容性負載在反饋回路上會產生額外的相移,很有可能會產生振蕩。為了消除這些問題,我們需要較大容值的鉭電容作為去耦電容,并且需要特別注意該電容的布局,應直接連接在供電引腳上,且越近越好。

當然,并不是所有的低質量的去耦都會使運放產生振蕩。如果沒有足夠的正向反饋,或者相移并不是很大,并不會使運放振蕩。但是,運放的性能會大大下降。較大的過沖,較長的建立時間會影響頻率響應和脈沖響應。

在以前的博客中曾經討論過,TINA或者其它的SPICE仿真工具不能很好地仿真出這些現象。SPICE中的電壓源是相當穩定的,不會隨著負載電流而產生變化。要想仿真出實際的供電阻抗非常難,并且結果是不準確的。電源抑制比的值用我們最好的模型macro來仿真,但是,反饋回路上的相位關系不可能完全準確。一般情況下,仿真是很有用的,但并不能準確地預測出上述現象。

你不應該成為一個偏執狂------沒有必要對去耦太過要求。對一些特別敏感的情況和潛在的問題提高警惕就可以了。適當的理解和認知會使模擬設計變得更好。

(來源:EDN電子技術設計,作者:作者:Bruce Trump)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。