【導讀】在超聲及成像等各類系統中,模擬信號的電壓有時可能突然達到極限值。而諸如ADC驅動器之類的多種下游電路可以對模擬輸入信號電平進行限制,以維持其性能。在過驅條件下,這類器件可能過度吸取電流,也可能被驅動至飽和狀態,從而延長恢復時間。

簡介

在超聲及成像等各類系統中,模擬信號的電壓有時可能突然達到極限值。而諸如ADC驅動器之類的多種下游電路可以對模擬輸入信號電平進行限制,以維持其性能。在過驅條件下,這類器件可能過度吸取電流,也可能被驅動至飽和狀態,從而延長恢復時間。

在這類系統中,可以利用多種箝位放大器來對輸出端的信號偏移進行限制,以保護下游器件。目前,多數箝位放大器都依賴于一種稱為輸出箝位放大器(OCA)的輸出箝位架構。一種被稱為輸入箝位放大器(ICA)的新型架構可提供更高的箝位精度和更低的失真。

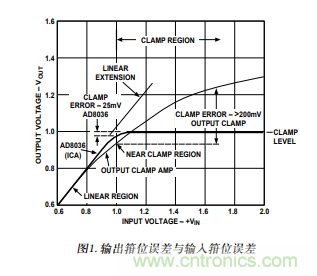

圖1顯示了兩種器件的相對性能。可以看出,在線性區,ICA更接近直線,進入箝位區后有所彎曲。另一方面,OCA在接近箝位電壓時,偏離直線的時間更早。當然,響應更接近直線的程度顯示了放大器在該區的線性度。

目標最大偏移稍寬,以最大限度降低失真。因此,用ICA取代OCA時,箝位區可以較窄而不增加額外的失真。這樣做可以降低下游電路在過驅過程中的電壓。在多數設計中,進行這樣的調節只需要對產生箝位電壓的電路略作修改即可。

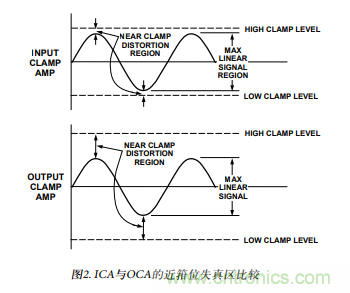

圖2即顯示了這種概念。各類放大器的線性信號幅度都是相同的。但是,由于近箝位失真區較大,必須將OCA的箝位電平上下限設得稍寬一些,以保持信號的線性度。因而,在過驅條件下,下游電路在由OCA驅動時,信號將大于ICA驅動的情況。

另外,由于ICA具有更出色的過驅特性,結果將進一步改善過驅響應。對于低增益箝位級,ICA輸出偏移箝位設定電平的值不會超過10 mV。另一方面,OCA的過沖將達幾百毫伏,具體取決于過驅信號的大小。同樣,圖1顯示了這種概念。顯然,ICA在箝位區的性能相對平坦,不受過

驅幅度的影響,而OCA輸出則隨過驅幅度加大而增加。

ADI推出的前兩款輸入箝位放大器AD8036和AD8037采用ICA結構。但是,由于它們在工作原理方面存在差異,除了工作增益為+1的電路,在設計中以ICA取代OCA并不是“直接”替代即可,盡管兩種器件的引腳排列都是相同的。但是,由于二者的引腳排列相同,一般而言,不需要對電路進行太多修改。不過,對于每種狀況都必須對每種配置單獨處理。下面將詳細討論進行這種替換時需要考慮的因素。

反相工作

需要考慮的第一個因素是運算放大器的工作極性。AD8036和AD8037的輸入箝位運算放大器架構不是反相工作模式。因此,不能直接用適用于反相配置的ICA取代OCA。為了在反相應中發揮出ICA的出色箝位特性,必須采用一個獨立的反相級。

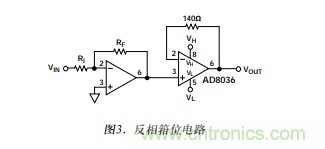

圖3所示電路中,反相級之后為ICA,即同相配置的AD8036,用于提供反相箝位放大器的整體功能。圖中所示電路的增益為–RF/RI,箝位電壓為VH和VL。有關箝位級的工作原理,將在下節進一步討論。在所有箝位電路中,VH必須大于VL,但二者可以為器件輸出范圍內的任何值。

對于要求增益大于(-)1的電路,設計人員可以選擇如何在反相級與箝位級之間分配增益。為獲得最高精度,應降低ICA的工作增益,因為箝位精度是增益的函數,對此下一節將詳述。需要的額外增益可以在反相級中提供。

同相工作

單位增益

對于取代同相OCA的情況,最重要的考慮因素是箝位放大器的工作增益,因為ICA的輸出箝位電平是放大器閉環增益的函數。

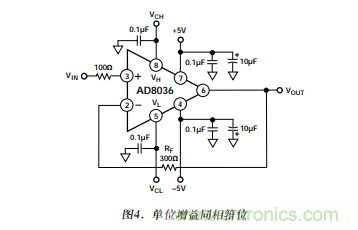

首先需要考慮的是同相單位增益。對于OCA,箝位電平等于施加于VH (引腳8)和VL(引腳5)的電壓。對于ICA,將這些電壓值乘以閉環增益可以算出箝位電平。但是,由于增益為+1,因而ICA和OCA的箝位電平將相等。因此,可以直接進行替換。圖4為單位增益箝位電路示例。

由于這里討論的是同相單位增益,因此,所選的放大器也必須在單位增益下具有穩定的工作性能。在前面提到的兩種ICA中,AD8036針對單位增益進行過補償。因此,可以用AD8036直接取代同相單位增益應用中的OCA。該器件將在相同電平下提供與OCA相同的增益和箝位。

增益為2或大于2

當箝位放大器的同相增益等于或大于2時,可以使用帶寬較寬的AD8037,因為該器件針對等于或大于2的噪聲增益進行過補償。然而,要保持箝位電平不變,必須改變施加于箝位引腳的電壓,因為箝位電平是放大器閉環增益的函數。利用以下等式即可算出正確的箝位電壓:

其中: VCH 為輸出箝位電平上限

VCL 為輸出箝位電平下限

G 為放大器配置的增益

VH 為施加于VH (引腳8)的電壓

VL 為施加于VL

(引腳5)的電壓

一般地,為了使箝位電平維持于采用OCA時的水平,施加于任一箝位引腳的電壓應設為箝位電平除以放大器閉環增益之商。例如,如果放大器的工作增益為2,且其箝位電平上限為1V,則施加于VH(引腳8)的電壓應為1V/2,即0.5V。類似地,如果需要將箝位電平下限設為–1V,則施加于VL(引腳5)的電壓應為–1 V/2,即–0.5 V。圖5所示為增益為2的AD8037的箝位級。

由此可以推斷出,箝位電路中的輸入失調將隨運算放大器級的增益倍數倍增。為了獲得最佳箝位精度,箝位放大器應設為低增益,需要的任何額外增益則于箝位級之前的另一個增益級提供。現實情況下,對于增益不超過10的箝位級,利用ICA都可以實現優于OCA的精度。

有關近箝位區失真的討論仍然適用。箝位窗口必須稍大于最大信號偏移,以盡量減少失真。ADC將在待轉換最大信號電平與最大過驅信號電平之間形成一個區間,在該區間中其指標不會受到影響。箝位電平即應設在這一區域之內。

失調箝位

有些運算放大器應用需要在輸出端提供直流失調電壓。這些一般配置為反相模式,其失調可能由直流電壓產生,該電壓通過求和電阻相加而得,并作為放大器的額外輸入。由于ICA不支持反相模式箝位,因而這種配置不能箝位。可以設計同相電路,同時提供增益和失調。然而,由于用來改變增益和失調的電阻之間存在相互作用,其設計不如反相配置簡單。

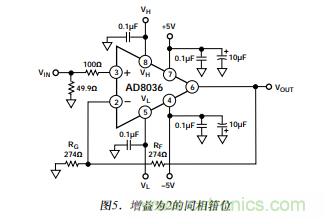

圖6顯示了AD8037的一種同相配置,同時提供箝位和失調。電路所示為AD9002的驅動器,這是一種8位125 MSPS模數轉換器,圖中展示了采用具有失調和箝位功能的AD8037時需要考慮的因素。AD9002的模擬輸入范圍為地電壓至–2V之間。輸入偏移該范圍的值不能太大,以避免吸收過多電流。在地電壓附近,輸入具有對稱性,其幅度為1 V p-p。

為使AD8037在增益為2的條件下正常工作,我們依據數據手冊選用了一個301 Ω的反饋電阻。當增益為2時,R1和R3兩個并聯電阻必須等于反饋電阻R2。因此R1 × R3/(R1 + R3) = R2 = 301 Ω用于提供失調的基準器件為AD780,其輸出為2.5V。為了算出R3的值,先假定同相輸入端的輸入為0V。這會強制反相輸入同樣為0V,該值為–1V(與輸入中點對應的范圍中點),因此,R2中的電流為1V/301Ω或3.32 mA。由于電流不會流入R1或運算放大器的反相輸入端,因此,R3中的電流一定相同。因此

2.5 V = (3.32 mA) R3 或 R3 = 750 Ω.

利用以上等式,可計算出R1的值為499 Ω。

需要對信號進行箝位處理,使輸出在任一方向上偏移ADC最大輸入信號范圍的值不超過100mV。因此,在輸出端,高電平箝位應發生于+0.1V,低電平箝位應發生于–2.1V。

由于箝位發生在輸入級,因此,輸出端的箝位電平不但受電路增益的影響,同時也受失調的影響。因此,為了取得目標箝位電平,VH必須在+550mV時偏置,VL則須在–550mV時偏置。電源與地之間兩個電阻806Ω和100Ω形成的分壓器用于產生箝位電壓。

一般地,輸出端的箝位電平可用以下等式計算:

VCH = VOFF + G × VH

VCL = VOFF + G × VL

其中,VOFF為輸出端的失調電壓。

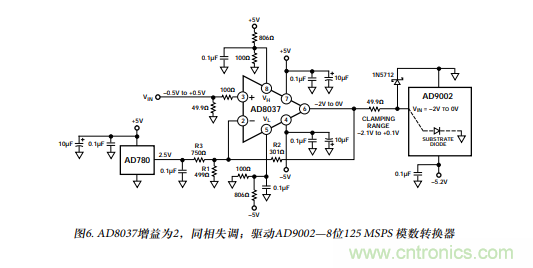

另外,設置箝位電平需要注意,箝位信號(VH和VL)是交替同相輸入,在常規同相輸入超出它們形成的“窗口”時選用。請參看圖7。可以使箝位電壓比輸入信號的最大偏移高出和低出100mV,增益為2。因而,VH應比最大輸入信號偏移+0.5 V高50 mV,即+550 mV。類似地,VL應比最小輸入信號偏移-0.5 V低50mV,即-550 mV。兩種情況下,多出的50 mV將乘以2,結果為100 mV,而相同的失調將同時應用于輸入信號和箝位信號。

1N5712肖特基二極管用于保護AD9002中的基底二極管在加電瞬變期間不發生正向偏置。

其它的考慮一般地,用于產生VH和VL電壓的電阻應保持在低于1k的水平,這樣可以減少偏置電流導致的誤差。另外,建議在接近運算放大器之處用0.1µF電容接地,以旁路VH和VL

。如果未使用兩個箝位輸入之一或者兩者都未使用,則可將相應的引腳置于懸空,放大器的作用將與無箝位放大器相同。如果兩個箝位引腳之一或兩者同時動態驅動,則可以形成一種非箝位情形。此時,VH可針對正偏移無箝位在+V處偏置,VL可針對負偏移無箝位在–V處偏置。

結束語

輸入箝位放大器(ICA)比輸出箝位放大器(OCA)具有更好的箝位性能。對于多數應用,可用ICA取代OCA,但根據各種電路的細節,必須進行必要的修改,以成功完成更替。要成功應用ICA,必須根據具體情況處理各種電路。本文提到的技術描述了多數常見情況下需要的電路變更。

(來源:亞德諾半導體)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱聯系小編進行侵刪。