【導讀】幾乎所有的電子設計師和嵌入式系統開發人員都聽過現場可編程門陣列(FPGA)。對于實際的FPGA器件,設計人員和開發人員都知道它擁有可編程架構,能夠對其進行配置來而執行想要的功能,但他們的了解可能僅限于此。同樣,當涉及創建一個可以在FPGA上實現的設計時,他們可能聽過硬件描述語言(HDL)和寄存器轉換級電路(RTL)之類的術語,但可能并未充分理解它們的含義。

幾乎所有的電子設計師和嵌入式系統開發人員都聽過現場可編程門陣列(FPGA)。對于實際的FPGA器件,設計人員和開發人員都知道它擁有可編程架構,能夠對其進行配置來而執行想要的功能,但他們的了解可能僅限于此。同樣,當涉及創建一個可以在FPGA上實現的設計時,他們可能聽過硬件描述語言(HDL)和寄存器轉換級電路(RTL)之類的術語,但可能并未充分理解它們的含義。

與Verilog或VHDL相似,HDL能讓FPGA設計人員描述設計意圖,正如軟件開發人員使用C或者C++等編程語言一樣。理解HDL的方式之一就是它可以用來描述同時發生的事物,這也是現實世界中硬件工作的方式。相比之下,軟件編程語言通常用于描述順序發生的事。

同時,RTL是常用于邏輯綜合引擎輸入的抽象級電路。該工具將RTL轉換到邏輯元件和互連網絡,然后在FPGA的可編程邏輯內實現。邏輯綜合引擎可以比作軟件開發者的編譯器,后者采用高級程序作為輸入,并將其轉換為由處理器執行的機器代碼。

FPGA的可編程結構可用于構建硬件加速器,以低功耗執行數據處理任務。可編程結構經過配置后可創建一個或多個更適合處理決策任務的軟核處理器,這些處理器還可以控制硬件加速器,包括向其提供數據并根據結果采取相應措施。

RISC-V就是這樣一種處理器,它是一種開源指令集架構(ISA),可以通過開源許可免費獲得。RISC-V開源硬件概念的創造者受到Linux開源軟件成功的啟發。RISC-V的一大優勢是在各類設計實現中都有出色的軟件兼容性,并且目前這些處理器的使用急劇增長。

然而,對于想要使用這種處理器的非FPGA設計人員而言,問題在于他們缺乏有關FPGA設計語言、工具和流程的專業知識。為了解決這個問題,低功耗可編程FPGA的領先供應商萊迪思半導體開發了名為Lattice Propel™的工具,這是一款基于圖形用戶界面(GUI)的設計環境,任何用戶(無論是否具有FPGA專業知識)都能使用它以拖放的方式快速設計基于RISC-V處理器的系統。

Propel輸出的是RTL文件,可以發送到綜合引擎,生成可載入FPGA的配置文件。之后軟件開發人員可以在基于FPGA的RISC-V設計實現上運行他們的RISC-V可執行文件,正如在其他任何RISC-V處理器上運行一樣。萊迪思為其FPGA客戶免費提供RISC-V IP核。

基于FPGA的解決方案

數據處理要求有合適的計算引擎。開發者擁有諸多不同選擇,包括微處理器(MPU)、微控制器(MCU)、圖形處理器(GPU)、FPGA和SoC等器件。

MPU和MCU在執行決策任務時效率很高,但是在實現原始數據處理算法時,無論是處理時間還是功耗都不太理想。SoC能以最低的功耗實現最高性能,但缺點是開發起來價格昂貴、耗費資源且十分耗時,并且在此類芯片架構中實現的算法基本上都是固定無法更改的,而系統采用的協議和標準會不斷變化,因此會帶來很多問題。

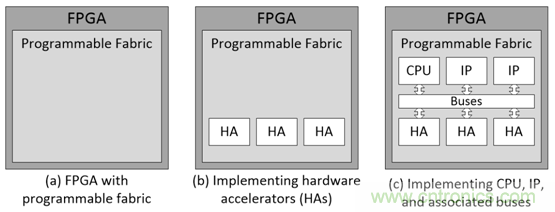

某些數據處理任務(包括許多AI/ML算法)非常適合并行處理。FPGA的可編程架構(圖1a)經配置可實現硬件加速器(HA)功能,以大規模并行方式執行任務(圖1b),從而顯著提高性能,同時降低功耗。

許多情況下還需要數據協處理功能,使用中央處理器(CPU)來強化硬件加速器,處理器可以執行高級決策和控制功能。不同于直接在芯片中實現的硬核CPU,FPGA的可編程架構能夠實現軟核CPU以及相關的總線結構(地址、數據、控制)和任何所需的外設IP功能(圖1c)。

圖1. 結構化總線的方法廣泛適用于各類應用,包括嵌入式視覺、安防和人工智能。

需要注意的是,根據FPGA器件和用戶的要求,額外的可編程邏輯功能和外圍通信功能(例如USB、MIPI、I2C、SPI、CAN和UART)可以通過硬核和/或軟核實現。文章篇幅有限此處不作贅述。

使用軟核CPU有諸多優點,包括能夠配置處理器的操作及許多可選功能,如動態內存訪問(DMA)控制器,從而對其精確調整,高效地滿足目標應用的要求。此外,如有需要,可以配置可編程結構實現其他外設IP功能。如在人工智能應用中,可以使用可編程邏輯資源來創建簡單的人工神經網絡,用于推理之類的任務。

RISC-V

如前所述,RISC-V是基于已有的精簡指令集計算機(RISC)原則的開源指令集架構,可通過開源許可獲得。此外,許多公司目前提供支持RISC-V的RISC-V硬核或開源操作系統,并且幾種主流的軟件工具鏈均支持該指令集。

RISC-V的模塊化設計包括基礎指令集和其他的擴展指令集。在行業、技術界和教育機構的共同努力下,兩者已得到長足的發展。基礎指令集規定了指令(及其編碼)、控制流、寄存器(及其大小)、存儲器和尋址、邏輯(即整數)操作以及輔助功能。僅基礎指令集就能實現具有全面軟件支持(包括通用編譯器)的通用計算機。

還可以通過可選拓展指令集實現額外功能,從而讓設計人員靈活選擇其應用所需的功能。RISC-V定義了許多擴展指令集,包括A(原子)、F(單精度浮點)、D(雙精度浮點)、Q(四精度浮點)和C(壓縮的16位指令以減少代碼尺寸,用于存儲空間有限的系統)。上述指令集均可靈活選擇。

圖2. 萊迪思是首個支持RISC-V的基于閃存和SRAM的FPGA供應商。

與作為專用處理器的硬核實現相比,基于FPGA的軟核RISC-V擁有的巨大優勢在于FPGA可重新配置的巨大潛力能夠滿足各種擴展需求。

萊迪思RISC-V軟核IP套件擁有32位RISC-V處理器核以及可選的定時器和可編程中斷控制器(PIC)子模塊。該CPU核支持RV32I指令集、外部中斷和符合JTAG IEEE 1149.1規范的調試。

定時器子模塊是一個64位實時計數器,它將實時寄存器與另一個寄存器進行比較以觸發定時器中斷。PIC子模塊最多將八個外部中斷輸入聚合為一個外部中斷。處理器核通過使用行業標準的32位AHB-L總線接口訪問子模塊寄存器。

萊迪思Propel

許多嵌入式系統的設計人員都對使用FPGA很感興趣,但是一想到要使用傳統的FPGA設計工具和HDL就望而卻步。為了解決這一問題,萊迪思Propel采用了基于圖形用戶界面(GUI)的設計環境,任何用戶(無論是否具有FPGA專業知識)都能使用其拖放的設計方式快速構建和配置基于RISC-V處理器的設計。

Propel輸出的是使用Verilog HDL語言的RTL文件,可以將其發送到綜合引擎,生成可載入FPGA的配置文件。該配置文件可用于萊迪思CrossLink™-NX(面向嵌入式視覺應用)、Certus™-NX(通用FPGA)以及MachXO3D™和Mach™-NX FPGA(安全系統控制)系列產品。FPGA配置完成后,軟件開發人員可以在基于FPGA的RISC-V設計實現上運行他們的RISC-V可執行文件,正如在其他任何RISC-V處理器上運行一樣。

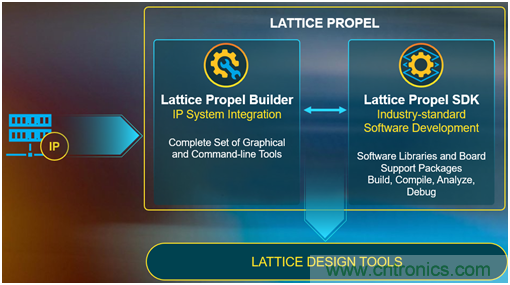

Lattice Propel由兩個部分組成。首先是Propel Builder,它提供圖形化的拖放界面,讓用戶選擇IP模塊并將其連接在一起。這些IP模塊包括RISC-V處理器(帶有可選的定時器和中斷控制器)、AMBA總線結構、接口、存儲器、輸入/輸出(I/O)等。用戶還可以方便地在線升級現有IP模塊和獲得新的IP模塊。

圖3.Propel界面直觀、易于使用、功能強大。

除了拖放IP實例化,Propel Builder還能自動進行引腳連接,通過向導配置和設置參數以及采用按構造逐步校正進行IP集成。

其次是萊迪思Propel SDK(軟件開發套件),可提供無縫的軟件開發環境。它擁有行業標準的集成開發環境(IDE)和工具鏈。SDK還為Propel Builder定義的系統提供軟件/硬件調試功能以及軟件庫和板級支持包(BSP)。

需要注意的重要一點是,Propel可以很好地對接下游工具,并且它也是一個獨立的程序,且其大小僅為0.5 GB,可以快速輕松地下載和安裝。同樣令人感興趣的是,Propel的所有命令都可以用Tcl編寫,從而提高了設計效率并將其快速集成到用戶自己的設計環境中。

圖4. 無論是簡單的“Hello World”應用還是復雜的嵌入式控制和數據處理系統,Propel都能讓用戶快速完成設計

對于硬件設計,Propel是那些需要FPGA優勢但缺乏FPGA硬件設計經驗的團隊的理想選擇。此外,如果團隊成員確實具有FPGA設計經驗,那么他們還可以根據需要對設計做更為精確的控制。對于軟件設計,Propel提供行業標準的C/C ++開發環境。軟件開發人員似乎更多地使用現成的微控制器。

設計人員可以使用Propel在CrossLink-NX、Certus-NX和Mach-NX FPGA中快速輕松地生成基于RISC-V軟軟核的處理器系統,從而提供復雜的視頻處理、系統控制和系統安全功能,其延遲遠遠低于通過外部獨立處理器實現的設計。

總結

除了擁有以低功耗執行高性能數據處理任務的邏輯功能和硬件加速器外,FPGA內部的可編程架構還可用于實現一個或多個更適合決策任務的軟核處理器,以及用于諸如硬件加速器之類的控制功能,包括向它們提供數據并根據結果采取措施。

RISC-V就是這樣一種處理器,它是一種開源指令集架構(ISA),可以通過開源許可免費獲得。萊迪思是首個支持RISC-V以及為其FPGA客戶免費提供RISC-V IP核的基于閃存和SRAM的FPGA供應商。

對于想要使用這種處理器的非FPGA設計人員而言,問題在于他們缺乏有關FPGA設計語言、工具和流程的專業知識。為了解決這個問題,萊迪思提供了Propel來簡化設計流程,讓開發人員能夠快速設計基于RISC-V處理器的系統。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱聯系小編進行侵刪。