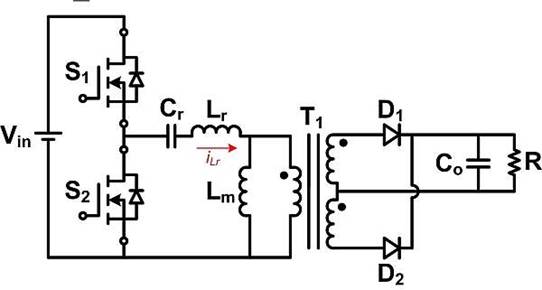

【導讀】電源行業(yè)廣泛應用如圖 1所示的 LLC 串聯(lián)諧振轉換器 (LLC-SRC),它帶有兩個諧振電感器(兩個“L”:L m和 L r)和一個諧振電容器(一個“C ”:C r ) 作為低成本、高效率的隔離式功率級。LLC-SRC 具有軟開關特性,無需復雜的控制方案。

電源行業(yè)廣泛應用如圖 1所示的 LLC 串聯(lián)諧振轉換器 (LLC-SRC),它帶有兩個諧振電感器(兩個“L”:L m和 L r)和一個諧振電容器(一個“C ”:C r ) 作為低成本、高效率的隔離式功率級。LLC-SRC 具有軟開關特性,無需復雜的控制方案。其軟開關特性允許使用具有較低額定電壓的組件,并提供高轉換器效率。與用于其他軟開關拓撲(如移相全橋轉換器)的控制器相比,其簡單的控制方案——具有固定 50% 占空比的可變頻率調制——需要更低的控制器成本。

圖 1LLC-SRC

盡管 LLC-SRC 可以實現(xiàn)比硬開關反激和正激轉換器高得多的效率,但如果您想獲得最佳效率,仍然存在一些設計挑戰(zhàn)。首先,在 LLC-SRC 設計中,兩個諧振電感的比率(L m與 L r 之比)可能必須小于 10,以便提供足夠寬的可控范圍。同時,您將需要 L m上的大電感來降低循環(huán)電流——這意味著您需要保持 L r電感大以保持低諧振電感比。

有趣的是,串聯(lián)諧振電感器 L r中的電流完全是交流電,沒有任何直流成分——這意味著磁通密度變化很大(ΔB 很高)。高 ΔB 意味著與交流相關的電感器損耗高。如果電感器繞在基于鐵氧體的磁芯上,磁芯氣隙附近的邊緣效應會導致較高的繞組損耗。

L r上的大電感意味著更多的電感和更高的交流繞組損耗。這就是為什么許多 LLC-SRC 設計將粉鐵基磁芯應用于諧振電感器,以在繞組損耗和磁芯損耗之間進行權衡。然而,高 ΔB 會在諧振電感器上產生相當大的損耗——要么是高繞組損耗,要么是高磁芯損耗。

LLC-SRC 設計中的第二個挑戰(zhàn)是如何最好地優(yōu)化同步整流器 (SR) 控制。LLC-SRC 整流器電流傳導時序取決于負載條件和開關頻率。LLC-SRC SR 控制最有前途的方法是檢測 SR 場效應晶體管 (FET) 漏源電壓 (V DS ) 并在 V DS低于或高于特定電平時打開和關閉 SR 。在V DS感測方法需要毫伏級的精度,因此只能在集成電路中實現(xiàn)。自驅動或其他低成本 SR 控制方案不適用于 LLC-SRC,因為它們的電流饋電電容器負載輸出配置。因此,LLC-SRC SR 控制器電路的成本通常高于其他拓撲結構的成本。

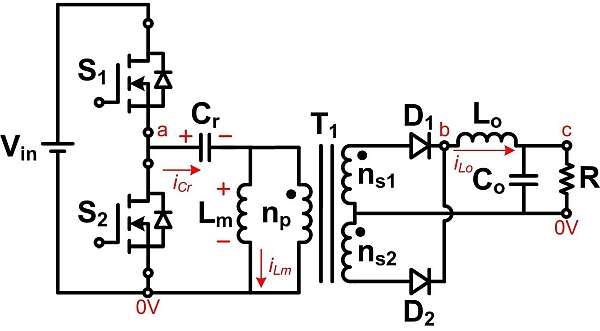

為了解決這兩個挑戰(zhàn)——高電感器損耗和 SR 控制——并且仍然利用諧振轉換器可以提供的大部分優(yōu)勢,請考慮使用改進的 CLL 多諧振轉換器 (CLL-MRC),如圖2所示。

圖 2修改后的 CLL-MRC

與所有三個諧振元件(一個電容器和兩個電感器)都在輸入側的 CLL-MRC 不同,改進的 CLL-MRC 將一個電感器從輸入側移動到輸出側,并將電感器放置在整流器之后 – L o,如圖2所示。這種修改允許諧振電感器上存在直流電流,這意味著較小的 ΔB 和可能較低的磁損耗。

在輸出端有一個電感器也會將輸出配置從電流饋電電容器負載配置更改為電壓饋電電感器負載配置。電壓饋電電感負載配置可實現(xiàn)低成本 SR 控制方案,因為您可以將電感電壓用于感測信號。

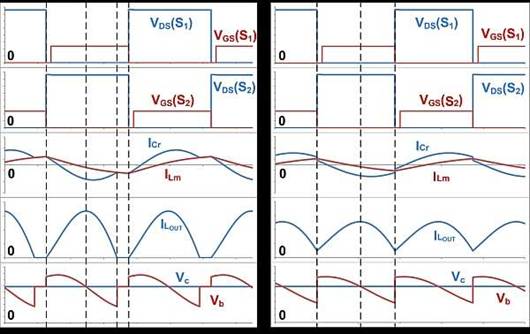

圖 3說明了改進的 CLL-MRC 的操作,其中 f sw是轉換器開關頻率,f r1 = {2π[C r (L r1 //L r2 )] 0.5 } -1是兩個諧振頻率之一。當 f sw低于 f r1,輸出繞組電流在開關周期結束前降至零,就像 LLC-SRC 中的輸出繞組電流一樣。現(xiàn)在你在輸出端有一個電感。一個簡單的電容器和電阻器組可以檢測輸出電感器電壓。每次發(fā)生較大的電壓變化率 (dV/dt) 時,就是開啟或關閉 SR 的時機。因此,SR 控制方案的成本低于 V DS感測方案。

當 f sw高于 f r1 時,輸出電感電流工作在連續(xù)導通模式。換句話說,ΔB 變小,電感交流損耗可以小得多,轉換器效率可能比 LLC-SRC 更高。

圖 3修改后的 CLL-MRC 關鍵波形:f sw < f r1(左);f sw > f r1(右)

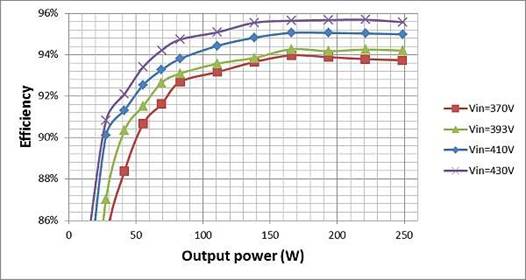

為了驗證這些性能假設,我構建了具有完全相同組件和參數(shù)的 LLC-SRC 和改進的 CLL-MRC 功率級。唯一的區(qū)別是使用 72μH 電感器作為 LLC-SRC 諧振電感器,使用 1μH 電感器作為改進的 CLL-MRC 輸出電感器。

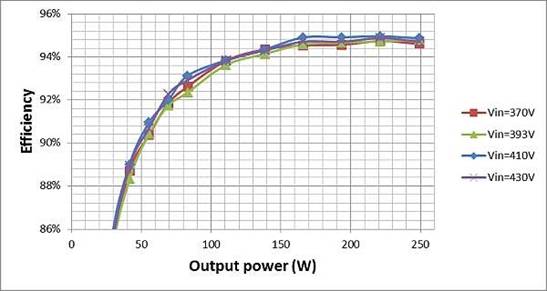

圖 4顯示了兩個功率級的效率測量結果。在較低的輸入電壓下,f sw小于 f r1 - 因此修改后的 CLL-MRC 中的 L o電流仍處于不連續(xù)導通模式,具有較大的 ΔB。因此,在這種操作條件下,改進的 CLL-MRC 沒有效率優(yōu)勢。

當輸入電壓升高時,f sw高于 f r1并且 L o電流處于連續(xù)導通模式。使用 430V 輸入時,改進后的 CLL-MRC 的效率比 LLC-SRC 高 1%。此比較表明,如果您將改進的 CLL-MRC 設計為始終在高于 f r1的頻率下運行,則其效率性能在整個范圍內可能優(yōu)于 LLC-SRC。

圖 4不同輸入電壓電平下的轉換器效率:修改后的(頂部)CLL-MRC;(底部)LLC-SRC

LLC-SRC 確實是一種很好的拓撲結構,并提供了許多吸引人的功能。但根據(jù)應用程序,它可能不是最佳解決方案。有時,您需要跳出思維定勢,以更低的電路成本實現(xiàn)更高的效率。

(來源:中電網)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱[email protected]聯(lián)系小編進行侵刪。

推薦閱讀: