【導讀】前幾天,看到一個比喻,說鎖相環是一個電路的心臟,沒有它,整個電路都工作不了了。想想也是,沒有鎖相環,混頻器沒法變頻,ADC沒法采樣,確實很重要。實際的PLL電路肯定相當復雜,不過,可以從簡單的看起。

前幾天,看到一個比喻,說鎖相環是一個電路的心臟,沒有它,整個電路都工作不了了。

想想也是,沒有鎖相環,混頻器沒法變頻,ADC沒法采樣,確實很重要。

實際的PLL電路肯定相當復雜,不過,可以從簡單的看起。

一個最最簡單的PLL,有三部分組成,VCO,鑒相器(PD)和低通濾波器。

這篇文章呢,就先講講鑒相器的原理。

鑒相器(Phase Detector/PD)

鑒相器,英文名為Phase Detector,簡稱PD。

Phase Detector直譯過來為相位檢測器,讀上去好像比鑒相器通俗一點哦。

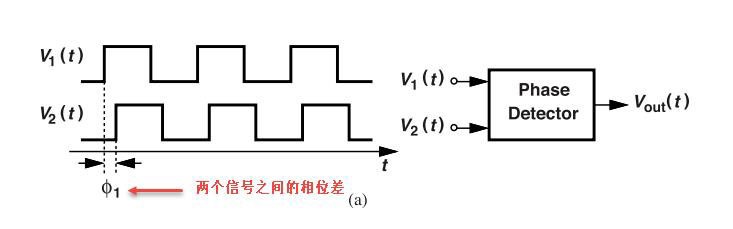

相位檢測器,就如其字面意思,就是檢測相位用的。不過呢,它是對兩個信號的相位差做出反應。也就是說,它不管你相位的絕對值,它是比較兩個相位的相對值。

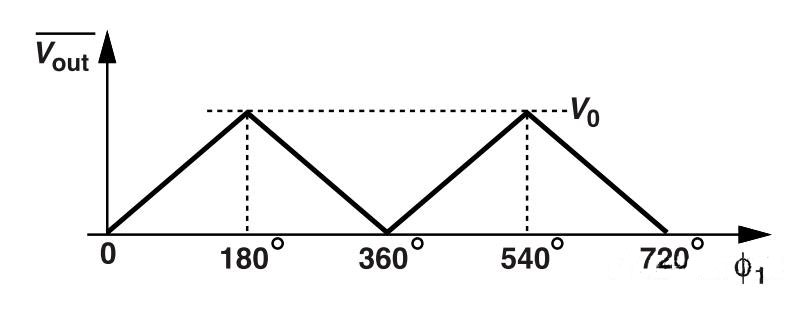

相位檢測器的輸出呢,一般是一個電壓,而且這個電壓與相位差呈線性關系。如下圖所示。

它的主要工作時用來測量兩個信號之間的相位差,然后輸出一個參量,比如說電壓。而這個電壓與相位差呈線性關系。

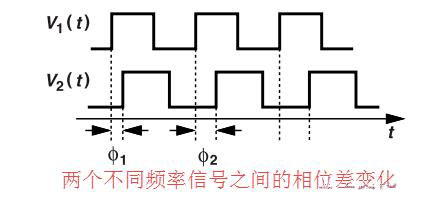

如果V1(t)和V2(t)的頻率不相等的話,兩者的相位差則會隨時間發生變化。如下圖所示。

PD怎么實現呢?

那上述的功能怎么用電路實現出來呢?

異或門

或許你想不到,一個簡單的異或門(XOR)就可以實現上面的功能。當然,實際電路可能比這個復雜,這個等我了解到了,再談。

目前,先從原理層面上看看。

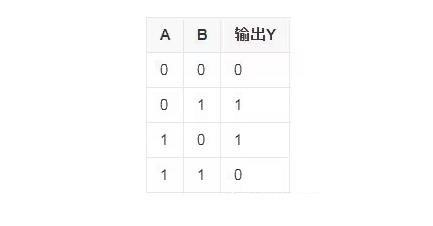

異或門的真值表如下:

換成文字描述就是:當兩個輸入相同時,輸出為0;當兩個輸入不同時,輸出為1.

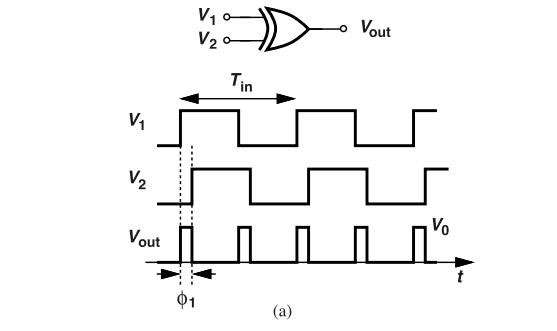

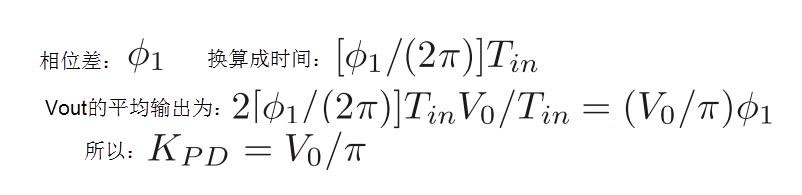

異或門當做PD來使用時,其工作原理如下圖所示。

如上圖所示,兩個方波信號V1和V2,而V2的相位比V1滯后,即V2的變化沿要比V1的來的晚一點。

在一個周期內,V1和V2會有一段時間,電平不一致。

當V1和V2經過異或門時,兩者電平不同時,異或門輸出高;當兩者電平相同時,異或門輸出低。這樣,異或門就將V1和V2的相位差,與電壓輸出連接起來了。

輸出Vout是一系列的脈沖信號,因為上升沿處要高一次,下降沿處要高一次,所以該脈沖信號的頻率是輸入信號的2倍。

脈沖寬度與信號之間相位差的大小成正比關系,也就是說,相位差大,脈沖寬;相位差小,脈沖窄。

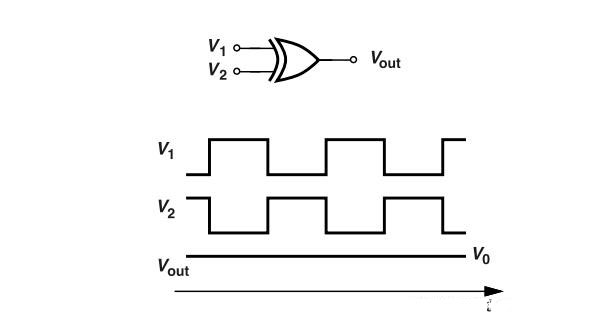

脈沖信號的平均值如下圖所示,與相位差線性相關。

當V1和V2相差180度時,這時Vout的輸出恒定為1, 此時Vout的平均值最大。

當V1和V2的相位差超過180度時,Vout的平均值開始線性下降。

因此,當XOR作為PD時,其輸入輸出的特性曲線如下圖所示。

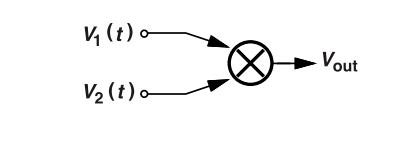

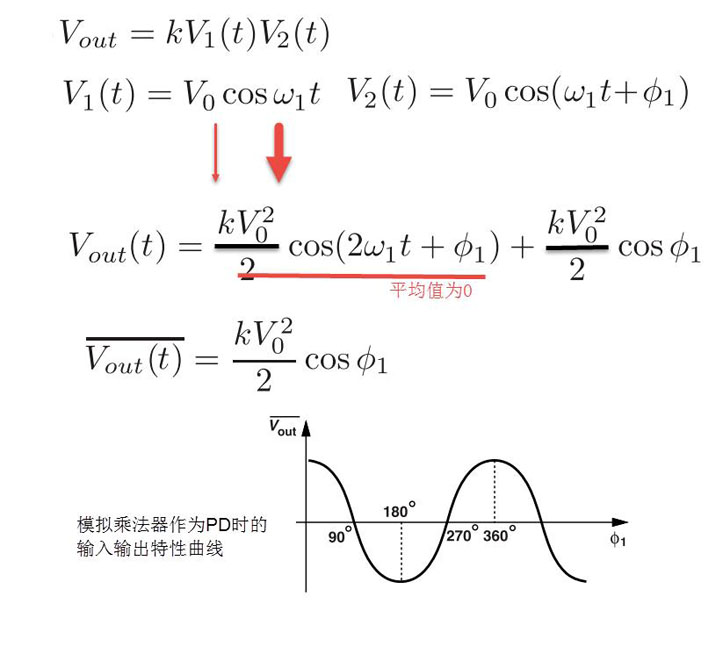

另外,模擬乘法器(或者混頻器),也可當成PD來使用。想不到吧?

其輸入輸出特性曲線如下圖所示。

參考文獻:

Razavi, Design of CMOS Phase-Locked Loops

PS:給自己打個氣,再接再厲,唐僧都取到西經了,總歸會做好的。

(文章來源:與非網)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀: