【導讀】近年來隨著高性能計算需求的持續增長,HBM(High Bandwidth Memory,高帶寬存儲器)總線接口被應用到越來越多的芯片產品中,然而HBM的layout實現完全不同于傳統的Package/PCB設計,其基于2.5D interposer的設計中,由于interposer各層厚度非常薄且信號線細,使得直流損耗、容性負載、容性/感性耦合等問題嚴重,給串擾和插損指標帶來了非常大的挑戰。

碳化硅功率器件在功率轉換效率、改進的高溫性能和使用更簡單的電路拓撲結構方面比硅功率器件具有多項優勢。

在電動汽車牽引逆變器、DC/DC 轉換器和車載充電器 (OBC) 等一些需求旺盛的關鍵應用領域,器件特定的導通電阻 ( R DS(on) × A,其中A是傳導面積)是影響器件電容的關鍵品質因數 (FOM),從而影響硬開關 (HS) 和軟開關 (SS) 拓撲中的效率。隨著電動汽車的快速充電標準向更高電壓和更高功率的方向發展,可能需要并聯多個設備,這可能導致在管理設備方面面臨系統級挑戰,這些設備在性能方面可能無法很好地匹配時間和溫度。因此,較低的 R DS(on)采用低熱阻封裝的器件在這些高功率應用中具有優勢。

UnitedSiC(現為 Qorvo)致力于級聯 SiC FET 架構,與更傳統的 SiC MOSFET 器件相比,該架構在一些關鍵器件參數(包括R DS(on) × A )方面顯示出多項優勢。在本文中,我們將討論其新型第 4 代 (G4) 750 V 額定設備中的部分優勢,并比較這兩種設備架構。

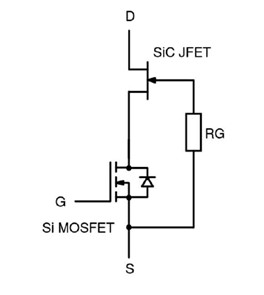

UnitedSiC 的級聯 SiC FET 由一個 SiC normally on JFET 器件和一個 normally off Si MOSFET 組成,如圖 1 所示。

圖 1:SiC FET 共源共柵原理圖(:UnitedSiC,現為 Qorvo)

Si MOSFET 是低壓器件,控制開關的導通/關斷。它利用了數十年的產品成熟度及其近乎理想的 MOS 特性,包括完整的 5 V 閾值電壓 (V th )、卓越的 V th穩定性、卓越的跨導提供與現有 Si 解決方案兼容的柵極驅動電壓,以及寬 ± 20V 額定值。

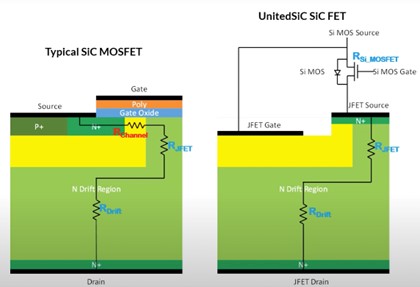

與反載流子遷移率較差的 SiC MOSFET 溝道不??同,Si MOSFET 的溝道電阻非常低。SiC MOSFET 中的總 R DS(on)分量主要來自漂移 (epi) 和溝道電阻 (R ch ) 的組合,隨著額定電壓的降低,前者占主導地位,使其無法在 650-到 750-V 級。在這些額定電壓下,R ch可以超過總 R DS(on)的 50% 。

圖 2 顯示了 SiC MOSFET 和級聯 SiC FET 之間的橫截面圖比較。與 SiC MOSFET R ch相比,級聯方法中使用的 JFET 在 p 摻雜柵極(圖 2 中以黃色顯示)之間存在一個常開通道,它對 R DS(on)的貢獻要低得多。相比之下,級聯低壓 Si MOSFET的 R ch也低得多。

圖 2:SiC MOSFET 和 SiC 級聯 FET 橫截面示意圖(:UnitedSiC,現為 Qorvo)

圖 3 顯示了 UnitedSiC 在650 至 750 V 范圍內對其器件與競爭對手 SiC MOSFET 的關鍵R DS(on) × A指標進行的比較。對于 750-V 共源共柵 SiC FET,該指標在 25C 時大約低 3 倍,在 125?C 時大約低 1.8 倍。

圖 3:SiC MOSFET (650 V) 和 750-V SiC FET 級聯R DS(on) × A比較(:UnitedSiC,現為 Qorvo)

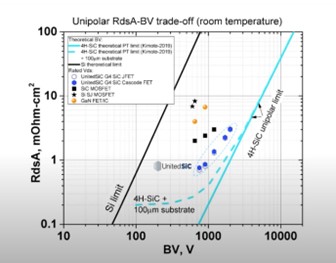

圖 4 顯示了同一指標的更廣泛比較,其中查看了R DS(on) × A與一系列器件的額定擊穿電壓 (BV),包括 Si 超結 MOSFET、SiC MOSFET 和氮化鎵 FET . UnitedSiC 的 G4 SiC 共源共柵 FET 的性能更接近理論極限。

圖 4:R DS(on) × A指標與一系列 FET 技術中的 BV(:UnitedSiC,現為 Qorvo)

我們來看看UnitedSiC在750V電壓等級G4器件上相對于之前的第三代器件所做的一些具體改進:

電壓范圍已從 650 V 增加到 750 V,以更好地針對 400-/500-V 總線電壓。例如,這將滿足當今常用的 1 級和 2 級 EV 充電電壓電源轉換。

改進的單元密度以及進一步的襯底減薄技術已經能夠降低關鍵的R DS(on) × A FOM。這降低了給定管芯尺寸的傳導損耗。

對于給定的 R DS(on) ,較小的裸片尺寸以及其他設計改進會導致較低的輸出電容 (C OSS )/存儲能量 (E OSS ),從而減少 HS 拓撲(例如圖騰柱 PFC)在連續導通模式下的損耗. 較低的時間相關 C OSS還可以在 LLC 等 SS 電路中實現更高頻率的操作,從而提高系統效率。

G4 器件中較低的反向恢復電荷 Q rr改善了 HS 導通損耗。

顯示了 UnitedSiC 750V、6mΩ 器件與具有相同 BV 額定值的競爭對手 SiC MOSFET 之間的參數比較。這兩款器件代表了目前市售的 R DS(on) 750-V SiC 器件。

UnitedSiC 共源共柵 SiC FET 與具有相似 R DS(on)和 BV 額定值的 SiC MOSFET 之間的參數比較

表中的綠色顯示級聯 FET 的相對優勢,而黃色顯示劣勢。讓我們更詳細地討論這些特征:

共源共柵器件具有接近 5-VV th并允許 0- 至 12-V 柵源 (V gs ) 驅動。這使得該器件可以方便地使用任何 Si 或 SiC 柵極驅動器,同時還確保了良好的抗噪性。較低的驅動電壓和較低的柵極電荷 (Q g ) 可降低柵極驅動器損耗。

共源共柵體二極管壓降 (V f ) 的正向壓降要低得多,接近 1 V。這是第三象限中 Si MOSFET 二極管壓降和 JFET 電阻的總和。在 SiC MOSFET 中,V f的范圍為 3 至 5 V,隨著負 V gs的增加而增加,這可能是完全關閉柵極所必需的。較低的Vf可降低第三象限 HS 操作期間的死區時間損耗,并在 SS 電路中失去諧振時實現良好的性能。

在 HS 應用中,反向恢復損耗可能是總開啟損耗 (E on ) 的重要組成部分。圖 5 顯示了 UnitedSiC 完成的反向恢復波形的比較,顯示其級聯結構中的電荷 Q rr低得多。

比較共源共柵 SiC FET 和 SiC MOSFET 的反向恢復波形(:UnitedSiC,現為 Qorvo)

在 HS 應用中,有源開關輸出電容 C OSS的放電能量 E OSS可能是 HS 期間總 E on和 E off的很大一部分,如圖 6 所示。而 E on和 E off損耗很難比較來自不同的供應商,因為它們取決于外部條件,如使用的柵極電阻、電路寄生和允許的過沖,表 1 可用于得出一個廣泛的結論,即級聯 FET 中 HS 損耗的權利較低,源于較低的R DS(on) × E OSS產品。

在 EV 牽引逆變器等電機控制應用中,短路性能是負載可能短路的應用中器件穩健性的重要指標。柵極驅動器需要在此事件期間響應以關閉驅動器 FET 并防止災難性故障。FET 的短路耐受時間 (SCWT) 是衡量其承受此類高壓/大電流事件能力的指標,大多數 SiC MOSFET 的額定短路耐受時間約為 3 s 或更短(如果有的話)。級聯結構中的 SiC JFET 在較高電流傳導下自然傾向于夾斷溝道,這會提高 SCWT 性能。

與 SiC MOSFET 中更平坦的響應相比,共源共柵 FET的 R DS(on)溫度系數更高,在統設計期間必須予以考慮。

級聯方法的另一個潛在挑戰是間接轉換率控制,因為 JFET 的柵極在當前設備中無法直接訪問。與外部柵極電阻器 (R g )的簡單調諧相比,使用小型緩沖器可以很好地管理這一點,從而降低關斷損耗、更清晰的波形和更短的延遲時間。

UnitedSiC的低 R DS(on) G4 級聯 SiC FET 器件的優勢使其非常適用于 EV 牽引逆變器、DC/DC 轉換器、EV OBC 系統、EV 無線充電器以及 AC 和 DC 斷路器等應用。UnitedSiC(現為 Qorvo )在此 750-V FET 系列中提供 6 mΩ 至 60 mΩ的 R DS(on)范圍,使設計人員可以靈活地選擇更低的損耗和更高的效率或更低的成本。他們還在該 G4 系列中提供額定電壓為 1,200 V 的共源共柵器件,可滿足使用 800 V 總線電壓的更高電壓 3 級直流快速充電要求。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀: