【導讀】在人工智能(AI)、機器學習(ML)和數據挖掘的狂潮中,我們對數據處理的渴求呈現出前所未有的指數級增長。面對這種前景,內存帶寬成了數字時代的關鍵“動脈”。其中,以雙倍數據傳輸速率和更高的帶寬而聞名的 DDR(Double Data Rate)技術作為動態隨機存取存儲器(DRAM)的重要演進,極大地推動了計算機性能的提升。從 2000 年第一代 DDR 技術誕生,到 2020 年 DDR5,每一代 DDR 技術在帶寬、性能和功耗等各個方面都實現了顯著的進步。

在人工智能(AI)、機器學習(ML)和數據挖掘的狂潮中,我們對數據處理的渴求呈現出前所未有的指數級增長。面對這種前景,內存帶寬成了數字時代的關鍵“動脈”。其中,以雙倍數據傳輸速率和更高的帶寬而聞名的 DDR(Double Data Rate)技術作為動態隨機存取存儲器(DRAM)的重要演進,極大地推動了計算機性能的提升。從 2000 年第一代 DDR 技術誕生,到 2020 年 DDR5,每一代 DDR 技術在帶寬、性能和功耗等各個方面都實現了顯著的進步。

如今,無論是 PC、筆電還是人工智能,各行業正在加速向 DDR5 新紀元邁進。今年,生成式 AI 市場蓬勃發展,用于大型模型應用的 AI 服務器大力推動了對 DDR5 的需求。隨著內存市場需求的回暖,內存芯片供應商們已著手在今年第 4 季度全面拉高 DDR5 產能,逐步取代現今的 DDR4。

DDR5 的新時代已經來臨,然而,一些挑戰也阻礙了產業的進一步發展。

DDR5 時代:超高速性能背后的設計挑戰

2020 年 7 月,DDR5 內存技術標準正式發布,標志著內存技術開啟了新的篇章。DDR5 以更高的帶寬和性能吸引了廣泛的關注。與之前的 DDR4 相比,DDR5 的最大優勢在于它顯著降低了功耗,同時將帶寬提升了一倍。具體來看,DDR5 當前發布協議的最高速率已達 6.4Gbps,其時鐘頻率也從 1.6GHz 增加到了 3.2GHz。

當我們深入探究 DDR5 的更多細節時,我們也發現這一新技術帶來了一些額外的技術挑戰。例如,DDR5 的電源電壓相較于 DDR4 的 1.2V 降低了 0.1V,達到了 1.1V,雖然較低的電源電壓降低了功耗并延長了電池壽命,但同時也帶來了一些技術挑戰,比如更容易受到噪聲的干擾,這使得信號完整性變得更具挑戰性,因為信號開關時電壓之間的噪聲余量更少,并可能會因此影響到設計。

DDR5 的另一個重大變化是,與 DDR4 的電源管理芯片(PMIC)集成在主板上的方式不同,DDR5 將電源管理 IC(PMIC)從主板上轉移到了雙列直插式內存模塊(DIMM)上。這使得電源管理、電壓調節和上電順序在物理上更接近模塊上的存儲器件,這也有助于確保電源完整性(PI),并增強對 PMIC 運行方式的控制。

此外,在數據位總數保持不變的情況下,DIMM 的通道數從 1 個通道增加到 2 個通道也是一個重要的進步,通過將數據分成兩個較窄的通道傳輸,可以更有效地生成和分配時鐘信號,從而來改善信號完整性。

顯然,DDR5 標準的開發也考慮到了信號完整性問題,將 PMIC 轉移到模塊中也會發揮相應的優勢。然而,設計人員仍然需要考慮兼顧電源影響的信號完整性的整體效應。如上文所述,DDR5 具有高達 6.4Gbps 的數據速率和 3.2GHz 系統時鐘頻率,電源噪聲在這種高速操作中可能會引發更明顯的問題,對系統性能和穩定性造成影響。如果分別進行電源完整性和信號完整性分析,就可能會遺漏電源噪聲引起的問題。

因此,要想充分發揮 DDR5 的性能,必須在系統的所有關鍵點包括芯片、封裝和 PCB 進行兼顧電源影響的信號完整性分析。但是,進行這種層面的分析是一項復雜的任務,它對底層計算平臺如用于仿真分析的硬件、軟件工具都有很高的要求,也會使得總體的設計時間變得更長,增加了設計的難度和復雜性。

充分釋放 DDR5 的潛力,Cadence 的妙計

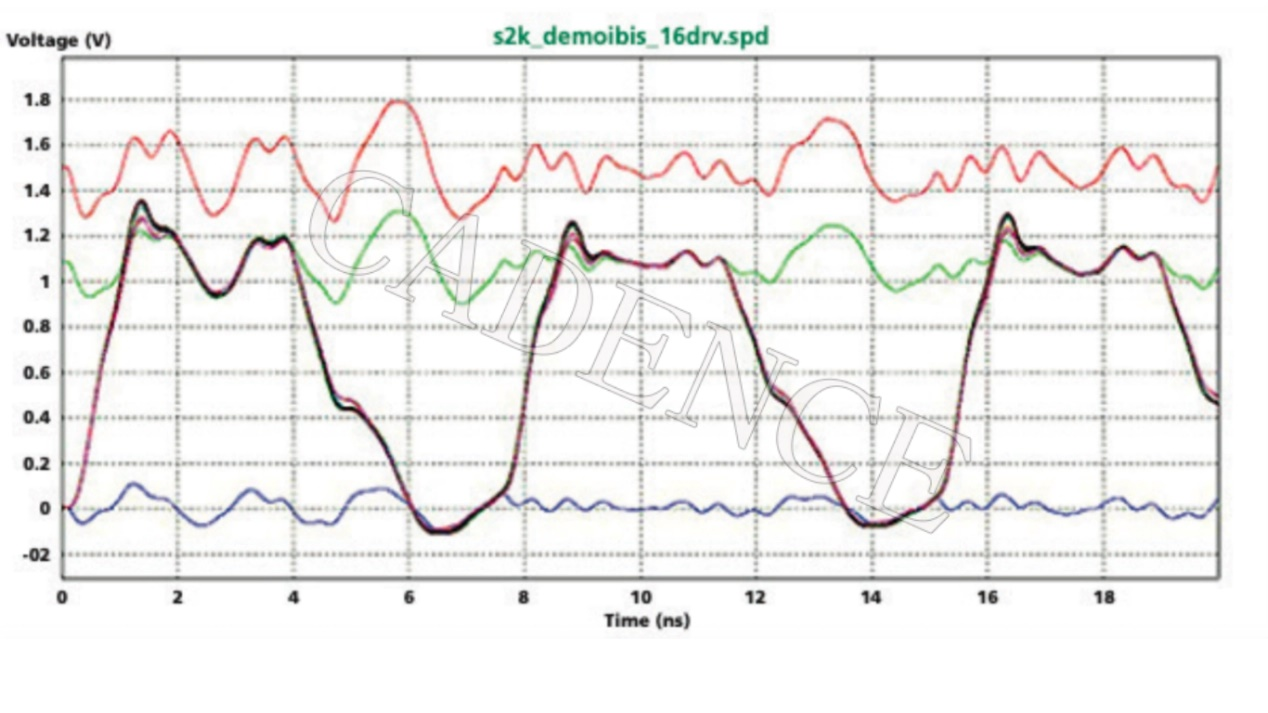

早在 2005 年,“兼顧電源影響”這一概念首次亮相,它是一種能夠同時分析信號與電源噪聲的先進信號完整性仿真方法(圖 1)。兼顧電源影響的信號完整性解決方案必須考慮反射、串擾、時序和其他效應,并配備相應的仿真和規則檢查技術。值得注意的是,要想有效地實施兼顧電源影響的信號完整性仿真,需要在規則檢查和布線后的分析階段進行,因為平面和信號的相互作用/耦合發生在布線完成之后。

因此,一個完整的兼顧電源影響的解決方案往往需要提供:

l 一套針對信號衰減和電源對信號的影響的快速檢查方案

l 能夠模擬大型電路的時域仿真器(多個信號網絡和電源網絡的結果)

l 電源網絡和信號網絡的建模

l 高級輸入/輸出(I/O)緩沖器建模

圖 1:兼顧電源影響的信號完整性仿真結果

盡管市場上的許多工具都支持基本的兼顧電源影響的 I/O 建模標準,不過,隨著內存接口技術的不斷發展,市場對信號完整性工具的要求也日益嚴格,能實現在芯片、封裝和 PCB 上的耦合信號、電源和接地信號的準確提取的工具卻是鳳毛麟角。

在這方面,作為電子設計自動化(EDA)仿真領域的領軍企業,Cadence 推出的 Sigrity X 技術則是針對 DDR4 和 DDR5 提供了真正的兼顧電源影響的信號完整性分析。

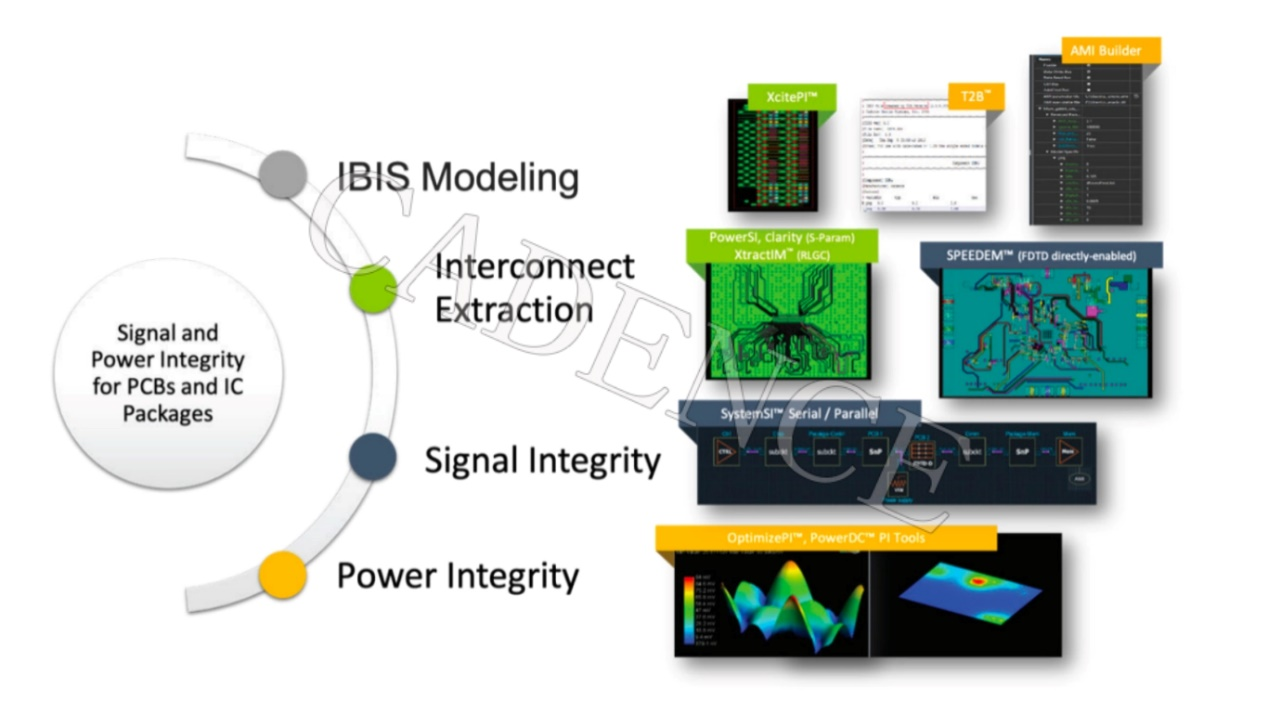

Sigrity X 技術不僅實現了芯片、封裝和 PCB 上的耦合信號、電源和接地信號的精確提取,還能同時針對反射、損耗、串擾和同步開關輸出(SSO)效應進行高效仿真。采用 Sigrity 技術的設計人員能迅速將晶體管級模型轉換為考慮電源影響的行為級 IBIS 模型,從而在幾個小時之內就能提供精準、高效且全面考慮電源影響的仿真,大大縮短了原本需要數天的設計周期。(圖 2)

圖 2:用于 PCB 和 IC 封裝的 Cadence 信號完整性和電源完整性工具

Sigrity X 技術簡化了工作流程,提供設計同步快速仿真和用于最終驗證的簽核級準確度。信號、功率和熱問題可以在每個設計階段予以解決,從而降低了設計和分析團隊間的迭代次數。設計人員可以在設計畫布內運行簽核級引擎來進行高精度的仿真,從而提供高質量的設計,供分析團隊進行驗證。之后,分析團隊利用 Sigrity 大規模并行仿真引擎進行全系統仿真,確保整個“芯片-封裝-PCB-外殼”符合設計規范,并為簽核做好準備。

這些優勢使得 Sigrity X 成為 DDR5 內存和 112G 接口的最佳解決方案。其黃金標準的互連建模,結合了串行器/解串器(SerDes)分析和支持 IBIS 算法建模接口(AMI)的時域仿真(電路和通道仿真),賦予 Cadence 獨一無二的優勢,從而能提取和接口合規性簽核提供完整的解決方案。

進一步的,Sigrity XtractIM 和 Clarity 3D Solver 技術可以配合使用,這讓工程師們能夠針對各種類型的封裝創建出包含耦合信號、電源和接地互連模型的完整封裝模型,有效彌補了封裝設計和封裝表征之間的差距。

此外,Sigrity SystemSI 技術支持快速連接兼顧電源影響的 IBIS 模型和兼顧電源影響的互連模型,設計人員通過這一技術,可以迅速確定出最壞的情況,與 JEDEC 標準進行比對,確保 DDR4/DDR5 接口(包括比特誤碼率要求)符合所有相關規范。

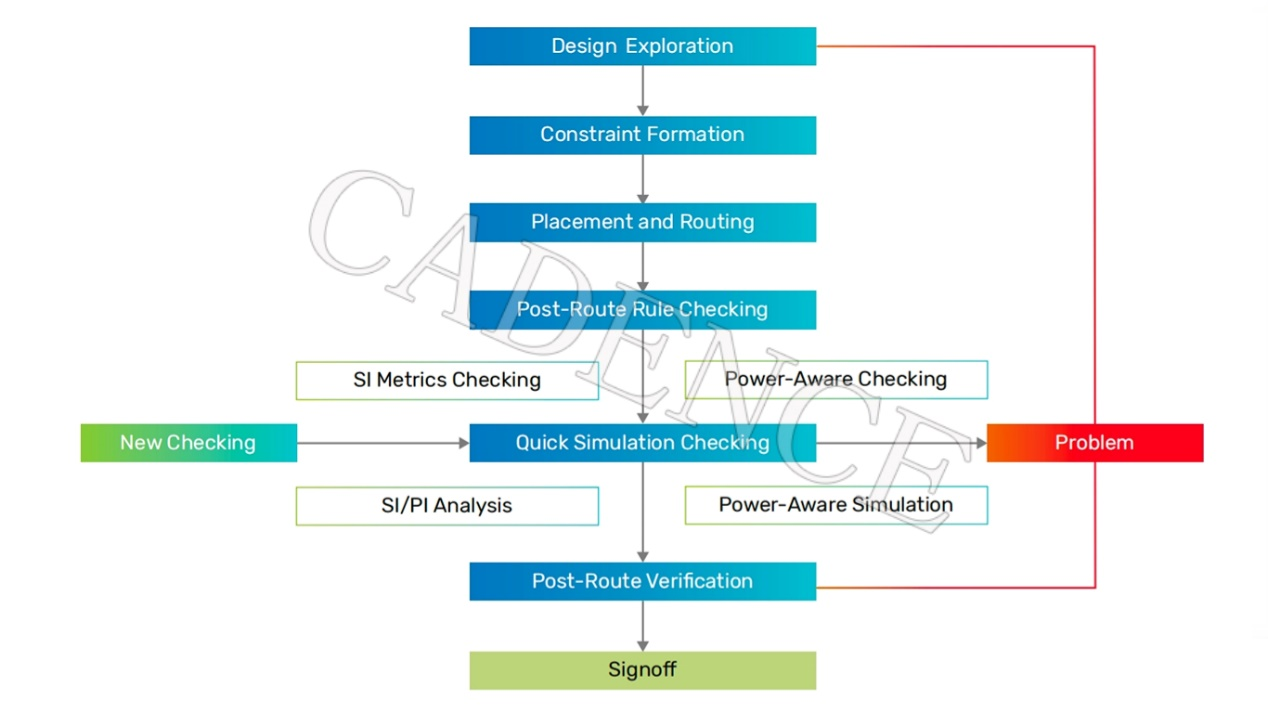

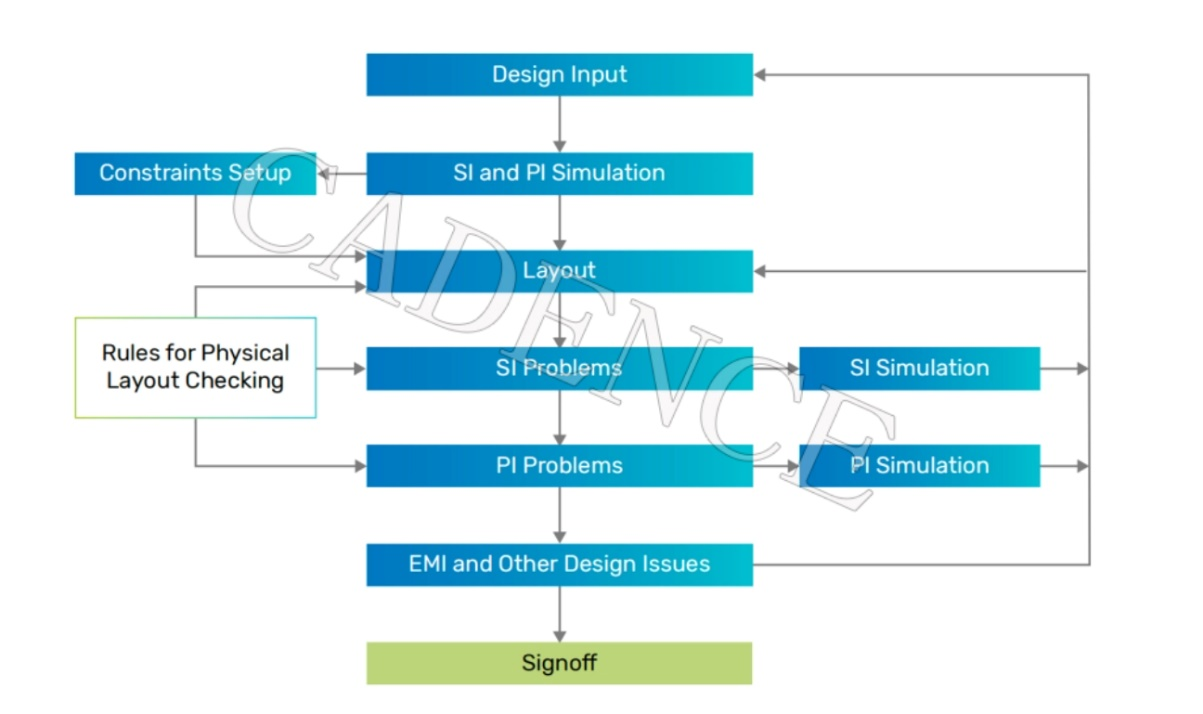

圖 3 是 Cadence 兼顧電源影響的檢查和仿真流程,這與傳統的約束驅動的設計流程(圖 4)形成了鮮明對比。傳統的約束驅動的設計流程主要包含四個部分:預布局布線、約束形成、規則檢查和布線后驗證。

圖 3:Cadence 兼顧電源影響的約束驅動的流程

VS

圖 4:傳統的約束驅動的設計流程示例

當前的眾多現行仿真技術中,信號分析和電源分布網絡(PDN)之間常常存在脫節,也會存在一些其他缺點。通常情況下,根據 SPICE 模型的復雜性不同,有時會使用時域仿真來生成準確的電阻/電感/電容(RLC)模型,而有時則會假設一個理想的接地平面。由此得出的時域模型是基于仿真提取的簡單頻率響應,雖然較為便捷,但是在準確性方面略有不足,而對于更高的頻率,工程師會使用通過混合求解器創建的 S 參數。

其實還有一種高效的方法是利用有限差分時域(FDTD)方法與混合求解器相結合,從而將覆蓋范圍擴大到信號、電源和接地線。

這一方法的成功實踐案例是 Cadence 的 Sigrity SPEED2000 引擎工具,它集成和整合了若干個求解器的輸出,以此解決電路布線以及傳輸線和電磁場問題,能更好地展示數據和電源/接地平面之間在不同時間的相互作用。并使用 FDTD 方法來分析 IC 封裝和 PCB 的布局。為電路設計的進一步優化提供了重要的參考依據。

當進入到最終的簽核階段,工程師通常傾向于使用 3D 全波建模方法以獲得更高的準確度。但這會消耗更多的計算資源并且增加仿真的時間。為了緩解這個問題,可以采用分割和并行化技術。在這方面,通過使用 Clarity 3D Solver 進行基于有限元分析(FEM)分析,然后再結合 Sigrity XtractIM 技術,最終,各個分析結果被重新組合,形成一個基于頻率響應的 S 參數模型,從而實現對整個系統或設計的深入和精確分析。

總結

科技的每一次飛躍,在帶來技術提升的同時,也不可避免地為設計者埋下了新的挑戰。在邁向 DDR5 內存的新時代和新挑戰的路上,有了 Cadence Sigrity X 這把銳利的“利刃”于手,工程師們可以坦然應對信號完整性的各種復雜問題,確保產品不僅與規格相符,更在性能上大放異彩,為未來創新之路再添一磚。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀: