【導讀】GaN 是一種二元化合物,由一個鎵原子(III 族,Z = 31)和一個氮原子(V 族,Z = 7)組成,具有纖鋅礦六方結構。鎵原子和氮原子通過非常強的離子化學鍵結合在一起,從而產生很大的能帶隙。

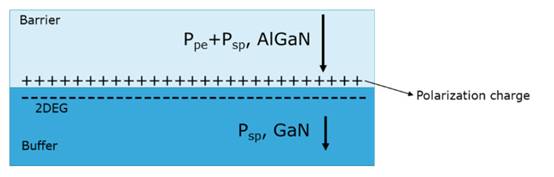

GaN 是一種二元化合物,由一個鎵原子(III 族,Z = 31)和一個氮原子(V 族,Z = 7)組成,具有纖鋅礦六方結構。鎵原子和氮原子通過非常強的離子化學鍵結合在一起,從而產生很大的能帶隙。這一特性使 GaN 非常穩定,非常適合在高溫和惡劣環境下工作。用這種技術制造的晶體管(通常具有橫向結構)稱為高電子遷移率晶體管 ( HEMT )。HEMT 的名稱源于 2DEG 在 AlGaN 勢壘層和 GaN 緩沖層界面處形成的低電阻導電通道。可以借助圖 1 來理解 2DEG 的累積。

圖 1:GaN-AlGaN異質結構的簡化橫截面

圖 1:GaN-AlGaN異質結構的簡化橫截面

與鎵和鋁相比,氮具有更高的電負性(電負性衡量某個原子吸引共享電子對的傾向)。因此,電荷位移會引起電自發極化 (P sp )。另一方面,具有不同晶格常數1 的外延層上的機械應力和應變會引起壓電極化 (P pe )。發生這種情況的原因是,變形有利于晶體內帶電原子的位移,從而產生凈電偶極矩。P pe對于拉伸應變 AlGaN 層為負,對于壓縮應變 AlGaN 層為正。因此,自發極化和壓電極化的方向在拉伸應變的情況下是平行的,而在壓縮應變的情況下是反向平行的。在 AlGaN 中,晶格常數小于 GaN。因此,AlGaN 在 GaN 層上施加應變,從而產生額外的 P pe。

因此,AlGaN 的總極化 ( P sp + P pe ) 較大,從而在 AlGaN/GaN 界面產生凈正電荷。在異質界面產生的自由載流子 (電子) 中和了固定的自發極化和壓電極化,從而形成了具有極高電子遷移率 (范圍在 1,500 至 2,000 cm 2 /Vs 之間) 的 2DEG 層。這種 2DEG 具有高導電性,主要是因為電子被限制在界面上非常小的區域內。由于遷移率較高,因此無需摻雜,從而限度地減少了電離雜質散射現象。

2DEG 層將產生常開(耗盡模式或 d 模式)開關,即具有負閾值電壓 (V th )。為了簡化柵極驅動并使晶體管按照電力電子電路的通常要求安全運行,需要采取額外步驟來確保器件可以在柵極施加 0 V 時關閉。圖 2 顯示了增強模式 (e 模式) 或常關 HEMT 的兩種一般結構。

E型HEMT

圖 2:E 模式(常閉)HEMT 實現:p 柵極(左)和凹柵極(右)(來源:意法半導體)

圖 2:E 模式(常閉)HEMT 實現:p 柵極(左)和凹柵極(右)(來源:意法半導體)

圖 2 描述了兩種本質上常閉型 GaN HEMT 的實現方式:分別為 p 柵極(帶肖特基柵極接觸)和凹陷柵極。第三種方案(未顯示)由 d 模式 HEMT 和硅低壓MOSFET組成,采用共源共柵配置,部分供應商采用此方案。

具有絕緣柵電介質的絕緣柵場效應晶體管具有理想的特性,例如柵極漏電減少和柵極電壓擺幅大。金屬絕緣體半導體場效應晶體管 (MISFET) 通過局部等離子蝕刻工藝完全去除柵極下方的 AlGaN 阻擋層,從而實現 e 模式操作,使器件在零柵極電壓下關閉。當 MISFET 中的柵極電壓超過正 V th時,柵極界面下方會形成電子積累層,從而恢復 2DEG 導電通道的完整性,從而使器件可以打開。MISFET 的一種變體是部分凹陷柵極金屬絕緣體半導體異質結場效應晶體管 (MISHFET)。

顯然,制造 MISFET 的一個非常關鍵的步驟是凹槽雕刻。常見的蝕刻技術是電感耦合等離子體反應離子蝕刻 (ICP-RIE)。該技術將化學反應和離子誘導蝕刻結合在一起,而離子通量的獨立控制可以實現高度靈活性。然而,由于等離子體的照射時間較長,等離子體中的紫外線會對半導體表面造成嚴重損壞。表面損傷反過來會導致漏電流增加、V th不穩定和電流崩塌(動態導通電阻增加)。干原子層蝕刻 (ALE) 是一種可在蝕刻后提供高質量界面的替代蝕刻方法。自限性化學改性僅影響晶圓的頂部原子層,選擇性蝕刻僅去除經過化學改性的區域,一層又一層。ALE 工藝可代替 ICP-RIE,以降低柵極凹槽表面的粗糙度并進一步改善界面處的捕獲狀態。

對凹槽柵極 HEMT 的興趣

如今,大多數 GaN 制造商都選擇了共源共柵或 p 柵極。因此, CEA-Leti近宣布凹陷技術取得了新的里程碑,這引起了人們的真正興趣,并增強了市場增長前景。據分析和咨詢公司 Omdia 稱,GaN 市場規模將在 2030 年達到 38.9 億美元,自 2022 年以來復合增長率為 37%。受益于這種市場擴張的行業包括數據中心(由于為 AI 供電所需的數據流量呈指數級增長)和充電器、汽車和電信等消費應用。如今,微軟、谷歌和 Meta 等大型科技公司正在激烈競爭,以發布使用生成式 AI 模型來處理和生成大量文本和數字數據的產品。這種模型必須依賴大量的計算能力,需要巨大的服務器群,其中使用冷水和電力來冷卻設備。高效 GaN 產品的出現對于構建更環保的電源轉換器來說是一個真正的福音。

眾所周知,傳統的 p-GaN 柵極結構存在可靠性問題,即使在輕微過壓下也容易失效。實驗中檢測到了時間相關的擊穿,這是由 p 型柵極的 GaN 基功率 HEMT 中的正向柵極應力引起的,由肖特基金屬/p-GaN 結控制。當在柵極上施加高應力電壓時,靠近金屬界面的 p-GaN 耗盡區會出現較大的電壓降和電場,從而促進滲透路徑的形成。這種退化的機制與時間相關的介電擊穿相符:在關斷狀態下以恒定電壓進行測試時,柵極電流一開始會變得嘈雜,然后突然增加幾個數量級。

相比之下,全凹陷 MIS 柵極 GaN 功率晶體管比 p-GaN HEMT 具有更寬的柵極電壓擺幅、更高的柵極可靠性和更低的柵極漏電流。

得益于之前與意法半導體的聯合開發努力, CEA-Leti取得了許多進展。

然而,要充分發揮凹槽柵極方法的所有優勢,還有許多挑戰需要解決。MISFET 會受到凹槽區域粗糙表面和電活性缺陷的影響,導致通道遷移率下降。因此,優化絕緣體和 AlGaN/GaN 之間的界面以限度地減少界面捕獲狀態并增強電流流動非常重要。控制絕緣體電荷也至關重要。CEA-Leti 制造工藝的進展主要集中在:

濕法清洗、熱處理和等離子處理以獲得高質量的表面

用于柵極凹槽的低沖擊蝕刻和 ALE

界面層(本例中為 AlN)可進一步降低功率損耗

提高可靠性的薄膜介電層替代材料

所有這些工藝步驟(從表面處理到蝕刻和介電層沉積)都必須認真執行,才能獲得所需的器件規格。正確表征等離子輔助蝕刻引起的損傷以及工業上可行的工藝集成帶來了額外的挑戰,這些挑戰仍需解決。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀: