【導讀】反復試驗的方法將信號發送到 ADC 非常耗時,而且可能有效也可能無效。如果轉換器捕獲電壓信息的關鍵時刻模擬輸入引腳不穩定,則無法獲得正確的輸出數據。SPICE 模型允許您執行的步是驗證所有模擬輸入是否穩定,以便沒有錯誤信號進入轉換器。

ADC 的 SPICE 模擬

反復試驗的方法將信號發送到 ADC 非常耗時,而且可能有效也可能無效。如果轉換器捕獲電壓信息的關鍵時刻模擬輸入引腳不穩定,則無法獲得正確的輸出數據。SPICE 模型允許您執行的步是驗證所有模擬輸入是否穩定,以便沒有錯誤信號進入轉換器。

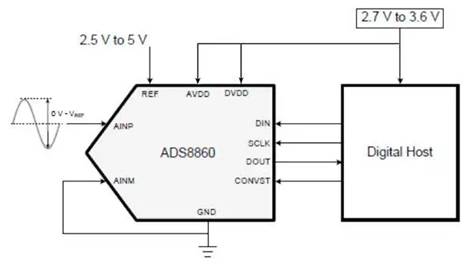

讓我們仔細看看典型的串行偽差分 SAR-ADC,例如ADS8860(圖 1)。

圖 1 ADS8860 是一款偽差分輸入、1 MHz、16 位 SAR-ADC。

該設備的 TINA-TI Spice 宏模型允許您模擬進入轉換器的模擬信號的影響。借助此模型以及 AINP、AINM 和 REF 處的適當驅動器運算放大器模型,您可以在進入 PCB 之前確定是否可以實現良好的轉換。ADC 宏模型的重要性在于它準確地表征了轉換器的輸入端子。驅動 AINP、AINN 和 REF 的運算放大器還必須準確地模擬其開環輸出電阻 (Ro)。

讓我們開始弄清楚這個宏模型是如何工作的。轉換器宏模型使用 55 pF 采樣電容器分別對正輸入和負輸入進行采樣。該設備轉換 AINP 和 AINN 處兩個采樣值之間的電壓差。當您查看模擬結果時,模型必須在采集周期結束時穩定到至少半個 LSB。對于這個 16 位轉換器,半個 LSB 等于 REF / 2 16。

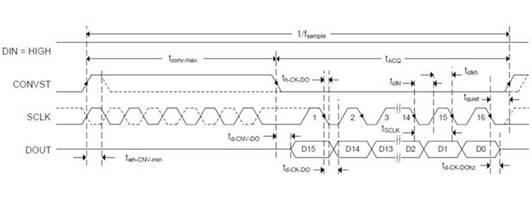

電壓參考引腳 REF 需要在轉換過程中或 CONVST 引腳變為高值后保持穩定的電壓(圖 2)。當 CONVST 為低時,轉換器正在獲取輸入信號(獲取模式)。SAR-ADC 宏模型具有 1 MHz 時鐘,并會產生 CONVST 信號。電壓參考引腳必須在轉換器的整個轉換時間內在位轉換周期結束時穩定到半 LSB 電平。

圖2 在這個具有三線操作的三線時序圖中,CONVST 用作芯片選擇。

圖2 在這個具有三線操作的三線時序圖中,CONVST 用作芯片選擇。

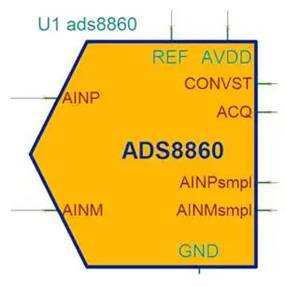

圖 3中ADS8860的 TINA-TI 模型對 AINP 和 AINN 上的輸入信號進行采樣,并在模型的 AINPsmpl 和 AINMsmpl 上顯示結果。

圖 3 這是 SAR-ADC 的 TINA-TI 宏模型。

圖 3 這是 SAR-ADC 的 TINA-TI 宏模型。

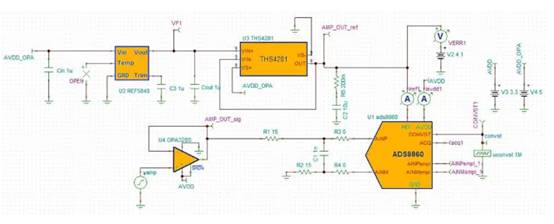

在圖 4中,AINP 處的輸入等于 3V,參考電壓等于 4.096V。在測試輸入信號的精度時,設置ADS8860 TINA-TI 電路以感測放大器驅動器的輸出 AMP_OUT_sig 與其輸出信號 AINPsmpl 之間的差異。在查看此差異時,檢查采集時間結束時或 CONVST 引腳升高之前的區域。驗證信號是否小于半個 LSB。

圖 4 此設置用于 TINA-TI 電路監控模擬和參考輸入。

圖 4 此設置用于 TINA-TI 電路監控模擬和參考輸入。

檢查模擬輸入函數的準確性后,檢查電壓參考引腳的穩定性。在測量 REF 引腳的準確性時,測量電壓參考輸出 (VF1) 和THS4281放大器輸出 (AMP_OUT_ref) 之間的差異。務必使用 VERR1 的值消除電壓參考 ( REF5040 ) 和運算放大器 ( THS4281 ) 產生的偏移誤差。在執行此操作時,使用 iref1 電流表檢查電流尖峰之前的電壓水平。參考文獻 1 為該模擬提供了很好的深入信息。

結論

對于 SAR-ADC 來說,模擬是一件棘手的事情。目前還沒有完整的轉換器模型可以準確地模擬整個設備。您擁有的資源是一個模擬 SPICE 文件,它可以模擬模擬輸入引腳的穩定性。擁有此工具的幸運在于,您擁有一個強大的工具來解決關鍵、困難的轉換器問題之一。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀:

意法半導體推出高性能、高能效、節省空間的36V工業級和汽車級運算放大器