- 高速數據線路對保護器件的要求

- PESD器件的特點與應用

- 具有極低電容值的ESD抑制

- POE技術應用于數據線

- 選用適合GDT作為第一級雷擊防護

Ethernet這一全球應用最為廣泛的局域網技術在不斷更新:802.3ae的出現使10Gbps的速率已成為主流廠商研究目標;LAN和WAN的融合使其應用場所已不再局限于室內;POE技術賦予以太網絡新的含義。在更高速率的呼聲中,USB3.0標準山雨欲來風滿樓,新版IEEE1394也來勢洶洶。所有這些都使未來數據通訊成為一個高速的世界。

隨著行業的匯聚聯合,對數據端口傳輸速率要求的增高,制造商必須對設備需求作出響應,以便容納更高的數據率以及符合當前和擬議中的通信需求。另外,保護昂貴的設備不會受到因用戶錯誤操作、環境危害或電源變化所引起的致命的損壞也是一項關鍵的設計課題。

以太網口、USB2.0、IEEE1394、ITV應用和操作中使用的數字式可視接口(DVI)和高清晰度多媒體接口(HDMI)協議允許高速數據傳輸率,并可以支持即插即用熱插拔安裝和操作。但這些外部端口很容易受到來自工作環境和周邊設備的破壞性的ESD脈沖的傷害。

ESD抑制器件除了保護數據傳輸線路之外,必須保持其信號的完整性。部分以太網端口由于用于樓宇之間,有遭受雷擊感應被損壞的危險,附近電力線的影響也不容忽視。防雷元器件除了保護網絡后端的PHY不被擊穿之外,也必須保持信號傳輸中不會掉包。POE技術由于會疊加在信號雙絞線上,這給此類過壓防護帶來新的挑戰。

通常,較為流行的用戶端以太網聯接支持100Mbps的數據傳輸;USB2.0支持480Mbps的數據傳輸;DVI和HDMI協議更是分別支持高達8Gbps和5Gbps的數據傳輸帶寬。在Ethernet、USB2.0、DVI和HDMI的高速數據率下,傳統保護裝置的寄生電容可能破壞信號的完整性或令其失真。失真表現為由較慢的上升和下降時間所致的高態/低態瞬變的前沿和后沿被修圓。

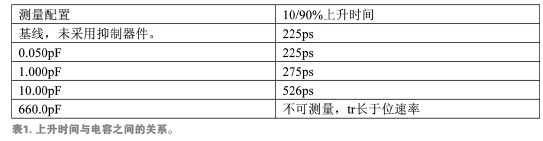

上升和下降時間較慢會給系統帶來一些問題,其中最重要的是時序問題。電路在特定的時間需要穩定的“高”態和“低”態。隨著各狀態之間過渡時間的增加,電路有可能檢測到不完整的過渡期,從而將數據誤差引入系統。表1是不同寄生電容ESD抑制器件對數據上升沿時間(10%至90%高電平)所造成的影響比較。

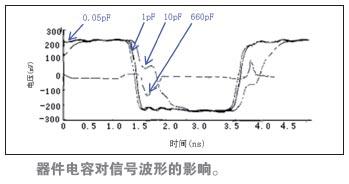

傳輸速率為12Mbps時,其保持電平的時間要長得多(80ns)。在此數據傳輸率條件下,1OpF或更小的電容值將使得數據通過時的失真最小。當傳輸速率提高到480Mbps時,信號具有短得多的電平保持時間(2.0ns)。此時1OpF電容的ESD抑制器件已經引起波形失真:它減少了電平保持時間并使前沿和后沿的形狀大為改變。而660pF電容的ESD抑制器件則造成了相當大的失真,以致于波形甚至無法達到信號工作電壓。圖1顯示了不同ESD抑制器件對480Mbps數據波形的影響。

圖1.器件電容對信號波形的影響

這些數據揭示了在進行超高速系統的數據傳輸線路保護時抑制器的電容特性的重要性。盡管現有的各種抑制器均能夠提供有效的ESD或雷擊保護功能,但不能以犧牲系統的信號完整性為代價。因此,在把抑制器引入電路設計之前,必須對其電容有所考慮。

具有極低電容值的ESD抑制元件(如PESD器件)以及具有極低電容值的雷擊解決方案能夠在提供保護功能的同時保持高速數據信號的數據完整性。由于傳輸最高速率的不同,不同的數據接口所能接受的最高電容是不一樣的。

[page]

譬如,理想USB2.0數據線上的寄生電容總量一般要求控制在10pF以內,而DVI或HDMI數據接口要求則更低,通常低于1pF。但由于設計余量以及其他電子器件寄生電容的影響,對抑制器件電容值的要求更為苛刻。

高速信號和瞬變(如ESD)還帶來了另一個寄生特性—電感。尤其值得關注的是用來實現連接器、芯片及其他任何配套元件之間互連的電路板上跡線的寄生電感。與電容效應相似,由電路板跡線所產生的電感將不會影響低頻信號。但是,在高速條件下,這種電感將產生有可能影響信號完整性的阻抗分量。當高頻信號(如ESD)通過時,少量的跡線電感可能轉換成巨大的阻抗。

ESD防護中,設計師可通過在ESD抑制器和受保護芯片之間設置盡可能大的距離的方法來利用上述特性來完善ESD器件和IC本身間的協同、耦合。雷擊防護中,由于浪涌中的高速頻率成分并不多,寄生電感的阻抗影響較小。這就需要在雷擊防護器件間加入一定的耦合元素。

以太網雷擊防護中,情況略微復雜。這是由于相對于ESD,雷擊能量較高,作用時間長,防護時有時需要多種防雷器件協同保護。同時又要考慮這些防雷器件的電容,耦合器件對阻抗匹配的影響,以及數據線間平衡度的要求。如果再加上POE技術應用于數據線上,又需考慮防雷器件的“誤動作”,以及耦合器件在工作電流下的功耗和壓降等因素。通常的防護概念普遍如此:

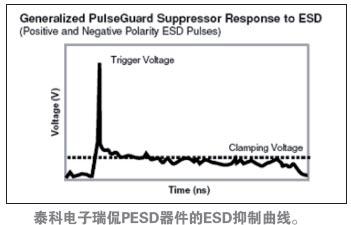

圖3.泰科電子瑞侃PESD器件的ESD抑制曲線。

首先利用GDT(氣體放電管)的低電容,高通流量,但防護效果“粗”的特點,選用適合的GDT作為第一級雷擊防護;其次選用低電容,防護效果“細”的半導體器件組合作為第二級雷擊防護;最后可在以太網隔離變壓器次級選用極低容值反應迅速的ESD防護器件作為“精密”防護。在一二級防護器件間的耦合器件有時還要承擔起過流保護的職責,它的選擇也很關鍵。

泰科電路保護部門擁有符合標準的高品質GDT全系列;晶閘管,SibarTM系列,可在特殊半導體組合下承擔起二級防護功能;極低電容的pESD系列可在充足保護功能下,提供給工程師更大的設計空間。在提供品質優秀的多數防護產品同時,電路保護部門可針對客戶的不同要求,提供高性價比的一攬子解決方案,以及快速的相關技術服務。

ESD的防護對于高速率傳輸端口尤為重要。眾所周知,由半導體技術決定,處理數據越快,芯片對靜電越敏感。對這些端口的靜電保護,要考慮的因素也比較多。

低電容ESD保護對于高速條件下保持數據的完整性是非常關鍵的。在常見的瞬間過電壓抑制器件中,金屬氧化物壓敏電阻(MOV)和多層壓敏電阻(MLV)因價廉物美而應用廣泛。但其固有的高電容決定了其應用范圍只能局限于低頻領域和電源的瞬間電壓抑制上。而硅類ESD防護器件,包括齊納二極管、TVS二極管/陣列等,雖然具有保護電壓低而準確的優點,其寄生電容依舊不可忽視,通常難以適用于高速數據通訊接口,如HDMI,IEEE1394等。

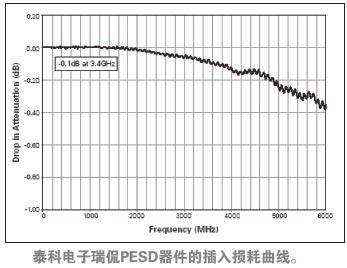

圖4.泰科電子瑞侃PESD器件的插入損耗曲線。

為滿足高速數據通訊接口既ESD保護有效、又不影響高速信號傳輸的要求。近年來,市場上推出了多種專門適用于此類保護要求的器件。其中以泰科電子瑞侃電路保護部推出的PESD器件為代表。該器件的電容極低(通常0.25pF,圖4、圖5展示了PESD的高頻特性),漏電流極小(<0.001A);ESD防護快速有效(響應曲線如圖3所示,觸發電壓典型值為150~250V;響應時間少于1ns);價格低于低電容硅器件。因此,在高速數據傳輸條件下,PESD器件擁有更佳的保護應用特性。該器件已成功應用于HDMI1.3和USB2.0等多種高速接口電路。[page]

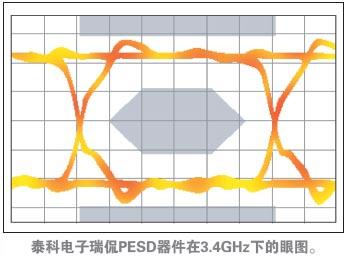

圖5.泰科電子瑞侃PESD器件在3.4GHz下的眼圖。

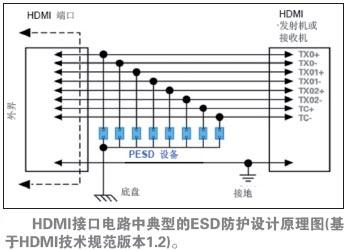

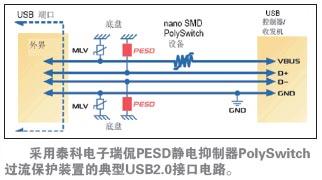

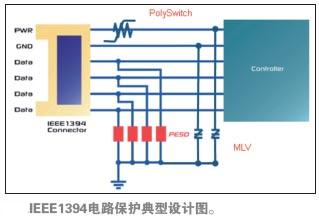

圖6、圖7和圖8展示了利用電路保護部門PESD器件對HDMI1.3、USB2.0和IEEE1394接口電路進行保護的典型應用。這些保護將ESD與敏感電路隔離。在傳輸線路脈沖(TLP)測試和IEC61000-4-2測試中,尤其是經過多次采樣(1000次TLP測試)后,其性能要比其他可比較的元件好。

相對于其他典型的聚合物ESD防護器件,這類PESD器件的較低觸發電壓(通常150V)和低箝位電壓(通常25V)能更好的幫助保護敏感電子元件。該器件采用電子工業中最流行的0603和0402貼裝形式,符合RoHS的嚴格要求;幫助機頂盒敏感電路、手提電腦、手機和其它便攜式設備免ESD侵害。

圖6.HDMI接口電路中典型的ESD防護設計原理圖(基于HDMI技術規范版本1.2)。

圖7.采用泰科電子瑞侃PESD靜電抑制器和PolySwitch過流保護裝置的典型USB2.0接口電路。

圖8.IEEE1394電路保護典型設計圖。

當選擇了一個抑制和電特性(漏電流、電容)與電路參數相吻合的ESD抑制器之后(如PESD),還需要作出另一項選擇:抑制器應安裝在電路板的什么位置上才能優化電路的ESD保護?“優化”ESD保護指的是使受保護芯片上的ESD瞬變盡可能少。簡單地講,應把ESD抑制器直接放置在連接器的后面。它應該是第一個遭遇ESD瞬變的板級元件。

然后,在實際可行的情況下,任何需要保護的芯片均應盡可能地遠離ESD抑制器。采取這一方法將極大地減輕集成電路所承受的應力。下面列出的是PESD器件安裝位置的相對優先級,按從高到低的順序排列如下:

- ?設置于作為系統屏蔽(機殼)中的入口的連接器的內部

- ?安放于電路板跡線與連接器插腳相互作用的位置

- ?放置于電路板上緊挨在連接器后面的位置

- ?位于可以高效耦合至I/O線路的性能穩定且未受保護的傳輸線路

- ?設置于數據傳輸線路上的一個串聯阻性元件之前

- ?位于數據傳輸線路上的一個分支點之前

- ?靠近IC和/或ASI

與電路板走線相關聯的電感以及任何的封裝寄生電感都將在保護電路中加入阻抗,成為PESD電壓抑制器和IC間的耦合阻抗。因為IC芯片將要承受抑制器兩端和耦合阻抗兩端的電壓之和,理想的設計應使PESD盡可能多承受應力,同時保證兩級防護間沒有遺漏的“死角”。

機殼(框架)的地應是ESD基準,而不是信號(數字)地。目的是把ESD從信號環境中屏蔽出去。使ESDTVS保護器件以機殼的地為基準,可免受不希望的噪聲效應(如接地反跳)的影響。目標是盡量保持“干凈”的信號(數據)環境。