- 當今的集成電路的外部保護要求

- 評估ESD保護的有效性

- PicoGuard® X S技術、硅技術與無源技術比較

- 維持信號完整性、電磁干擾與浪涌保護

隨著SoC特征尺寸的減小,器件更易遭受ESD損傷,越來越多纖薄型工業設計更注重小外形封裝中的ESD及EMI性能。且保護器件必須完全“透明”,不能降低信號完整性,安森美采用先進技術的電路保護方案讓我們知道:ESD有效性和信號完整性可以得到評估和證明。

靜電放電(ESD)保護及電磁干擾(EMI)正在成為所有電氣設備越來越重要的考慮因素。消費者要求的更多功能特性及纖薄型工業設計要求更加注重小外形封裝之中的ESD及EMI性能。

外部保護要求

業界正在采用最先進的技術制造先進的系統級芯片(SoC)。設計人員為了優化功能及芯片尺寸,正在持續不斷地減小其芯片設計的最小特征尺寸。但相應的代價是什么?就是特征尺寸的減小,導致器件更易于遭受ESD損傷。

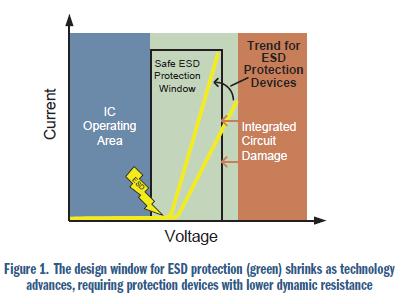

當今的集成電路(IC)給保護功能所留下的設計窗口已經減小。如圖1所示,IC有預期的電壓及電流工作區域,環繞此區域的是安全過壓區。ESD保護必須在安全過壓及過流區工作。隨著業界趨向以更小幾何尺寸和更低電壓制造更先進IC,IC的安全工作區也在縮小。

在以前的IC中,設計人員足以選擇可在IEC61000-4-2ESD規范規定的ESD沖擊下輕易存續的保護產品。因此,大多數保護產品規格書僅列出額定存續等級(如保護器件可在IEC61000-4-2 8 kV 4級接觸式放電條件下存續)。但這并未顯示保護器件在保護敏感電路時的有效程度。有效ESD保護的關鍵是限制ESD事件期間的電壓,令其處于給定芯片組的安全電壓窗口內。ESD保護產品實現有效ESD保護的方式,是在ESD事件期間提供接地的低阻抗電流路徑,如圖1所示;用于新集成電路的保護產品需要更低的動態阻抗(Rdyn),從而避免可能導致損傷的電壓。由于給保護功能所留的設計窗口減小,選擇具有低動態阻抗的ESD保護產品變得更加重要,以此確保鉗位電壓不超過新芯片組的安全保護窗口。因此,ESD保護產品供應商必須提供保護產品有效性的信息,而非僅是保護產品自身的存續等級。

評估ESD保護的有效性

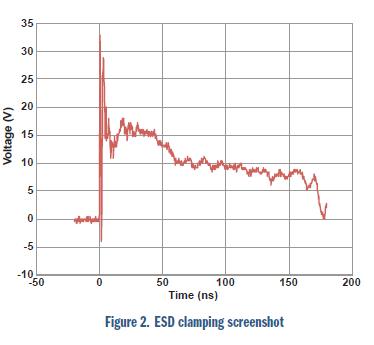

安森美半導體使用兩種方法來顯示ESD保護的有效性:ESD屏幕截圖及傳輸線路脈沖(TLP)測量。ESD屏幕截圖方法捕獲保護產品在被施加IEC 61000-4-2 ESD應力(通常為8 kV接觸放電)時的電壓。圖2中所示的屏幕截圖顯示了安森美半導體的保護器件在遭受8 kV應力條件下在10納秒(ns)時間內將電壓鉗位至20 V以下。屏幕截圖提供形象直觀的保護產品有效性視圖,特別適合于比較針對相同應用的兩款產品。安森美半導體的應用注釋AND8307/D簡述了屏幕捕獲數據。但屏幕截圖并不支持解析出描述保護產品性能的基礎參數。TLP方法則提供更加量化的ESD保護器件有效性衡量手段。

下頁內容:PicoGuard® X S技術、硅技術與無源技術比較

[page]

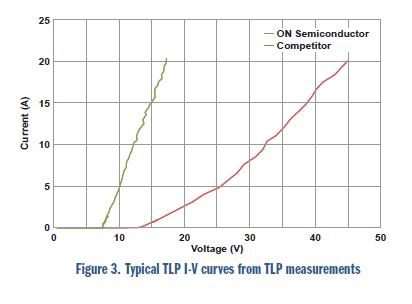

TLP方法創建電流-電壓(I-V)曲線,其中各個數據點是采用與ESD事件在電流波形及脈沖寬度方面密切匹配的方形脈沖獲得的。TLP脈沖寬度通常為100 ns,脈沖幅度最高達40 A。圖3顯示了TLP I-V曲線示例,其中比較了旨在用于相同應用的安森美半導體產品與競爭對手產品。與競爭器件相比,安森美半導體產品以更低的電壓導通,且動態阻抗低得多。TLP I-V曲線以及由此提取來的參數能用于比較不同ESD保護器件的特性,并能用于預測電路的ESD鉗位性能。能夠從TLP數據提取出來的參數包括特定電流電平的鉗位電壓值以及動態阻抗和電壓截距。安森美半導體應用注釋AND9006/D詳細闡釋了TLP技術,而應用注釋AND9007/D介紹了由TLP測量解析出來的規格參數。

PicoGuard® X S技術

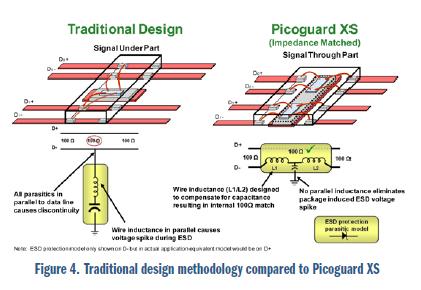

傳統ESD保護產品貼裝在信號走線與地之間,在信號路徑上不會產生中斷。為了將高速數據線路的信號完整性下降問題減至最輕,電容必須最小化,如圖4所示。

安森美半導體優異的PicoGuard XS技術通過使信號路徑穿越保護產品,提供阻抗匹配的信號路徑,故而消除了信號完整性問題,如圖4所示。PicoGuard XS技術平衡了封裝串聯電感與保護二極管電容,提供極佳的100 Ω信號路徑,與印制電路板(PCB)上走線的阻抗匹配。此外,這種設計事實上省下了與保護二極管串聯的電感,因而將ESD事件起始階段的封裝引致電壓尖峰減至最小。

硅技術與無源技術比較

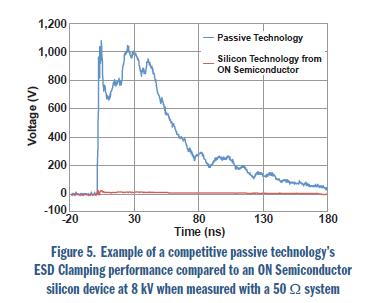

安森美半導體的保護及濾波方案基于先進的硅工藝。相比較而言,其它幾種低成本無源方案結合使用了陶瓷、鐵氧體及多層壓敏電阻(MLV)材料。這些類型器件傳統上ESD鉗位性能較弱。在某些無源方案中,下游器件會遭受的電壓比安森美半導體硅方案高出一個或多個數量級,如圖5中的ESD屏幕截圖所示,其中比較了安森美半導體硅方案與競爭技術在8 kV ESD應力條件下的表現。競爭技術的導通電壓如此之高,以致于它根本不會激活,所測的電壓只不過是在50 Ω測量電路上的電壓降。其它一些更老技術甚至在經歷較少幾次ESD沖擊后性能就會下降。由于材料成分原因,某些無源器件往往在不同溫度條件下的性能表現不一致,因此在惡劣環境下的可靠性更低。

下頁內容:維持信號完整性

[page]

維持信號完整性

ESD及EMI方案用于保護系統,抵御或濾除有損系統整體性能的無用信號。在系統正常工作期間,保護器件不得降低信號完整性。換而言之,它們必須完全“透明”。展示保護產品不會降低信號完整性是重要的。安森美半導體使用幾種不同方法來展示產品不會降低信號完整性。

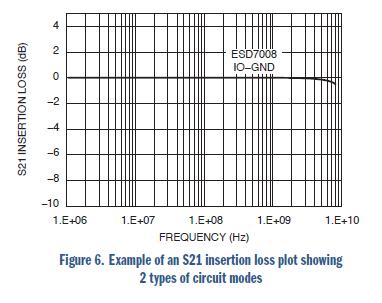

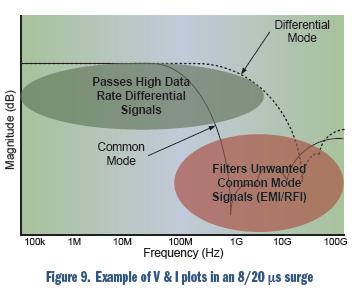

衡量信號完整性效應的一種方式是使用S參數插入損耗圖,如圖6所示。S21圖顯示了不同頻率條件下的功率損耗測量結果。它們顯示了特定器件在特定設計中的工作特性。S參數圖也衡量濾波器的頻率響應,如第5頁中有關共模濾波器的圖9所示。

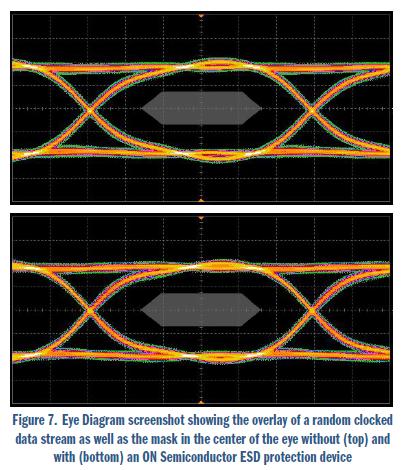

一種經典的高速數據信號之信號完整性展示方式是眼圖,如圖7所示,其中比較了采用及沒有采用安森美半導體ESD保護產品的信號。隨時鐘變化的數字信號的偽隨機圖案以時間軸建立在數字存儲示波器上。高質量的信號將顯示出較大的眼形張開區域,此區域處于不同的數據過渡段的中間。高速接口標準規范定義了位于眼圖中間的六邊形模板(mask)。數據圖案不得穿越模板,因此確保能夠準確無誤地讀取數據。也能夠通過眼圖快速地查看及測量信號的其它關鍵參數。保護產品的存在導致的眼圖質量下降必須極小,就像安森美半導體ESD保護器件的眼圖那樣。

在某些情況下,為了提供最高性能,阻抗匹配對于接口標準至關重要,這些情況下可以采用時域反射計(TDR)測量。TDR顯示完整信號路徑的特征阻抗,包括給定保護或濾波方案對阻抗的影響。USB及HDMI等大多數高速信號標準規定了可以接受的TDR差分阻抗測量值。

電磁干擾(EMI)

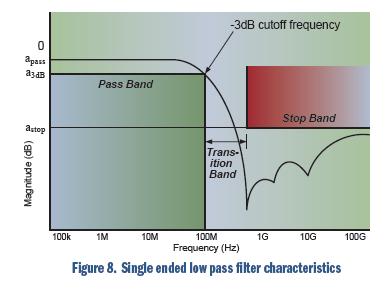

安森美半導體提供兩種類型的EMI濾波器,分別是單端濾波器及共模濾波器。單端濾波器采用不同陣列配置來制造,用于并行接口。這些濾波器包括用于音頻等低速信號的通用電阻-電容(RC)型濾波器和用于較高速度及功率敏感型接口的電感-電容(LC)型濾波器。低通濾波器提供700 MHz至最高6 GHz范圍的截止頻率。截止頻率如第5頁中圖8所示的S21圖所示。單端濾波器無法滿足高速差分接口的需求。差分接口擁有固有的噪聲抑制,但它們不能完全免受可能存在于來自外部源的共模噪聲的影響,亦不能防止接口信號輻射至系統其它元件。

下頁內容:電磁干擾與浪涌保護

[page]

這些應用中能使用共模濾波器(CMF)來消除不想要的共模噪聲,并防止高速信號輻射有害的共模噪聲信號至系統其它元件。同時,CMF還使想要的高速數據事實上不受影響地通過。典型的CMF特性如圖9所示,圖中顯示消除了共模噪聲,同時支持差模信號無損通過。

浪涌保護

除了保護免受ESD沖擊影響,安森美半導體還提供保護免受由雷擊或電力線交叉故障導致的浪涌沖擊影響的方案。廣泛用于多種消費及電信/網絡設備中的一種常見接口是10/100BASE-T和1000BASE-T以太網協議的RJ45接口。它包含4對差分數據線路,每條線路承載最高250 Mbps的數據率。此接口的額定浪涌等級通常遵循的是建筑內部標準。這類接口的保護涉及到確保橫向(金屬或差分)浪涌沖擊不會損傷下行敏感芯片組,例如物理層芯片。提供這種保護的方法是逐線路(就各對線路而言)連接分流保護元件,將入襲的有害浪涌能量傳輸回至浪涌源。

對于較低數據率(10/100BASE-T)而言,安森美半導體結合提供稱作晶閘管浪涌保護器件(TSPD)的消弧(crowbar)器件和類似于ESD保護中所使用元件的瞬態電壓抑制器(TVS)器件。TSPD的優勢是鉗位電壓較低及具有更大浪涌電流能力;例如,它們符合GR-108910/1000 μs標準的100 A要求。因此,它們適合于初級側保護,即“線路側”保護。

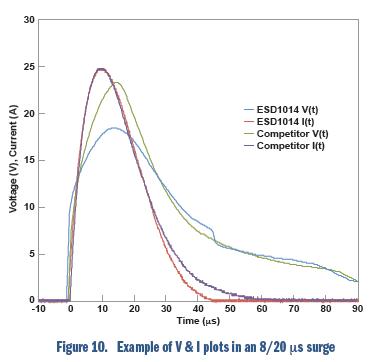

TVS鉗位器件支持8/20 μs脈沖浪涌等級,常用于第三級或物理層芯片側(PHY)的保護,旨在捕獲及安全地泄放任何殘余浪涌脈沖。圖10所示的是施加在安森美半導體新的TVS產品上的8/20 μs浪涌電流時域圖,以及時域響應電壓,清晰顯示了安森美半導體方案相較于競爭器件的優越性。

結論

上述簡介中概括了安森美半導體保護及濾波產品的重要特征。后面將按接口介紹具體產品,并附上方便產品選擇的指引。

未完待續……