【導讀】在使用去耦電容時,重要的是減少引線長度和減小寄生電感,并將電容盡可能地安裝在器件邊上。由于器件工作的頻率越高,轉換速率越陡峭,所產生的RF電流頻譜就越大,需要并接各種去耦電容。

在電子系統中選擇什么類型的去耦電容,以及如何對這些電容進行合理的布局,有一套較為嚴格的數學模型和理論,同時還需要相應的分析工具進行分析。由于這部分內容超出了本書的研究范圍,因此本節僅采用一些現成的結果和Xilinx的一些推薦數據來完成去耦網絡的設計。

在使用去耦電容時,重要的是減少引線長度和減小寄生電感,并將電容盡可能地安裝在器件邊上。為此,電源和地之間的閉環回路(該閉環回路與EMI特性有關)需要在CPLD/FPGA器件的電源腳附近放置一個去耦電容來實現。距離電源引腳越近,效果會越好。

由于器件工作的頻率越高,轉換速率越陡峭,所產生的RF電流頻譜就越大,需要并接各種去耦電容。并接電容的放置一般用于過濾高頻町胄邕量并對線路板噪聲產生旁路作用,通常將多種電容成對圍繞在CPLD/FPGA器件四周,放置在電源和接地引腳之間。在50 MHz系統頻率以下,最典型的高頻去耦電容為0.1μF與0.001μF并聯。在更高時鐘頻率下,則應選擇0.01μF和100μF電容并聯。

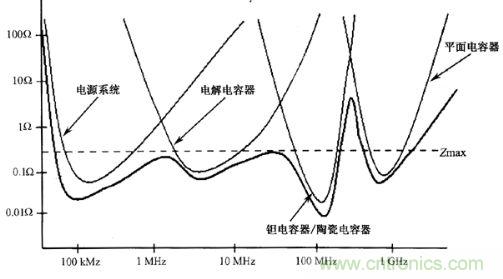

在實際應用中,使用最多的去耦電容器是鉭電解電容和高頻陶瓷片電容。去耦電容通常是根據時鐘或器件工作的第1諧波來選擇,而主要的RF電流是由3次諧波或5次諧波產生的。此時還應考慮該相位的諧波,需要利用各種電容來去耦。另外,時鐘的諧波分量也是一個必須考慮的參數,通常只要對時鐘的5次諧波以下的分量進行處理就足夠了。如下圖所示為常用去耦電容器的自激頻率響應曲線,在自激頻率點附近等效阻抗最小,去耦的效果也最好。在設計中,不同的電容器扮演不同的角色。

圖1:常用去耦電容器的自激頻率響應曲線