電路可靠性,亦即電路抗電氣故障的魯棒性(robustness) , 已日益成為IC設計師的關注點。其中的很多問題多年來已為人所知,有時人們覺得可靠性風險主要是最新制程世代才會面臨的問題。誠然 , 越小的器件、越細的導線、越薄的柵氧化層越容易受到過度電性應力(EOS)的影響 , 而新制程世代 , 對特定版圖形狀和圖案也更為敏感。然而 , 如果設計師認為在成熟節點上不存在電路可靠性問題的話 , 那他今后的項目(project)很可能會面臨一些潛在風險。

這是為何?

因為即使是在成熟的制程上 , 工程師們也會從上面不斷榨取性能、功能、面積及其他相關指標 , 以期獲得更高的投資回報(ROI)。越老的制程的不確定性可能會越少 , 但每一輪新的設計浪潮都會因為有不同的應用需求、及環境條件而引發新的可靠性問題。例如 , 汽車和醫療相關應用芯片設計目前是采用成熟制程技術的新驅動力量。這些應用和采用前沿制程的常見消費型應用相比 , 具有完全不同的設計需求及工作環境。

沒有一家汽車廠商會接受未在嚴格的高溫條件下進行了驗證的發動機控制芯片,而醫療廠商所生產的起搏器(pacemaker)則必須在很長的壽命期內可靠地工作。

此外 , 還有一些新的電路架構在成熟的節點被首次推出時 , 還尚未被發明出來。包含更多模擬電路、更高電壓(比如汽車上的50V)、更高的頻率還僅僅是電路設計師所面臨的、不斷變化的設計要求中的一部分。

這樣就需要有新的工具和方法 , 來確保新制程和成熟制程的電路可靠性。例如, 汽車設備上更高的電壓導致了更高的EOS風險 , 因此設計師需要更努力來確保具有較薄的柵氧化層的數字晶體管不會連接到50伏的電源上。不僅如此,采用高壓設計的電路也需要增大特定位置上的版圖圖案間間距。

針對這樣設計的驗證 , 我們只需要檢查某些特定區域即可 , 如果將整個芯片都執行符合高壓設計規則的較大間距DRC檢查 , 則將導致極端保守的設計考慮 , 以及過大的裸片面積和更高的制造成本。

[page]

有限的傳統方法

很多設計團隊采用用戶生成(user-generated)的標志層(marker layers)或文本點(text points)來檢查EOS問題 , 但這是容易出錯的方法 , 需要設計師人工判定電壓如何在電路節點之間變化、并人工標出需要符合高壓設計規則的正確區域。隨著電路功能的密集改版更新 , 標志層(marker layers)是極難保持的。

在芯片設計日益復雜的今天 , 我們也面臨了其他的風險:靜電放電(ESD)、閂鎖(latch-up)、電遷移(EM)等已知故障機制不能為標準設計做法所完全防止。

其中電遷移在很多代IC上一直是困擾設計師的問題。然而 , 結合了更高驅動強度和采用更細導線在14/16nm實現的FinFET技術 , 成為因電遷移而產生的電路故障的另一個起因。采用傳統方法進行EM檢查 , 將耗費巨大的運算資源 , 需要在整個芯片的每一個部分都提取寄生模型、進行電流仿真和標注最后結果。常見的16nm/14nm片上系統會有數十億個組件 , 想當然耳 , 而進行這樣的傳統檢查過程將非常緩慢 , 是不可接受的。

此外也因為目前所制造的晶體管柵極下的氧化層更薄 , 使得相關器件更容易受到EOS的影響。更困難的是 , 由于現代省電芯片的設計 , 大多數都采用多電源域(multi-power-domain)的策略 , 意味著一個芯片可能有著數十個不同的電源供電。這種更大的復雜性使得檢查出完整的潛在EOS問題變得極度困難。實際上 , 整個芯片的EOS檢查超出了以往各種工具所提供的標準電路仿真和驗證方法的能力。

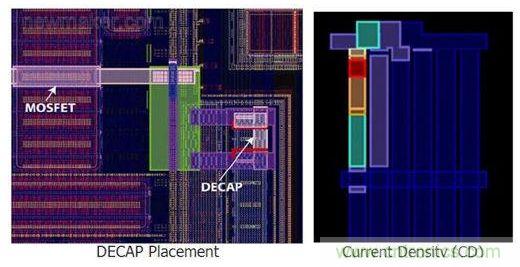

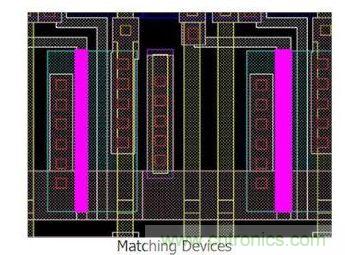

圖1:電路檢查包括去耦電容布局、幾何尺寸匹配及電流密度檢查

[page]

解決老問題 , 需要新方法

過去 , 設計師們依賴電路仿真(circuit simulation)、設計復核(desgin review)、也使用了 標志層(marker layers)或文本點(text points)進行特定區塊的設計規則檢查(DRC)、當然還有其他“自創”方法來查找可能的電路可靠性問題。

但是今天,由于上述所有挑戰 , 要確保一個設計能不出現潛在的可靠性問題 , 就需要一種整體的驗證策略 , 這種策略要能夠實現 電路架構的分類及其相關版圖位置的搜尋、金屬導線的寄生電阻測量、金屬導線的電流密度計算 以及特定區塊的DRC檢查等。

人工方法即將被取代 , 轉而使用可執行電路架構的分類 , 并能識別出相關的電路節點及其版圖位置 , 然后對各種電路類型或問題 , 執行相對應的靜態和動態分析的工具。

這些工具能快速并完整地分析每一器件以及其每個端點的可能的電壓。有了這個信息 , 即可計算整個芯片 , 每一電路節點及其相對應的版圖位置的所有可能電壓、并能進行非常精確和高效的OVD檢查 , 這也就是說可以根據兩個版圖圖案間不同的電壓差,定義出不同的最小可容許距離的設計規則并用此一工具進行驗證。

這些工具還可識別易受到電遷移影響的電路節點及其相對應的版圖位置、測量兩點間金屬導線的寄生電阻、并執行相對應設計規則驗證、來檢測潛在問題。

此外,由于這些問題很多都出現于大型芯片里 , 因此除了完整的功能外, 更需要高效、簡潔的驗證工具 , 以便快速找出電路錯誤的原因。隨著具有這些功能的新工具出現 , 我們現在看到了有數家晶圓代工廠,已開始在提供這一領域的相關驗證解決方案。

但這僅僅是EDA一個新領域的肇始,預計在很長的一段時間里, 我們將會持續使用這樣的工具, 處理以前“無法檢查的”電路可靠性問題的驗證。

相關閱讀:

如何快速而有效地解決IC失效問題

http://hdh-sz.com/test-art/80021528

IC智能卡失效的機理研究

http://hdh-sz.com/sensor-art/80007951

淺談IC對EMI控制的影響

http://hdh-sz.com/emc-art/80020357