【導讀】與傳統的攻擊技術相比,差分功耗分析(DPA,Differential Power Analysis)攻擊技術具有更強的攻擊性和解密效率,因此防DPA攻擊的設計方法越來越引起電路設計工程師的重視。本文從組合邏輯、寄存器、存儲器、傳輸數據結構和中間狀態等幾個方面對防DPA攻擊的電路設計方法進行了介紹。

最近,一種DPA攻擊技術被用來破譯集成電路中的重要信息。DPA攻擊技術的原理是:當芯片在執行不同的指令進行各種運算時,對應的功率消耗也相應變化。通過使用特殊的電子測量儀和數學統計技術,來檢測和分析這些變化,從而得到芯片中的特定關鍵信息。這種利用指令的電流變化來分析密碼算法和密碼的方法,和以往的攻擊技術有根本的不同,因此防DPA攻擊的設計方法越來越引起電路設計工程師的重視。

傳統的防DPA攻擊的方法有兩種:一種是用隨機數發生器產生額外的噪聲和干擾信號,另一種是通過增加濾波電路來消除噪聲。這兩種方法都具有其固有缺陷,它們都會增加芯片的面積,其中前一種方法還會增加額外功耗,后一種方法則只是相對增加了DPA攻擊的難度,并不能徹底解決DPA攻擊問題。

本文介紹的防DPA攻擊的電路設計方法不同于傳統方法,它從DPA的攻擊原理出發,專門針對DPA攻擊而設計,能有效解決通過分析芯片電流變化來進行攻擊的問題。這種防DPA攻擊的電路設計方法從分析集成電路的基本電路單元開始,由簡到繁設計出防DPA攻擊的復雜電路,從根本上解決了DPA攻擊問題。

防DPA攻擊的基本電路單元

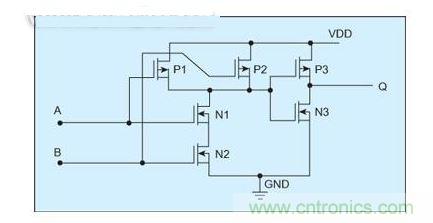

一個典型的CMOS NAND電路通常由4個MOS管組成,包括2個PMOS管和2個NMOS管。圖1是一個CMOS AND電路,它是由一個NAND電路(P1和P2的參數相同,N1和N2的參數相同)和一個NOT電路組成。

圖1:CMOS AND電路由一個NAND電路和一個NOT電路組成

由于P1和P2的參數相同,而且這兩個晶體管是并行的,所以當輸入信號A變化或者B發生變化時,這兩個PMOS管對AND的瞬態變化的影響一樣。而N1和N2是串行的,因此當輸入A=1、B=0時,NAND的瞬態特性與輸入A=0、B=1時的瞬態特性不同。雖然理想CMOS數字邏輯門在靜態條件下不會消耗電流,但當輸入信號變化時,它會消耗一定電流。這是因為MOSFET和信號傳輸線都存在寄生電容,并且當邏輯門處于變化狀態時,Vdd和Gnd都存在瞬態電流。因此,這個與門的瞬態電流大小不僅與輸入信號的變化有關,還與輸出值Q有關。

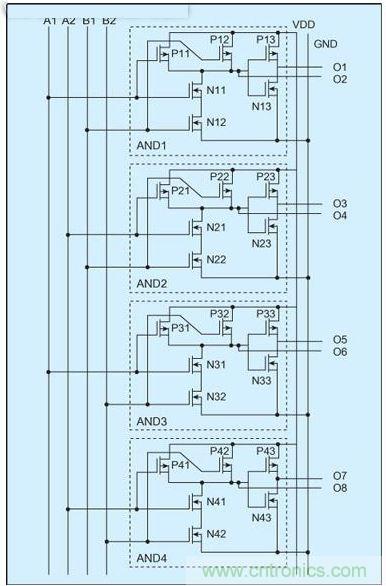

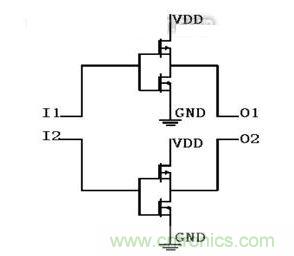

本文介紹的防DPA攻擊的基本電路單元,對所有可能的輸入信號都表現出相同的電特性。這些電特性包括導通和閉合的PMOS管和NMOS管的數量、輸入線的電容負載、輸出線的負載以及電路單元自身的瞬態電流。圖2為該基本電路單元的電路結構。

這個門電路有A和B兩個輸入,輸入信號是2位的常數漢明權重碼(constant Hamming weight representation),即A1和A2分別是0、1時對應“假”邏輯,1、0時對應“真”邏輯。在圖2中,信號傳輸都是以2位漢明碼形式進行,因此無論A和B信號如何變化,翻轉的MOS管的數量都相同,且是一個常數10。

圖2:防DPA攻擊的基本電路單元的電路結構

這個防DPA攻擊的基本電路單元還可以表達多種邏輯。當需要表達AND邏輯時,輸出為O1、O2,其中O1為漢明碼指示位;當需要表達NAND邏輯時,輸出為O2、O1,其中O2為2位漢明碼指示位;當需要表達OR邏輯時,輸出為O7、O8,其中O7為漢明碼指示位;當需要表達NOR邏輯時,輸出為O8、O7,其中O8為漢明碼指示位。而O3、O4、O5和O6是沒有作用的輸出信號,但為保證各種輸入情況下基本單元的對稱性和相同性,這幾個輸出管腳在實際電路設計中應盡量和O1、O2、O7、O8接相同的負載。

[page]

防DPA攻擊的主要目的是使電路電特性在運算時保持相同,而保持電特性相同很重要的一點是使整個電路在運算時翻轉的晶體管數量是一個常數。在傳統電路中,翻轉的晶體管數量與當前狀態和先前狀態相關,跟輸入參數也相關。本文介紹的電路設計方法能使翻轉的晶體管數量在任何運算步驟中都是一個常數。為實現這個目的,電路運算步驟之間增加了一個中間步驟,最簡單的中間步驟的設置是在輸入參數和電路運算完成之后設置系統中間值。中間步驟的設置能防止有用信息從功耗分析中泄漏出去。

假設這個基本電路單元處于中間步驟,即所有輸入都是同一個邏輯(都是1或都是0),若所有輸入都是0,那么4個與邏輯都進行0 AND 0操作,然后再輸入有效的常數漢明權重碼數據,則A1、A2和B1、B2各有一位從0翻轉到1。因此,在這個基本電路單元中,翻轉的晶體管數量總是一樣的。無論漢明碼的值是什么,基本單元的4個與門分別進行了1 AND 0、1 AND 1、0 AND 0和0 AND 1操作。因為4個與門的結構是相同的,不管A和B的輸入值是什么,這個基本單元的電特性都相同,所以DPA攻擊并不能從電特性中分析出輸入信號。表1根據晶體管的翻轉情況對基本單元的相同電特性進行了統計說明(假設先設置所有輸入為0)。

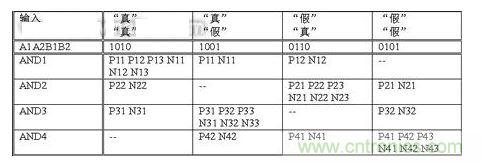

表1:無論輸入信號是什么,

基本電路單元中翻轉的晶體管數量保持恒定

在基本單元進行下一次運算之前,其所有輸入值需要重新設置為0,這個操作使同等數量的晶體管翻轉,攻擊者將無法從功耗分析上看出先前的輸入值。同樣,如果將所有輸入值設置為1也具有相同效果。本文把每次運算之間的設置初始值的操作狀態稱為“中間態”。

多級組合邏輯的設計

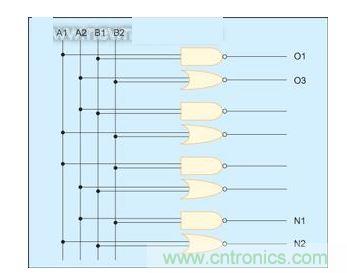

在實際電路中,多級的組合邏輯將串接在一起,即基本單元的輸出端連接到下一級基本單元的輸入端。在這種情況下,中間態必須能非常方便地在各級基本單元之間傳輸,以保證整個電路的不可攻擊性。圖3顯示了一種可傳輸中間態的防DPA攻擊的基本單元。

圖3:一種可傳輸中間態的防DPA攻擊的基本單元

這種基本單元可以級連起來,連接成復雜的數字組合邏輯。該基本單元與圖2描述的電路具有相同的邏輯特性,但當輸入0000或者1111時,它的輸出值是11或者00。輸出值11或者00能對下一級的基本單元進行置位或者清零,這就實現了中間態的傳輸。

[page]

當輸入是常數漢明權重碼時,該基本單元可實現NAND、AND、NOR和OR四個邏輯功能。輸出O1O2是NAND功能,輸出O2O1是AND功能,輸出N1、N2是NOR功能,輸出N2N1是OR功能。圖4所示的基本單元則可實現NOT邏輯。當輸入是常數漢明權重碼時,輸出是反相的漢明碼;當輸入進行置位或者清零,輸出是00或者11,也能實現中間態的傳輸。以上這五種邏輯足以組合成復雜的數字邏輯運算。

圖4:實現NOT邏輯的基本單元

防DPA攻擊的系統結構

前面介紹了組合邏輯防DPA攻擊的電路設計方法,現在將介紹時序邏輯防DPA攻擊的設計方法及防DPA攻擊的系統結構。

舉個例子,當電路傳輸的數據都是常數漢明權重碼時,輸入數據01給兩位寄存器,當這兩位寄存器的值是10時,兩位寄存器都會翻轉,而當兩位寄存器的值是01時,兩位寄存器都不會翻轉。這個不同點會把有用信息泄漏給DPA攻擊者。而在輸入數據之前,先把寄存器設置為00或11,那么當輸入數據是常數漢明權重碼時,無論輸入值是01還是10,都只有一個寄存器翻轉,從運算狀態到中間狀態也只有一個寄存器翻轉。這樣可有效防止寄存器在數據傳輸過程中的信息泄漏。

在有存儲器的電路中,存儲器在存儲0或者存儲1時有不同的電特性,如電流大小不同;同樣,存儲器在讀取0或者讀取1時也有不同的電特性,如電流大小不同。DPA攻擊者會利用這個特性對芯片進行分析,所以必須保證在對存儲器進行操作時有相同的電特性?,F在,由于系統傳輸的是常數漢明權重碼,所以在讀取存儲器的數據時,無論讀取的是什么值,都具有相同個數的1和相同個數的0。例如當數據線是8位時,每次傳輸數據都有4位0以及4位1。同樣,在存儲數據時,無論存儲的是什么值,只要是常數漢明權重碼,都將存儲相同個數的1和相同個數的0。這樣,在所有存儲器操作過程中都不會出現信息泄漏。

以上從組合邏輯、寄存器、存儲器、傳輸數據結構和中間狀態等幾個方面對防DPA攻擊的電路設計方法進行了介紹和說明,而組合邏輯基本單元、寄存器、存儲器等器件完全可以構成一個復雜的防DPA攻擊的電路。

為證明這種方法的有效性,對兩種智能卡芯片進行了對比。這兩種芯片都基于ISO/IEC7816協議,內部加密系統采用192位3DES來實現。一種芯片是采用普通的電路設計方法設計實現,另一種芯片在關鍵設計上采用了本文介紹的方法。用Cryptography Research 公司的DPA Workstation測試系統對前一種芯片進行分析,15分鐘內就破譯了芯片加密電路,取得密鑰。而對采用本方法實現的芯片,則無法用DPA Workstation測試系統進行分析,因為該測試系統是基于數據在加密算法的運行中出現的電流/電源變化來獲得密鑰,而現在,它無法從電流/電源變化中取得任何有效信息,自然也無法破譯芯片。