【導讀】在封裝內部添加IC組成振蕩電路的晶體元件稱為晶體振蕩器。本文為大家普及一下關于晶振振蕩電路設計的相關知識點。希望能幫助到大家。

晶片,石英晶體或晶體、晶振、石英晶體諧振器從一塊石英晶體上按一定方位角切下薄片。晶體振蕩器:在封裝內部添加IC組成振蕩電路的晶體元件稱為晶體振蕩器。

1 晶振的等效電氣特性

(1) 概念

[1] 晶片,石英晶體或晶體、晶振、石英晶體諧振器

從一塊石英晶體上按一定方位角切下薄片。

[2] 晶體振蕩器

在封裝內部添加IC組成振蕩電路的晶體元件稱為晶體振蕩器。

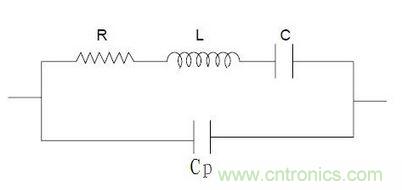

(2) 晶振的等效電路

Figure1. 晶振的等效電路

Figure 1展示了晶振等效的電路。R是有效的串聯電阻,L和C分別是電感和電容動態元件。CP 是晶振電極的分流電容。

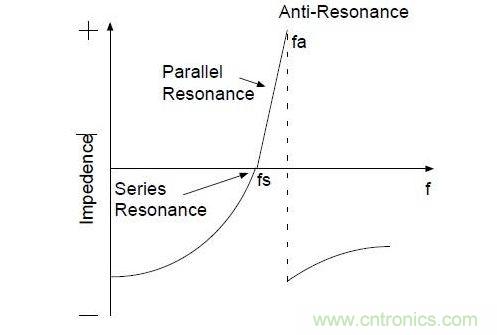

(3) 晶振等效電路的特殊狀態

Figure2是Figure 1電路中的阻抗頻率圖,不分析得出此圖規律的過程(原理)。

Figure2. 晶振的阻抗VS 頻率圖

[page]

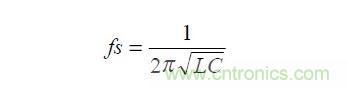

[1] 串聯諧振頻率

根據Figure 2,當晶振工作在串聯諧振(《電路基礎》)狀態(XC=XL)下時電路就似一個純電阻電路。串聯諧振的頻率為:

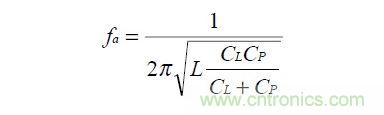

[2] 并聯諧振頻率

Figure 2中體現了隨著頻率小范圍的升高,Figure1所示電路出現了并聯諧振。此時的頻率為fa(不分析電路產生并聯諧振的過程)。

[3] 串聯諧振與并聯諧振之間的頻率并聯CL的并聯諧振

Figure1所示電路有兩個諧振點,以頻率的高低分其中較低的頻率為串聯諧振,較高的頻率為并聯諧振。由于晶體自身的特性致使這兩個頻率的距離相當的接近,在這個極窄的頻率范圍內(fs - fa),晶振等效為一個電感(不分析WHY),所以只要晶振的兩端并聯上合適的電容CL它就會組成新的并聯諧振電路。此時發生并聯諧振的頻率的計算公式為:

MX-COM的所有的晶振振蕩器都推薦使用晶振的并聯諧振模式。

2 晶振電路的設計

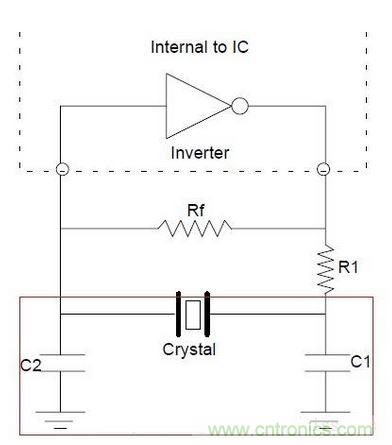

(1) 推薦的晶振振蕩器電路

Figure3. 晶振振蕩器設計電路

圖示中,沒在紅方框之內部分電路一般都被集成在芯片(如STM3210xxx)內部。若電阻部分沒有被集成在芯片內部,則需要考慮將電阻部分加入。Rf的值在500KΩ ~ 2MΩ。

[page]

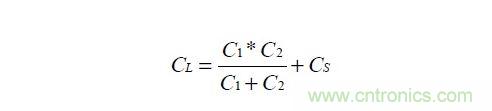

圖示的C1,C2就是為晶振工作在并聯諧振狀態下得到加載電容CL的電容。關于最優的加載電容CL的計算公式為:

其中Cs是來自板子的干擾電容值,5pf可以作為一個典型值被帶入以上公式中計算。

(2) 避免晶振振蕩器的不穩定與啟振問題

選擇合適的C1和C2的值就能夠滿足以上與CL的方程(整體的思路見3)。通常需要C1和C2的值近似相等。C1和/或C2的值較大時能夠增加頻率的穩定性,但會減少回路增益并且可能會引起整個晶振振蕩器的起振問題。

R1的主要被用來限制反相器(inverter)的輸出,以保證晶振不被過分驅動。R1和C1構成劃分電壓電路,C1和R1的取值要盡量使反相器的輸出靠近軌到軌(指器件的輸入輸出電壓范圍可以達到電源電壓)且使晶振的輸入要達到軌到軌的60%,通常的實踐是是R1的電阻與C1的容抗相等,如R1 約等于XC1。這使晶振的輸入是反相器輸出的一半。通常需要確保晶振分得的電壓要在晶振所能承受的范圍之內,過分的驅動晶振會損害晶振。使用晶振是要參考制造商的推薦。

理想狀況下,反相器會產生180°的相位偏移,但反相器固有的延遲會導致一個與這種延遲成某種比例的額外的的一個相位偏移。為了確保在在控制回路中產生360°的的相位偏移,需要使π網絡(回路)產生的相位偏移少于180°。調節R1的值就可以完成這個目標。在固定C1和C2的情況下,可以通過調節R1的值來更改閉環增益和相位偏移。在某些應用中,遇到上述兩種情況時R1也可被忽略。

一些IC將提到的這些器件(Rf,R1,C1,C2)都集成到了芯片內部,如此就可為晶振振蕩電路的設計者免去一些擔憂。在這種情況下只需要將晶振簡單的連接到芯片給出的兩個XTAL引腳上即可。

提示:

.選擇一個有效串聯電阻較小的晶振可以有利避免起振時的問題,且增加回路增益。

.縮短板上的布線路徑可以減少干擾電容(Cs),這將有利于減小起振問題,同時有利于晶振振蕩電路頻率的穩定性。

.為了確保晶振振蕩器起振良好及振蕩頻率的穩定性,需要在適用的溫度和電壓范圍測試晶振振蕩器電路,必要時更改各器件的值。

.優化R1值的推薦方式是提前計算出C1和C2的值并用一個分壓計代替R1,設置分壓計的初始值近似為XC1。在晶振起振和維持晶振振蕩器穩定頻率的條件下,必要時調整分壓計。

.要想設計出最好的晶振振蕩電路,聯系制造商了解晶振的精確的特性再根據以上指標來設計。

(3) 計算C1和C2的思路

根據MCU的系統時鐘(SYSCLK)或者與晶振振蕩器關聯的時鐘需求值(芯片會告知)依據fa的計算公式計算出CL,再有計算CL的公式和C1與C2近相等的原則得出C1和C2的值。

在為芯片設計晶振振蕩器的電路時,首先查看與晶振相連引腳內部都集成了哪些部分,Rf與R1是否還需要在外部設計。