【導讀】容性負載?是負載呈容性,還是帶容性的負載?呵呵,這不一個意思嘛,中國的語言,難怪老外覺得很難搞懂,自己人都被繞暈了。負載怎么會呈容性呢?在多負載的情況下負載怎么會呈容性呢?

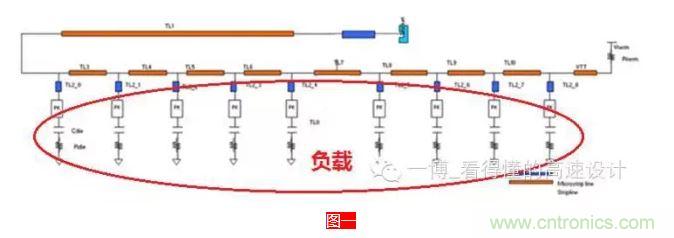

容性負載?是負載呈容性,還是帶容性的負載?呵呵,這不一個意思嘛,中國的語言,難怪老外覺得很難搞懂,自己人都被繞暈了。負載怎么會呈容性呢?這個主要是在多負載的情況下,如下圖一所示,由于分支和負載較多,不可避免的會增加過孔來連通信號,普通過孔是呈容性的,其次還有芯片封裝上的寄生電容(約0.33~0.44pF),另外還有Die上的寄生電容(約0.77~2.12pF),所有的這些電容會降低信號線的有效特征阻抗。

圖一

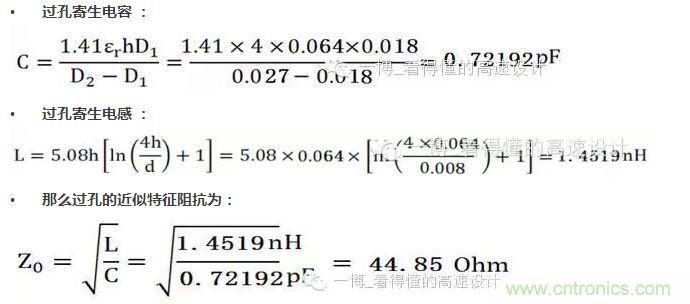

過孔為什么會呈現容性?這和其本身的結構及尺寸有關,請看下面的近似計算。

以8mil孔徑,18mil pad,27mil反焊盤,1.6mm通孔為例計算過孔的參數。

此公式是將過孔等效為傳輸線的模型來計算的,如果常規我們單端信號是50歐姆的特征阻抗,過孔的阻抗如上計算約為45歐姆,拉低了整體的特征阻抗,所以說呈現容性效應。

同樣,如果再考慮封裝電容及Die電容的容性,那么整個負載的有效阻抗就會更低于PCB的設計阻抗,這樣就會導致整體的阻抗不連續。

通常我們有兩種方法來進行容性負載的補償(相對于單端50歐姆的目標阻抗來說),其一是減小主干線路(變粗)的阻抗,其二是加大分支處(變細)的線路阻抗,使得整體的負載阻抗維持在50歐姆左右。

[page]

好了,口說無憑,讓我們來聯系下實際吧。

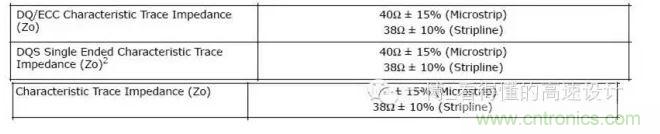

還是拿芯片行業的龍頭老大來舉例,如果大家經常看Intel的設計指導,就會看到他們關于DDR3的主干線路阻抗(40歐姆左右)控制都比50歐姆小,而且通常這樣的設計負載又很多(DIMM條就更不用說了),這個不正是降低主干線路阻抗的一種印證嘛!請看如下表所示。

出自Intel Romley PDG

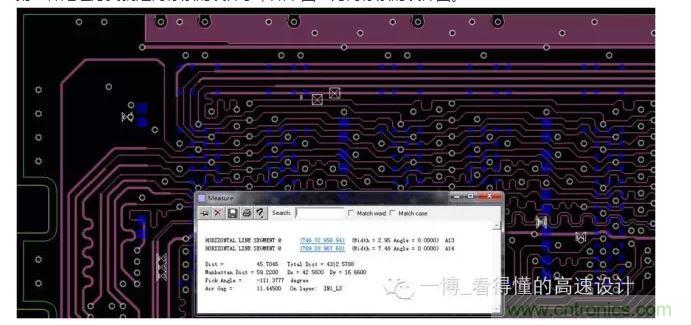

第二種處理方式就是內存條的設計了,如下圖二為內存條的設計圖。

圖二 內存條設計

從上圖可以看到,地址信號的主干線路線寬為7.5mil,而到了顆粒端就變成了3mil,除了布線密度上面的考慮外,主要還是為了補償容性負載。

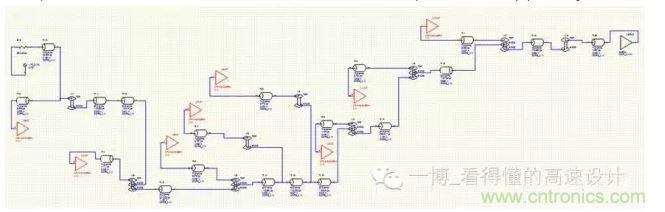

同時,高速先生也做了仿真來驗證容性負載補償是否真的有效,拓撲結構如下圖三所示。

圖三 仿真拓撲結構

[page]

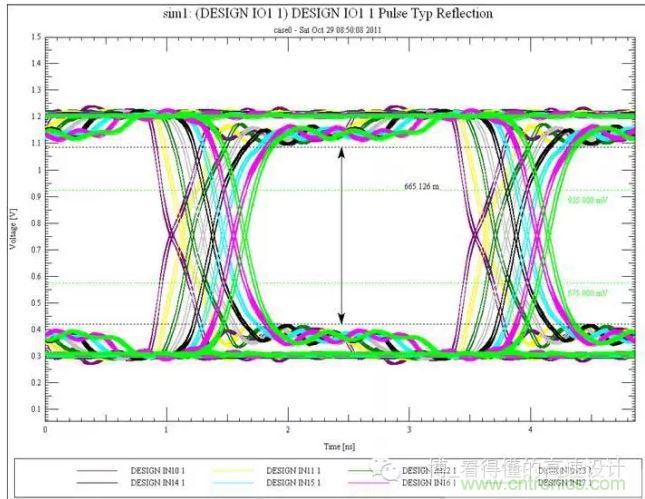

在正常控制PCB板上阻抗為50歐姆的情況下(不做容性負載補償),仿真波形如下圖所示。

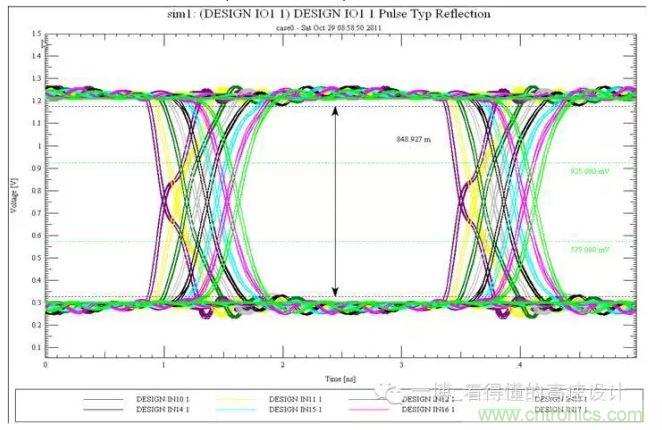

將主干線路的阻抗控制為42歐姆(有容性負載補償),仿真波形如下圖所示。

為了方便比較所以采用眼圖的方法,可知做了補償的眼圖有更大的眼高,兩者相差180mV左右,相當于提升了12%的系統裕量。