【導讀】對高速信號進行高分辨率的數字化處理需審慎選擇時鐘,才不至于使其影響模數轉換器(ADC)的性能。借助本文,我們將使讀者更好地理解時鐘抖動問題及其對高速ADC性能的影響。

對高速信號進行高分辨率的數字化處理需審慎選擇時鐘,才不至于使其影響模數轉換器(ADC)的性能。借助本文,我們將使讀者更好地理解時鐘抖動問題及其對高速ADC性能的影響。

我們將以凌力爾特(LTC)最新推出的高性能16位、160Msps的ADC LTC2209為例進行說明。LTC2209具有77.4dB的信噪比(SNR),100dB 基帶無寄生動態范圍(SFDR)。

與當今市場上的許多高速ADC一樣,LTC2209也使用采樣-保持(S&H)電路,該電路本質上是對ADC輸入的點取(Snapshot)。當采樣-保持開關閉合后,ADC輸入網絡被連至采樣電容。在開關打開的那一刻(1/2時鐘周期后),采樣電容上的電壓被記錄并保持。

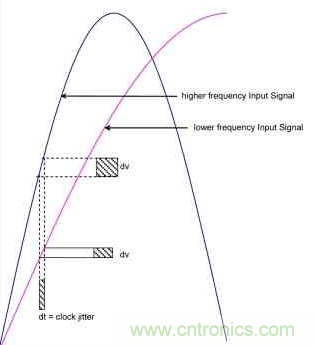

開關打開時間上的變異被稱為孔徑不確定性(aperture uncertainty),或稱為抖動,它將產生一個與抖動或輸入信號斜率成比例的誤差電壓。換句話,輸入頻率越快、幅值越高,則越易受時鐘源的影響。圖1顯示的是斜率與抖動的關系。

高速模數轉換器的性能分析及時鐘抖動會對其造成什么影響

鐘描述為“低抖動”已變得幾乎毫無意義。這是因為它對不同的關注者意味不同。對可編程邏輯供應商來說,30皮秒、甚至50皮秒都可被認為是低抖動的;相反的,根據輸入頻率的不同,高性能ADC需要的時鐘抖動應在1皮秒以內。

在頻譜的最高端將出現滿量程信號,否則與對最高頻率成分的簡單化處理不同,更精確地來講,采樣后信號的頻譜功率分布才是決定性因素。舉個簡化的例子,從DC到1MHz的均勻頻帶功率在1MHz的等值功率時比單頻或窄帶的靈敏度低6dB。

任何情況下,都有各種因素會造成抖動,除ADC本身內部的孔徑抖動外,還有振蕩器、各種頻率分割器、時鐘緩沖器和由耦合效應引入的任何噪音等其它多種因素。

C2209的內部孔徑抖動是70fsec(1fsec=10-15秒)。就LTC2209和LTC其它高速16位系列ADC所表現出的性能看,在某些采樣情況下,0.5皮秒的抖動(大多振蕩器供應商所能提供的最高指標)就可對SNR產生明顯影響。決定所需要的抖動性能的不是ADC,而是具體采樣情況。

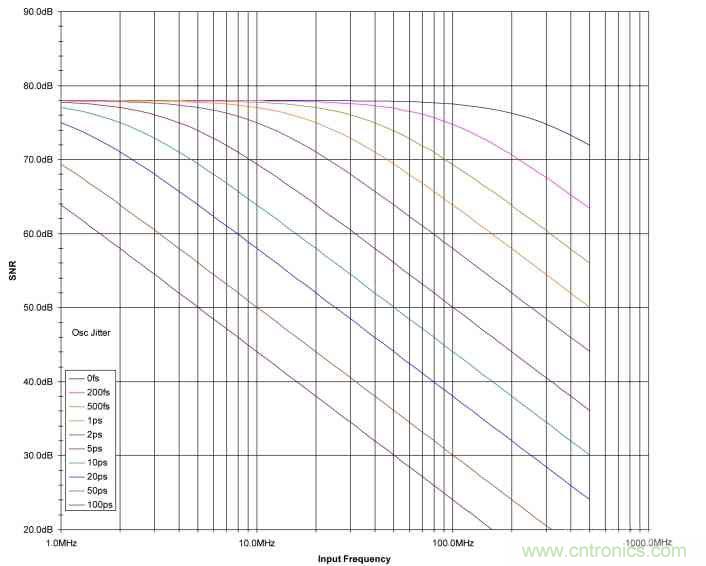

在140MHz輸入頻率下具備77dB SNR的ADC都需要相同的抖動性能,以便不折不扣地實現數據手冊上標注的SNR。就抖動性能來說,決定性因素是輸入頻率而非時鐘頻率。就LTC2209來說,帶10皮秒抖動的時鐘將在1MHz輸入頻率僅產生0.7dB的SNR損耗。在140MHz,SNR將被降低至41.1dB。

圖2顯示的是作為采樣輸入頻率函數的時鐘抖動對LTC2209的SNR的影響,它包括從完美時鐘到帶100皮秒抖動時鐘所逐漸增加的一系列時鐘曲線。在100皮秒,ADC的SNR在輸入僅為200kHz時就開始惡化。

時鐘抖動對SNR影響的理論極限是:

其中,fin是輸入頻率、s是以均方根(RMS)秒表示的抖動。

與抖動相關的噪聲功率與輸入功率(dBFS)成比例。隨著輸入電平的增高或降低,與抖動相關的噪聲成分也相應改變。例如,若我們在70MHz IF有-1dBFS的輸入信號并用帶1皮秒抖動的時鐘進行采樣,則我們可預期一個68dBFS的SNR。在-5dBFS,與抖動相關的噪聲成分將下降4dB、達72dBFS。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱聯系小編進行侵刪。