【導(dǎo)讀】許多數(shù)據(jù)采集、工業(yè)控制和儀表應(yīng)用都需要超高速模數(shù)轉(zhuǎn)換器 (ADC),而逐次逼近寄存器 (SAR) 轉(zhuǎn)換器則能完全滿足這一要求。然而,我們必須確保 SAR 轉(zhuǎn)換器周圍的外部電路也能勝任這一任務(wù),才能確保成功的轉(zhuǎn)換結(jié)果。

許多數(shù)據(jù)采集、工業(yè)控制和儀表應(yīng)用都需要超高速模數(shù)轉(zhuǎn)換器 (ADC),而逐次逼近寄存器 (SAR) 轉(zhuǎn)換器則能完全滿足這一要求。然而,我們必須確保 SAR 轉(zhuǎn)換器周圍的外部電路也能勝任這一任務(wù),才能確保成功的轉(zhuǎn)換結(jié)果。對于 SAR 轉(zhuǎn)換器來說,需要特別注意的關(guān)鍵端子是其模擬信號輸入端——如果不加以重視,這些輸入引腳會產(chǎn)生穩(wěn)定性問題和電容電荷"反沖",從而導(dǎo)致轉(zhuǎn)換不準確并延長信號采集時間。

在 SAR 轉(zhuǎn)換器應(yīng)用中,精確控制輸入信號的解決方案在于運算放大器(運放)的驅(qū)動。如搭配適當?shù)妮敵鲭娮韬碗娙葜担@些器件就是高分辨率、16 位和 20 位 SAR 轉(zhuǎn)換器系統(tǒng)的高精度穩(wěn)健解決方案的基礎(chǔ)。

本文將簡要討論實現(xiàn)穩(wěn)定準確的 SAR ADC 轉(zhuǎn)換的相關(guān)問題。然后,介紹一款合適的運放來驅(qū)動 SAR ADC,并說明如何實現(xiàn)必要的輸入驅(qū)動電路。我們將以 Analog Devices 的解決方案為例進行說明。

SAR ADC 輸入電路

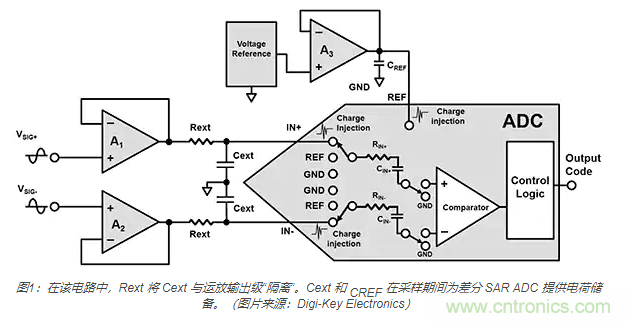

SAR ADC 驅(qū)動電路具有將 ADC 與其信號源隔離的運算放大器(A1 和 A2)(圖1)。在該電路中,Rext 通過"隔離"放大器的輸出級與 ADC 容性負載(CIN+ 和 CIN-)和 Cext 隔離來保持穩(wěn)定。Cext 和 CREF 為 ADC 提供了一個近乎完美的輸入源,可以吸收來自 IN+、IN- 和 REF 輸入端子的開關(guān)電荷注入。輸入端子 (IN+, IN-) 在轉(zhuǎn)換器的采集期間跟蹤輸入信號 (VSIG+, VSIG-) 的電壓,為 ADC 輸入采樣電容 CIN+ 和 CIN- 充電。

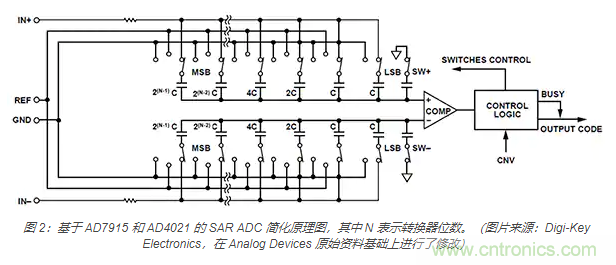

以 Analog Device 的 AD7915 (16 位)和 AD4021(20 位)SAR ADC 為例觀察 ADC 內(nèi)部,可以看到該器件使用了電荷再分配數(shù)模轉(zhuǎn)換器 (DAC)。容性 DAC 有兩個相同的二元加權(quán)電容陣列。這兩個電容陣列連接非反相和反相比較器輸入端(圖 2)。

在采集階段,輸入端(IN+ 和 IN-)切換到電容陣列。此外,SW+ 和 SW- 閉合,將最小有效位 (LSB) 電容與地 (GND) 相連。在這種狀態(tài)下,電容陣列成為采樣電容,采集 IN+ 和 IN- 模擬信號。采集階段結(jié)束后,控制邏輯(右側(cè))的 CNV 輸入變?yōu)楦唠娖剑瑔愚D(zhuǎn)換階段。

轉(zhuǎn)換階段開始時,先斷開 SW+ 和 SW-,將兩個電容陣列切換到 GND。在這種配置下,捕獲的 IN+ 和 IN- 差分電壓會導(dǎo)致比較器變得不平衡。電荷再分配 DAC 在 GND 和 REF 之間有條不紊地將電容器陣列的每個元件從最重要的位 (MSB) 切換到 LSB。比較器輸入按二元加權(quán)電壓步長來變化 (VREF/2N-1, VREF/2N-2...VREF/4, VREF/2)。控制邏輯將開關(guān)從 MSB 切換為 LSB,使得比較器回到平衡狀態(tài)。這個過程結(jié)束后,ADC 返回采集階段,控制邏輯產(chǎn)生 ADC 輸出代碼。

輸入電荷注入、電路穩(wěn)定性和驅(qū)動 AD7915 ADC

轉(zhuǎn)換過程的關(guān)鍵是獲取準確的輸入信號電壓。當驅(qū)動放大器準確地向輸入電容器 CIN+ 和 CIN- 進行充電時,ADC 數(shù)據(jù)轉(zhuǎn)換過程就會順利進行,同時保持穩(wěn)定,直至 ADC 采集時間結(jié)束。對設(shè)計者來說,問題在于 ADC 的輸入端引入了一個電容 (CIN+, CIN-) 以及需要驅(qū)動放大器進行管理的開關(guān)噪聲或"反沖"電荷注入。

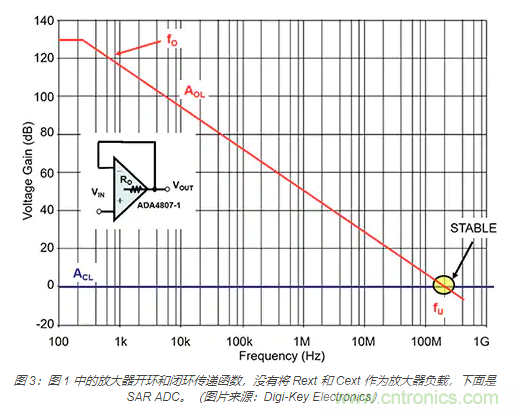

放大電路 Bode plot 可以快速估算電路穩(wěn)定性。Bode plot 工具可以近似地描述放大器的開環(huán)和系統(tǒng)閉環(huán)增益?zhèn)鬟f函數(shù)的大小(圖 3)。

y 軸量化了放大器電路的開環(huán)增益 (AOL) 和閉環(huán)增益 (ACL),其中放大器的 AOL 曲線從 130 分貝 (dB) 開始,閉環(huán)增益 ACL 等于 0dB。沿 X 軸的單位以對數(shù)形式量化了從 100 赫茲 (Hz) 到 1 千兆赫茲 (GHz) 的開環(huán)和閉環(huán)增益頻率。

在圖 3 中,放大器在大約 220Hz (fO) 時的直流開環(huán)增益以 -20dB/十倍頻程的速度從 130dB 下降。隨著頻率的增加,這種衰減在持續(xù)并在大約 180 兆赫茲 (MHz) 時跨過 0dB。由于這條曲線表示單極系統(tǒng),所以分頻器頻率 fU 等于單位增益穩(wěn)定放大器的增益帶寬乘積 (GBWP)。該圖代表一個穩(wěn)定的系統(tǒng),因為 AOL 和 ACL 的截止率是 20dB/十倍頻程。

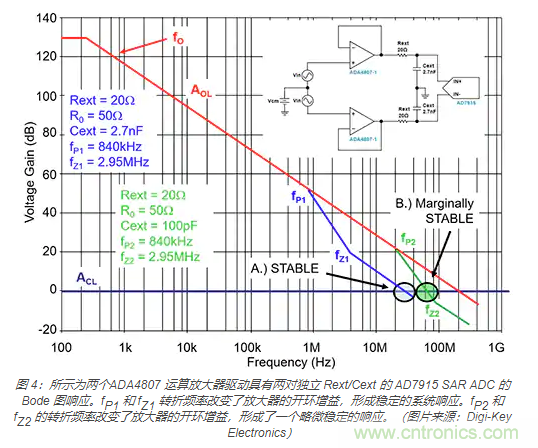

加入 Rext 和 Cext 以及 SAR ADC 后,通過創(chuàng)建系統(tǒng)零點和極點來修改放大器電路(圖 4)。該系統(tǒng)包括一個 16 位、每秒 1 兆次 (MSPS) 的 AD7915 差分 PulSAR ADC 和一個 180 MHz、軌至軌輸入/輸出 ADA4807-1 放大器,該器件由 Analog Devices 提供。由于存在 30 皮法 (pF)(典型值)的 ADC 輸入電容負載,放大器和 ADC 的組合需要 Rext。該電路還需要 Cext 作為充電筒,在 ADC 輸入端提供足夠的電荷,以準確匹配輸入電壓。

如圖 4 所示,由于電路在初始采集時 ADC 的電容負載和 ADC 的開關(guān)電荷注入,有可能發(fā)生振蕩。Rext/Cext 放大器輸出元件所產(chǎn)生的額外極點和零點保證了系統(tǒng)穩(wěn)定,所以開環(huán)和閉環(huán)增益曲線交點大于 20dB/十倍頻程,使相位裕度小于 45°。這種配置與 fP2 和 fZ2 一起構(gòu)成一個不穩(wěn)定電路。

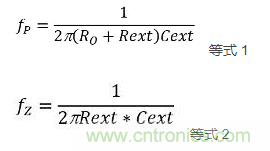

為避免不穩(wěn)定,在評估電路中帶有 Rext 和 Cext 的放大器開環(huán)增益曲線時,設(shè)計人員需要考慮放大器的開環(huán)輸出電阻 RO 的影響。阻值為 50 歐姆 (W) 的RO 與 Rext、Cext 的組合通過引入一個極點(fP,公式 1)和一個零點(fZ,公式 2)來修正開環(huán)響應(yīng)曲線。RO、Rext 和 Cext 的值決定了 fP 的轉(zhuǎn)折頻率。Rext 和 Cext 的值決定了零轉(zhuǎn)折頻率 fZ。

fP 和 fZ 的計算結(jié)果是:

fP1 = 842 kHz

fZ1 = 2.95 MHz

其中:RO = 50 W

Rext = 20 W

Cext = 2.7 納法拉 (nF)

fP2 = 22.7 MHz

fZ2 = 79.5 MHz

其中:RO = 50 W

Rext = 20 W

Cext = 0.1 nF

上述 fP1 和 fZ1 的值使 AD7915 和 ADA4807-1 成為一個穩(wěn)定的系統(tǒng)。

驅(qū)動 Easy Drive AD4021 SAR ADC

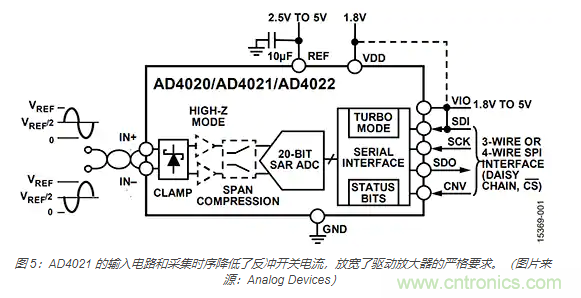

AD7915 的替代產(chǎn)品是 AD4021 20 位 1 MSPS Easy Drive SAR 轉(zhuǎn)換器。AD4021 器件系列將輸入反沖和輸入電流顯著降低至 0.5 微安 (μA)/MSPS。Easy Drive 器件的特點是能降低功耗和信號鏈復(fù)雜性。

AD4021 的模擬輸入端采用了能夠降低典型開關(guān)式電容 SAR 輸入非線性電荷反沖的電路。因為減少了反沖并延長了采集階段,因此可以使用較低帶寬、較低功率的驅(qū)動放大器(圖 5)。

減少反沖并延長采集時間,也使得輸入電阻電容 (RC) 濾波器中的 Rext 電阻值增大,Cext 電容相應(yīng)減小。這種較小的 Cext 放大器負載組合提高了穩(wěn)定性,降低了功耗。

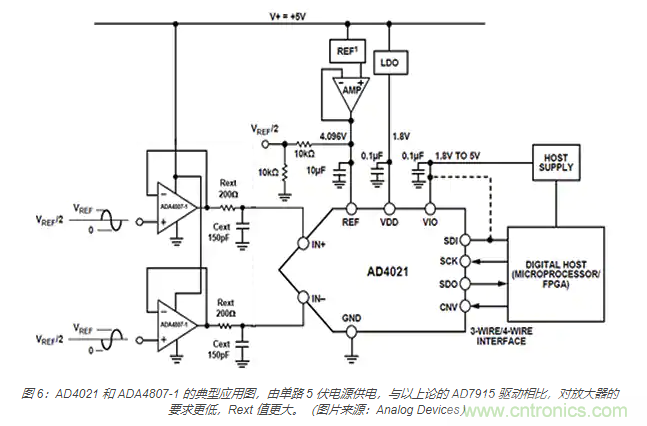

使用單路 5 伏電源的 AD4021 的推薦連接圖似乎具有類似電路圖。但對放大器的要求降低了,Rext/Cext(R 和 C)的值更小(圖 6)。

圖 6 中,基于 SAR 的 AD4021 也采用了電荷再分配采樣 DAC。ADC 有一個板載轉(zhuǎn)換時鐘和串行時鐘。因此,轉(zhuǎn)換過程不需要同步時鐘 (SCK) 輸入。這種時鐘配置可以延長采集時間,通過為輸入信號提供更長的時間使其建立至最終值,從而提高精度。

AD7915 和 AD4021 的驅(qū)動放大器主要考慮的是噪聲,因為放大器/Rext/Cext 組合必須從滿量程階躍到 16 位水平 (0.0015%, 15ppm) 的 AD7915,以及 20 位水平 (0.00001%, 1ppm) 的 AD4021。

為了保持 AD7915 和 AD4021 的信噪比( SNR) 性能,驅(qū)動放大器的噪聲必須小于 ADC 噪聲的三分之一。AD4021 的噪聲為 60 微伏有效值 (mVrms),這就要求放大器/Rext/Cext 組合的噪聲小于 20mVrms。AD4021 的噪聲為 31.5 mVrms,這就要求放大器/Rext/Cext 組合的噪聲小于10.5 mVrms。

Analog Devices 的精密 ADC 驅(qū)動器工具可幫助設(shè)計人員快速計算出正確的 Rext 和 Cext 值。通過選定的驅(qū)動器和 ADC,該工具可以模擬電路的建立時間、噪聲和失真行為。

結(jié)語

SAR ADC 將繼續(xù)在超高速數(shù)據(jù)采集、工業(yè)控制和儀器儀表應(yīng)用中占據(jù)主導(dǎo)地位。然而,我們需要考慮這類器件的外部輸入電路——驅(qū)動放大器和輸入濾波器,以適應(yīng)潛在的開關(guān)電荷注入和放大器穩(wěn)定性問題。

大多數(shù) SAR 轉(zhuǎn)換器(如 AD7916 和 AD4021)精確控制輸入信號的解決方案都依賴運放驅(qū)動器,如本示例中的 ADA4807-1。如圖所示,這類器件在適當?shù)妮敵鲭娮韬碗娙葜档闹С窒滦纬梢粋€堅實的基礎(chǔ),然后在此基礎(chǔ)上建立一個高精度、穩(wěn)健、高分辨率、16 位或 20 位 SAR 轉(zhuǎn)換器系統(tǒng)。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請電話或者郵箱聯(lián)系小編進行侵刪。