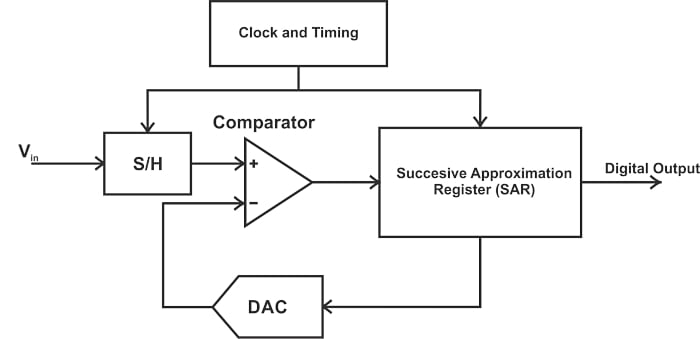

【導讀】ADC 是基于多種不同電路架構設計的復雜系統,例如閃存、SAR、Delta-Sigma (ΔΣ)和流水線結構。根據架構和特定電路實現,不同的電路元件可能是非線性的主要來源。盡管有多種設計,但我們仍然可以認識到在高速 ADC 中增加 SFDR 的兩個主要限制,即 S/H 電路和 ADC 的編碼器部分。為了更好地理解這一點,請考慮圖 3 中所示的 SAR ADC 框圖。

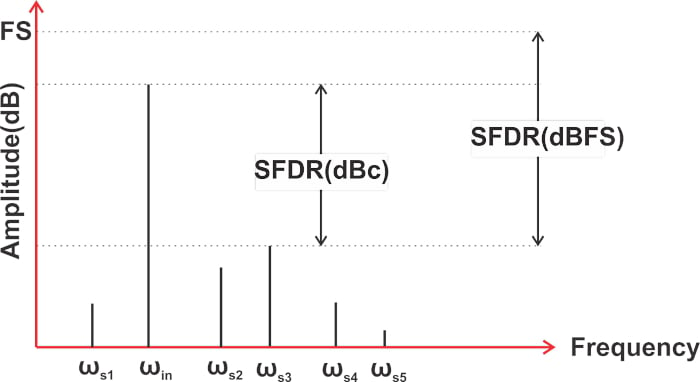

有多種不同的規格可用于表征電路線性度。SFDR 指標是一種常用的規范。該指標定義為所需信號幅度與感興趣帶寬內雜散的比率(圖 1)。

圖1. 顯示 SFDR 指標的圖表。

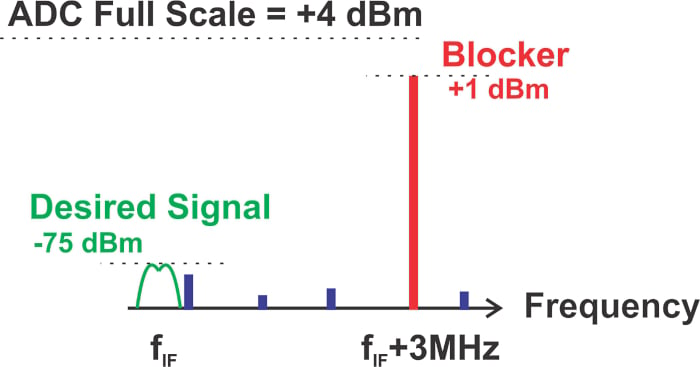

對于 ADC,SFDR 展示了 ADC 如何在存在大信號的情況下同時處理小信號。作為一個例子,考慮一個接收器應用程序。假設 ADC 輸入由 +1 dBm 阻塞信號和 -75 dBm 所需信號組成。在這種情況下,由于ADC 非線性,大阻塞器可能會在 ADC 輸出處產生不需要的雜散。這些不需要的雜散由圖 2 中的紫色組件顯示。

圖2. 該圖以紫色顯示不需要的雜散。

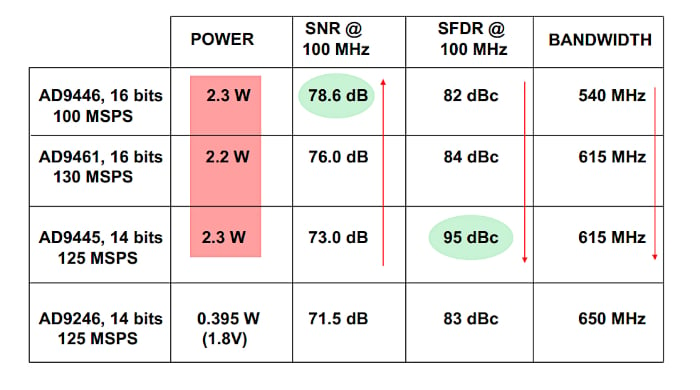

如果雜散足夠接近所需信號并且足夠大,則可能會將 SNR 降低到不可接受的水平。當今通信系統的嚴格要求可能需要 95 dB 范圍內的高 SFDR 值。然而,普通 ADC 無法提供這種水平的線性度。下面的表 1 比較了 Analog Devices 的四種高性能 ADC 的一些關鍵參數,應該可以幫助您了解高性能 ADC 的 SFDR 范圍。

表 1. 四種高性能 ADC 的關鍵參數。使用的數據由Analog Devices提供

此外,該表還強調了 SNR 和 SFDR 指標之間的權衡。對于該表中的前三個 ADC,它們使用相同的 IC 技術并具有相同的功耗,因此 SFDR 和 SNR 之間存在反比關系。我們將在本文稍后討論這種權衡的起源。在此之前,我們先回答一個重要問題:在高速 ADC 中提高 SFDR 的主要限制是什么?

ADC 中的靜態和動態線性

ADC 是基于多種不同電路架構設計的復雜系統,例如閃存、SAR、Delta-Sigma (ΔΣ)和流水線結構。根據架構和特定電路實現,不同的電路元件可能是非線性的主要來源。盡管有多種設計,但我們仍然可以認識到在高速 ADC 中增加 SFDR 的兩個主要限制,即 S/H 電路和 ADC 的編碼器部分。為了更好地理解這一點,請考慮圖 3 中所示的 SAR ADC 框圖。

圖3. SAR ADC 框圖。

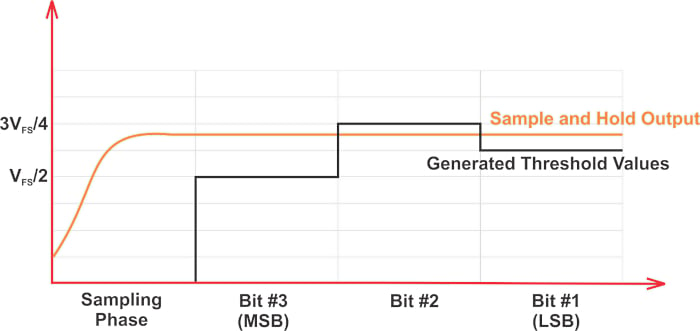

SAR數字化算法的步是采樣階段,在此期間S/H獲取輸入值。該樣本將在整個轉換階段保留。在轉換階段,所采集的樣本會連續與適當的閾值電平進行比較,以找到輸入的數字等效值。為了確定輸出的每一位,需要一個時鐘周期。假設采樣階段也需要 1 個時鐘周期,則 N 位 SAR ADC 需要 N + 1 個時鐘周期。圖 4 顯示了 3 位 SAR ADC 的 S/H 輸出和閾值波形。

圖4. 3 位 SAR ADC 的 S/H 輸出和閾值波形。

這里重要的一點是,對于給定的轉換階段,無論輸入頻率是多少,S/H 之后的電路組件都可以理想地使用直流信號。因此,SAR ADC 的比較器或內部DAC(數模轉換器)內的任何非線性 都不會隨輸入頻率而變化。我們可以說 ADC 編碼器部分的非線性影響了系統的靜態(或直流)非線性。靜態非線性的特征是ADC 傳遞函數中的DNL(微分非線性)和INL(積分非線性)誤差。

S/H 非線性怎么樣?與有效處理直流信號的編碼器部分不同,S/H“看到”交流信號。我們將在下一節中討論 S/H 非線性的很大一部分如何隨輸入頻率而變化。因此,S/H 決定了 ADC 的動態(或交流)線性度。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀:

為狀態監控選擇MEMS加速度計時,有這些關鍵但經常被忽視的參數