【導讀】半導體產品老化是一個自然現象,在電子應用中,基于環境、自然等因素,半導體在經過一段時間連續工作之后,其功能會逐漸喪失,這被稱為功能失效。半導體功能失效主要包括:腐蝕、載流子注入、電遷移等。其中,電遷移引發的失效機理最為突出。技術型授權代理商Excelpoint世健的工程師Wolfe Yu在此對這一現象進行了分析。

前言

半導體產品老化是一個自然現象,在電子應用中,基于環境、自然等因素,半導體在經過一段時間連續工作之后,其功能會逐漸喪失,這被稱為功能失效。半導體功能失效主要包括:腐蝕、載流子注入、電遷移等。其中,電遷移引發的失效機理最為突出。技術型授權代理商Excelpoint世健的工程師Wolfe Yu在此對這一現象進行了分析。

1、背景

從20世紀初期第一個電子管誕生以來,電子產品與人類的聯系越來越緊密,特別是進入21世紀以來,隨著集成電路的飛速發展,人們對電子產品的需求也變得愈加豐富。隨著電子產品的普及,電子產品失效率越來越高,質量變差,新產品不耐用。

由于產品失效率的提高,許多學者參與到半導體失效分析的研究中。經過大量研究分析和仿真,學者總結出:由于電流的作用,導致導線中的金屬原子與電子通過摩擦產生電遷移位移現象所引發的失效是電子產品失效模式的主要因素之一。電遷移滿足失效分布函數曲線,產品失效模式與產品工藝、工作溫度關系密切。

2、相關理論

電遷移現象主要發生在半導體在通電狀態下,由于電場作用,原子在與電子流的帶動下,由于摩擦,產生移位現象,這一現象被稱為電遷移。

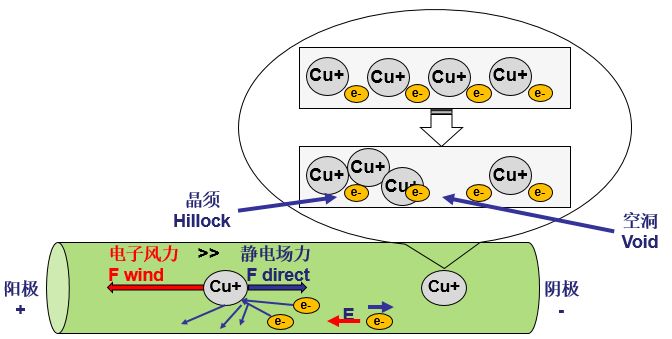

圖 1. 電遷移作用力引發半導體失效原理

如圖所示,在電場作用下,半導體在導通過程中,正電荷會同時受到靜電場力和電子高速運動沖擊所產生的風力作用。

由于電流密度增大,電子產生的風力會大于靜電場力,從而導致正電荷——也就是金屬原子,產生移位,這一現象稱為電遷移效應或電遷移現象。經過長期積累,半導體的部分連接就會形成不連貫的晶須(Hillock)或空洞(Void),最終導致半導體元器件失效。

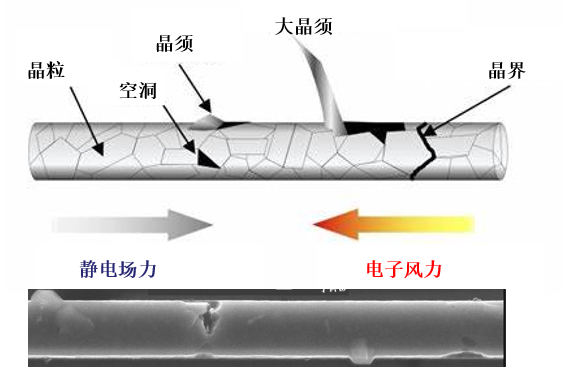

圖 2.電遷移作用失效示意圖

James R.Black最早在1967年提出基于電遷移引起平均失效時間(MTTF)的數據擬合經驗模型,為失效分析具有里程碑的意義。

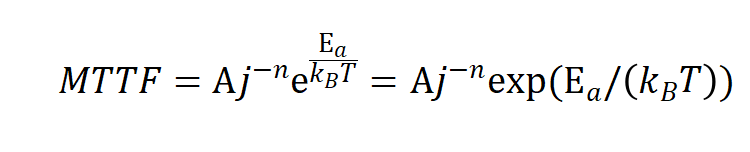

按照Black模型公式:

半導體元器件的失效機理與材料、電子碰撞間隔平均自由時間、有效散射橫截面積的因素常量A,電流密度j,絕對溫度T等因素相關。Blench和Korhonen等人進一步對電遷移物理模型進行完善。半導體元器件的失效機理單元模型壽命可靠度函數符合歐拉公式。

根據以上公式,電流密度越大,半導體元器件的響應速度就快,元件壽命就會越短,反之,元件的壽命就會增長。要滿足半導體元器件的響應速度,則半導體就需要較高的參雜度,另一方面,通過摻雜不同的材料、調整有效散射橫截面積等因素也會對芯片的壽命產生影響。

3、常規解決方案

(1) 報廢機制

企業通常利用產品生命周期管理方式,通過對產品生命周期進行分析,為產品設計一個報廢界定時間。在汽車、水電氣表等行業采用這種方式比較常見。

(2) 系統冗余

在保障性系統設計中,企業一般在報廢機制的基礎之上,還會通過采用雙備份冗余設計、或者K/N表決冗余,并加上系統修復的方式進行系統設計。

4、技術源頭控制

(1) 工藝控制理論

根據Black模型理論,當半導體采用寬線徑工藝,橫截面積較大時,其芯片壽命會變長,產品平均失效時間MTTF會相對拉得更長。這也從側面解釋了為什么傳統工藝設計出來的產品可靠性更高。

(2) 差異化技術控制方法

在芯片原理設計中,采用不同的拓撲架構模型,通過差異化技術實現不同的控制方法也很常見,比如采用CMOS基本單元替代TTL基本單元、采用恒流源替代恒壓源來完成不同的產品拓撲模型。在ADC、DAC、運算放大器、比較器等模型設計中十分常見。

在一些設計場合,通過調整芯片輸入閾值,降低芯片靈敏度,或通過控制芯片切換頻率,降低電流密度,達到提高產品可靠性的目的。

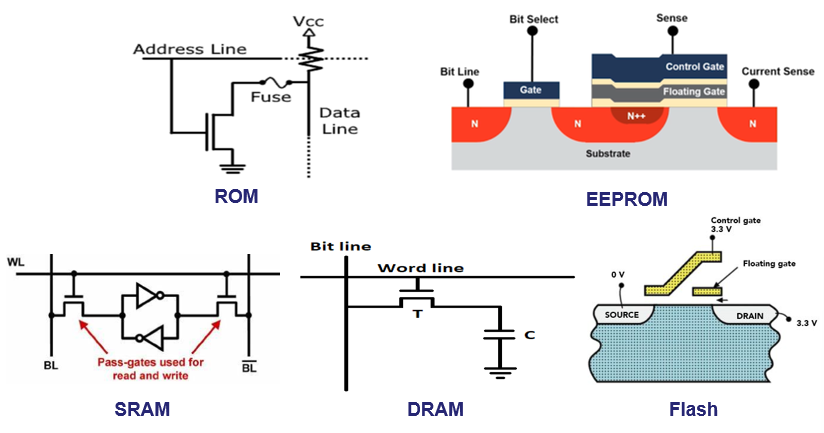

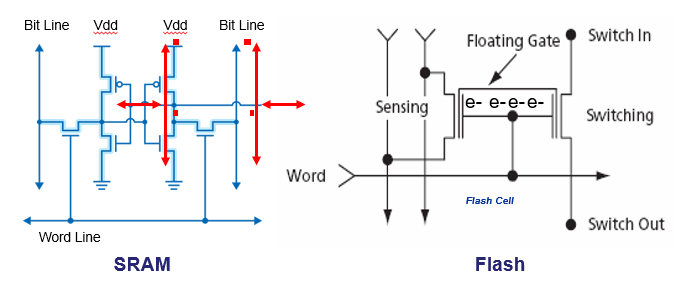

在核心處理芯片模型設計中,根據不同的應用場景,為了追求產品處理速度和可靠性,通常會采用不同的工藝模型進行芯片架構設計,比如從CMOS衍生出來的SRAM、DRAM、ROM、EEPROM、Flash等工藝用于不同的處理器產品架構中,會達到出不同的可靠性效果。

圖 3.不同工藝模型芯片單元架構

ROM工藝的處理器是一種非常古老的工藝產品,只能燒錄一次,雖然在某些應用場景還依然被大量使用。但在目前主流的產品方案應用中,基于SRAM和Flash工藝的MCU、MPU或FPGA處理器占據了絕大多數應用場景。

5、Microchip高可靠性Flash FPGA介紹

SRAM工藝的處理器是通過CMOS內部管道切換的方式工作,其產品處理速度較高,被眾多用戶接受。但是,CMOS工藝有一個致命缺陷,由于工藝原因,伴隨CMOS工藝制成芯片產生米勒效應極其容易受到外界干擾,產生翻轉。另外,CMOS在翻轉過程中,內阻變小,電流密度過大,芯片長期在高電流密度下工作,會加速產品老化時間。

除了基于傳統CMOS的SRAM處理器之外,Microchip推出了一種基于疊柵MOS工藝的Flash架構FPGA處理器。

圖4.Flash架構FPGA與SRAM架構FPGA的差別

Microchip的FPGA 產品范圍覆蓋從低端到中端應用,其產品特點以抗單粒子翻轉、安全、低功耗和上電即工作著稱,廣泛應用于通信、國防和航空、工業嵌入式產品。Microchip 目前主推三大系列 FPGA:

支持5K-150K LE(Logic Elements)具有大量資源的低密度器件的IGLOO?2 系列;

支持5K-150K LE具有大量資源和 32 位硬核處理器內核(ARM Cortex-M3)的SmartFusion?2 SoC系列;

以及采用 28 納米工藝技術實現, 支持25K - 480K LE的高性能PolarFire? FPGA 和 PolarFire? SoC系列(Hard 5-Core RISC-V 600MHZ CPU)。

這三大系列FPGA除了具有抗干擾、低功耗、上電啟動的特征外,還具有強大的DSP/數學模塊(18x18乘法器),可用于當前熱門的AI市場。

Microchip的這款Flash架構的FPGA最大的一個特點是電流密度小、抗干擾能力強、動態切換不會出現電流波動,基于其低功耗的特點,可大大延長產品使用壽命。非常適合應用在高可靠性、低失效率應用場合,能高效改善因電遷移引發的半導體失效問題。其授權代理商Excelpoint世健可提供技術支持和指導。

關于世健——亞太區領先的元器件授權代理商

世健是完整解決方案的供應商,為亞洲電子廠商包括原設備生產商(OEM)、原設計生產商(ODM)和電子制造服務提供商(EMS)提供優質的元器件、工程設計及供應鏈管理服務。多次被權威雜志和行業機構列入全球領先分銷商榜單。

世健與供應商及電子廠商緊密協作,為新的科技與趨勢作出定位,并幫助客戶把這些最先進的科技揉合于他們的產品當中。世健分別在新加坡、中國及越南設有研發中心,專業的研發團隊不斷創造新的解決方案,幫助客戶提高成本效益并縮短產品上市時間。世健研發的完整解決方案及參考設計可應用于工業、無線通信及消費電子等領域。

世健擁有超過35年歷史、逾700名員工,業務擴展至亞太區的49個城市和地區,遍及新加坡、馬來西亞、泰國、越南、中國、印度、印度尼西亞、菲律賓及澳大利亞等十多個國家。1993年,世健在香港設立區域總部——世健系統(香港)有限公司,正式開始發展中國業務。目前,世健在中國擁有十多家分公司和辦事處,遍及中國主要大中型城市。憑借專業的研發團隊、頂尖的現場應用支持以及豐富的市場經驗,世健在中國業內享有領先地位。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀:

創邁思、維信諾和意法半導體推出經濟、安全的隱形手機人臉認證系統