【導讀】"時間至關重要"——這個古老的慣用語可以應用于任何領域,但當應用于現實世界信號的采樣時,它是我們工程學科的支柱。當嘗試降低功耗、實現時序目標并滿足性能要求時,必須考慮測量信號鏈選擇何種ADC架構類型:∑-Δ還是逐次逼近寄存器(SAR)。一旦選擇了特定架構,系統設計人員便可創建所需的電路以獲得必要的系統性能。此時,設計人員需要考慮其低功耗精密信號鏈的最重要時序因素。

"時間至關重要"——這個古老的慣用語可以應用于任何領域,但當應用于現實世界信號的采樣時,它是我們工程學科的支柱。當嘗試降低功耗、實現時序目標并滿足性能要求時,必須考慮測量信號鏈選擇何種ADC架構類型:∑-Δ還是逐次逼近寄存器(SAR)。一旦選擇了特定架構,系統設計人員便可創建所需的電路以獲得必要的系統性能。此時,設計人員需要考慮其低功耗精密信號鏈的最重要時序因素。

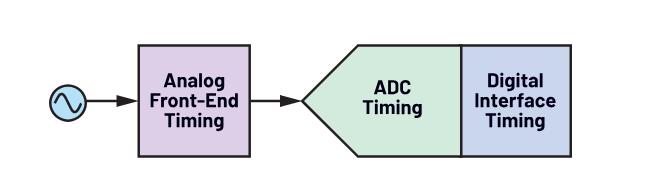

圖1. 信號鏈時序考量

需要高速度:低功耗信號鏈選擇SAR型還是∑-Δ型?

過去,當探索低功耗系統時,設計人員會選擇∑-Δ ADC來實現對緩慢移動信號的較高精度測量。SAR被認為更適用于需要轉換較多通道的高速測量,但新型SAR(如 AD4630-24 )正在進入傳統上使用∑-Δ ADC的高精度領域,因此以上說法并不是硬性規定。關于ADC架構的實際例子,我們來看兩款低功耗產品并考慮與ADC信號鏈架構相關的時序:AD4130-8 ∑-Δ ADC和 AD4696 SAR ADC,如表1所示。

表1. 超低功耗ADC

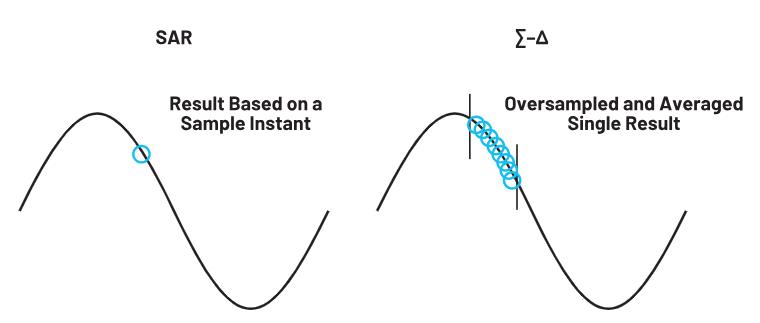

SAR轉換器對輸入進行采樣,在已知時間點捕獲信號電平。初始采樣(和保持)階段之后是轉換階段。獲取結果所需的時間很大程度上取決于采樣頻率。

不同技術獲取轉換結果的方式有所不同,SAR產品文檔使用的概念是采樣頻率(fSAMPLE),而∑-Δ產品的數據手冊使用輸出數據速率(ODR)。當相對于時間詳細討論這些架構時,我們會引導讀者區分二者。

圖2. SAR (?SAMPLE)與∑-Δ (ODR)的比較

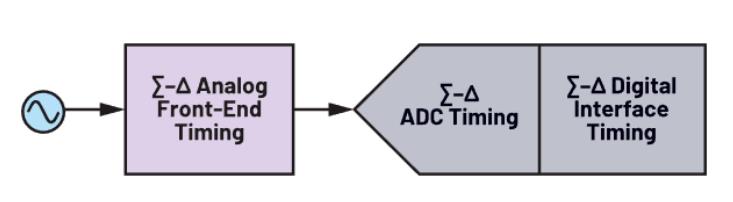

如果選擇的ADC是∑-Δ型而非SAR型,則需要考慮一組特定的時序因素。查看信號鏈時,需要探索的主要方面是模擬前端時序、ADC時序和數字接口時序,如圖1所示。

我們將分別探討這三個模塊,從模擬前端(AFE)開始。AFE可能因設計類型而異,但有一些共同方面適用于大多數電路。

圖3. AFE ∑-Δ時序考量

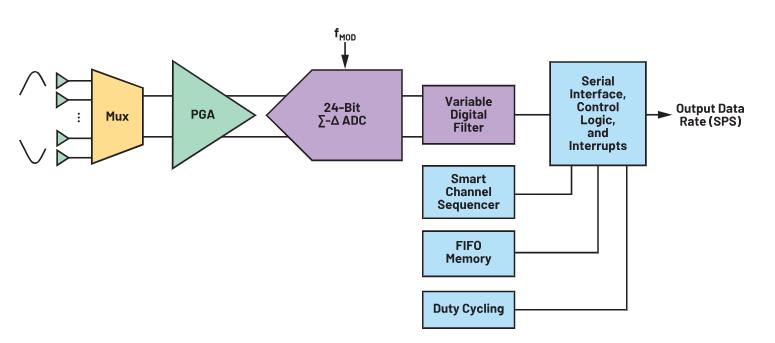

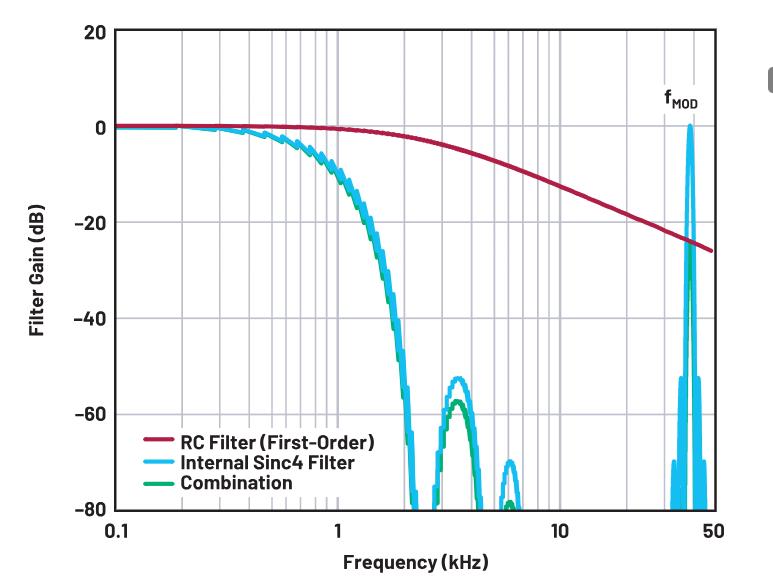

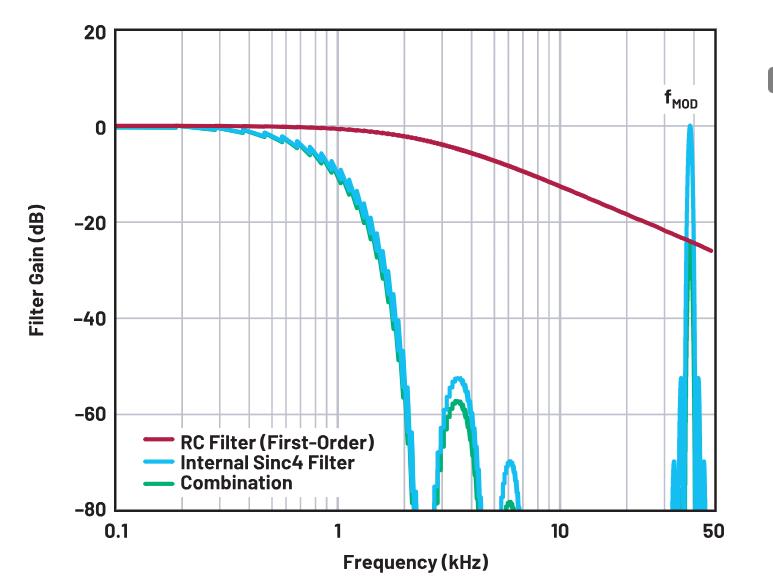

此器件的AFE包括一個片內PGA,其使模擬輸入電流最小化,從而無需外部放大器來驅動輸入。過采樣之后的數字濾波器確保帶寬主要由數字濾波器控制。AD4130-8提供多個片內sinc3和sinc4濾波器,另外還有用于抑制50 Hz和60 Hz噪聲的濾波器。sinc3和sinc4數字濾波器需要外部抗混疊濾波器作為補充。該抗混疊濾波器的作用是限制輸入信號的帶寬量。這是為了確保噪聲(例如變化率為調制器頻率fMOD的噪聲)不會混疊到通帶和轉換結果中。

圖4. AD4130 ∑-Δ簡化系統模塊

圖5. 外部和內部組合濾波的仿真

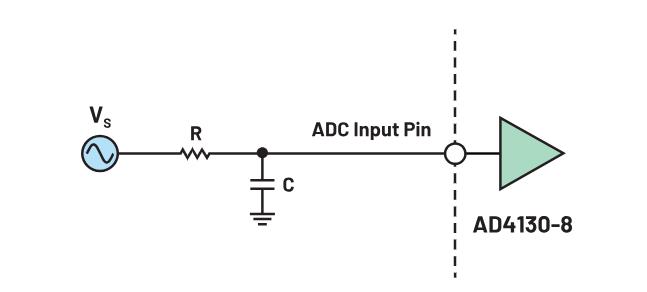

抗混疊濾波器

可以使用更高階的抗混疊濾波器,但通常使用一階、單極點、低通濾波器來滿足要求。濾波器基于對目標信號的采樣進行設計,式1決定濾波器的3 dB帶寬:

根據此電容上可以看到的最大電壓階躍確定電路充電所需的時間非常重要。

圖6. 一階低通抗混疊濾波器

電容上的電壓將隨時間變化,變化率為

VC = 某個時間點電容兩端的電壓,t = 時間

圖7. 響應1 V滿量程階躍變化的一階低通濾波器建立時間

圖7顯示,經過4個時間常數(