- 如何降低交擾

- 降低鎖相環(huán)(PLL)引起的干擾

- 適當(dāng)?shù)貞?yīng)用電容器是降低噪聲的有效方法

- 降低交擾的技術(shù)有:線跡間距加大,增加地線,降低諧波分量和線跡端接技術(shù)

- 采用合適的濾波器和穩(wěn)壓器,分離模擬和數(shù)字地是降低PLL干擾的方法

- 選擇合適電容值并注意一些應(yīng)用電容器的方法

降低交擾

交擾是一個重要的噪聲源。在高速系統(tǒng)中,信號地通路依賴于工作頻率。對于低速信號(<10MHZ),電流經(jīng)過最小電阻地通路(最短通路)返回到源。

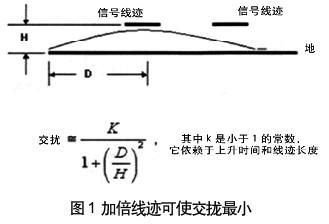

在10MHZ以上,情況就不同。經(jīng)電流最小電感地通路返回。重要的是返回信號以電流分布傳播(圖1),這意味著相鄰信號的返回通路可能容易重疊,導(dǎo)致交擾。

降低交擾的技術(shù)有:線跡間距加大,增加地線,降低諧波分量和線跡端接技術(shù)。

在高速DSP系統(tǒng)中,加倍信號間的線跡間距,可降低環(huán)路重疊,使交擾降低4倍。對于差分信號(Earthnet或USB),建議間距所產(chǎn)生的信號對應(yīng)具有所需的匹配阻抗。另外,關(guān)鍵信號(即時鐘)應(yīng)屏蔽,路由信號在電源和地平板之間的內(nèi)層,或把一個地平板放置在關(guān)鍵信號下面層上。

在再制板上加信號線時,應(yīng)包括一個并聯(lián)地線。這可能提供高速電流返回通路并在電流環(huán)路中產(chǎn)生最小面積。這個附加的通路,確保返回電流不產(chǎn)生大的環(huán)路和拾取噪聲。

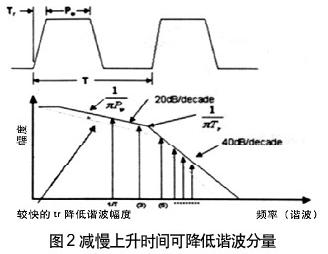

在降低交擾時,評價快速沿所引起的諧波和干擾是重要的。例如,在線跡上增加串聯(lián)終端電阻器,會使上升時間(Tr)減慢,這是有效地降低諧波分量的方法。噪聲幅度曲線在低頻能較好地衰減諧波分量(圖2)。

線跡可做為傳輸線(在上升時間Tr小于2倍傳播延遲時)。因此,應(yīng)保持線跡盡可能的短。若線跡的長度足以做為傳輸線,則用串聯(lián)終端(電阻器與輸出驅(qū)動器串聯(lián))或并聯(lián)終端(在負載處電阻器到地)接線。若電阻器與所用線跡PCB阻抗匹配,則可以降低傳輸線反射和瞬變。

鎖相環(huán)

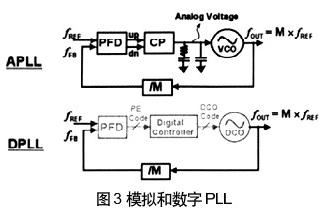

鎖相環(huán)(PLL)是另一個重要的噪聲源。在某些DSP中正日益采用模擬和數(shù)字版本PLL(圖3)。隔離到PLL電源時,用π形濾波器去除高頻噪聲是有效的。但它對去除低噪聲作用不大,需要用多級濾波器網(wǎng)絡(luò)。然而,在快速開關(guān)電路中,一個低壓降(LDO)穩(wěn)壓器是更適合的,因為這種器件在低頻具有高電源抑制比(PSRR)。若設(shè)計的系統(tǒng)運行在噪聲環(huán)境(如汽車、電/機裝置),具有較大的低頻瞬變,則應(yīng)選擇高PSRR穩(wěn)壓器。

分離模擬和數(shù)字地對于隔離來自模擬部分的數(shù)字噪聲有幫助。對于低速電路這樣做也是良好的。然而,對于高速電路(例如視頻部分)應(yīng)避免分離地。快速開關(guān)電流需用最小的電流環(huán)路,而隔離地阻止來自選擇通路的電流。因此,將選擇另外通路到源,這最終導(dǎo)致勢差、電流流和輻射。在數(shù)字數(shù)據(jù)進入點把模擬和數(shù)字地短接在一起,可提供一個直接通路而不影響低頻信號。信號朝實際的最短返回路徑到源,而不是短路的通路。

電容器應(yīng)用

適當(dāng)?shù)貞?yīng)用電容器是降低噪聲的有效方法。去耦電容器提供一個低阻抗到地通路來旁路不希望的高頻能量。可以用體電容器來旁路低頻到地,以及用去耦電容器提供本地電荷存儲。

對于去耦電容器沒有最好的值,這是因為反作用影響。通常,電容器阻抗隨頻率和電容降低。當(dāng)信號頻率超過諧振頻率時,電容器變成電感而不再是一個有效的濾波器。盡管低阻抗和更多電荷存儲能降低下降,但對于高頻信號,高值電容器不是最佳的。理想地,在電源地應(yīng)包含一個高值和一個較低值電容器。若不能實現(xiàn),用一個0.01礔電容器是一個可接受的折衷方案。應(yīng)該用較對大的體電容器,至少10倍于總?cè)ヱ铍娙萜鳌?br />

例如,在100KHZ,100礔電解電容具有0.6Ω左右的等效串聯(lián)電阻(ESR),同樣值的鉭電容具有0.12Ω左右的ESR,這使得鉭電容更適合體電容器。對于去耦陶瓷電容優(yōu)于聚酯電容器。例如,在1MHZ,0.1礔陶瓷電容器具有0.12Ω左右的ESR,而1.0礔聚酯電容器具有0.11Ω的ESR。

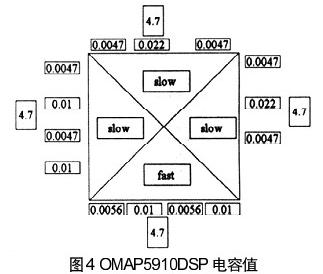

去耦電容器應(yīng)放置在PCB底端靠近器件引腳處。對于高速DSP,去耦電容器應(yīng)放置在每個電源引腳處。若空間不允許這樣做,也應(yīng)盡可能地放置在器件周圍。復(fù)雜DSP去耦的一種有效方法是從對角劃兩個虛線構(gòu)成一個X(圖4)。然后獨立分析4個區(qū)域的每個區(qū)域。

為使得體電容器靠近去耦電容器,把它們放置在板的頂端。這種定位使線蹤最短,同時可降低輻射和寄生電感。

以TI公司的OMAP5910 DSP為例,特別注意包含數(shù)字PLL和外部存儲器接口的區(qū)域(圖4中左邊區(qū)域)。該器件有13個芯核電壓引腳,峰值芯核電流耗電170mA(平均每個引腳13mA)。在該區(qū)域的3個芯核電壓引腳包括數(shù)字PLL和外部存儲器接口,耗電39mA。為了保證精度,在確定電容器大小時,增加100%容限(即78mA)是合適的。必須消除峰值I/O電流。應(yīng)采用謹慎的方法,假定在此區(qū)域所有54個I/O線同時開關(guān)4 mA,這將導(dǎo)致216 mA通過此區(qū)域的8個I/O電壓引腳。

隨著芯核和I/O電壓工作不同頻率,必須用合適大小的電容器去耦電源。在此實例中,用下面的公式計算,計算的芯核電容為0.0078礔,對于216mA I/O 電流所需電容為0.22礔:C=I(dv/dt)

其中I為峰值電流,dv為最大所允許的紋波電壓(假定10mV),dt為上升時間(假定1ns,OMAP5910典型值)。

所以,芯核電容C=78mA×(1ns/10mv)=0.0078礔

在OMAP5910 BGA 封裝中,對于每個區(qū)域的4個電容器都有足夠的空間,沒有一個是用于每個芯核電源引腳的。因此,為了去耦芯核電壓引腳,最好選擇兩個電容器,其總值為 0.0078礔(配置兩個0.0047礔陶瓷電容器,以使從引腳到地有最短距離)。

必須考慮開關(guān)頻率。芯核部分在150MHz開關(guān)轉(zhuǎn)換,而8個I/O引腳在75MHz開關(guān)轉(zhuǎn)換。可以用另外兩個電容器位置來去耦I(lǐng)/O電壓引腳(即用兩個自諧波振頻率75MHz以上的0.01礔陶瓷電容器提供0.022礔)。

體電容器值

在此實例中,DSP總芯核電壓電流為338mA。用上面的公式計算電容為0.0338礔。做為體電容應(yīng)該是10倍去耦電容值,大約為0.39礔。對于I/O電壓,進行同樣的處理,得到0.84礔電容,給出總電容1.23礔。對于體電容器,每個提供3.075礔(1.23礔除以4,然后乘以10),應(yīng)該把它加到每個區(qū)域上。現(xiàn)在可得到的最小體電容值是做為表面貼裝元件的4.7礔,此電容值在本例中工作良好。如果沒有表面貼裝電解電容,應(yīng)選擇鉭體電容器。對于4個區(qū)域的每個區(qū)域去耦和體電容值可以用這種方法計算,并示于圖4。