- 基于EPLD的數字濾波器的工作原理

- 分頻電路設計

- 延時電路設計

- 效果分析

在同步串行數據傳輸過程中,時鐘線上只要有一點小毛刺就會導致數據傳輸失誤,從而影響系統的正常工作。傳統的處理方法是在接收端并入一小電容來濾除毛刺,這種方法只能去除某一固定頻率下的干擾,而在實際工作中,干擾有可能由多種干擾源混合產生,其頻率可能是變化的。另外,若同步串行傳輸有多個接收端,則需要在每個接收線上都并上一電容,這樣,多個電容并聯在同一信號線上,勢必導致所需的信號失真。隨著現代電子技術的發展,EPLD以其編程靈活方便而日益成為現代電子設計的重要手段之一。

本文介紹了一種基于EPLD的數字濾波器,它可以抑制某些低頻線路上的干擾,利用此濾波器可以阻止某些頻帶的干擾信號通過,從而起到硬件抗干擾的作用。由于采用了EPLD技術,硬件編程方便、靈活,針對不同的干擾源的特性,可采取相應的措施來解決。

解決方案

串行傳輸線在實際傳輸過程中容易竄入干擾,其形式一般為小毛刺或窄脈沖形式,可利用它與主信號的不同特性加以濾除。

1 基本工作原理

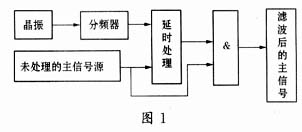

消除干擾信號需兩路輸入信號:主信號和參考時鐘信號。參考時鐘信號經過分頻、調整脈寬等處理,以此使主信號源產生所需的延時,再與其本身信號相比,從而濾去主信號源上的一些窄波干擾信號。濾波器的原理圖如圖1所示。器件可采用LATTICE公司的ispLSI1032E,參考時鐘信號可采用8M晶振。

2 具體電路設計

編程軟件為LATTICE公司的ispEXPERTSystem,它是一套完整的數字系統設計軟件,設計輸入可采用原理圖輸入、硬件描述語言輸入、混合輸入等方式,并可對所設計的數字電路系統進行功能仿真和時序仿真。

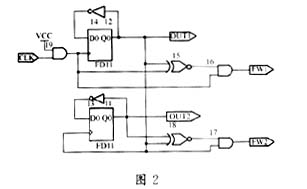

2.1 分頻電路

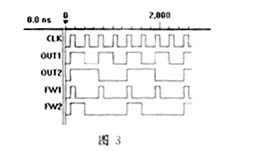

分頻電路可根據各具體干擾源的脈沖寬度來確定。具體電路如圖2所示,CLK為8M晶振信號,經整形后作為DQ觸發器的觸發信號,OUT1輸出二分頻后的4M方波信號,同時作為下一級觸發器的時鐘信號OUT2輸出四分頻后的2M方波信號,FW1輸出頻率為4M、脈寬為125ns的脈沖信號,FW2輸出頻率為2M、脈寬為250ns的脈沖信號,具體波形如圖3所示。由此類推,繼續級連DQ觸發器即可輸出八分頻、十六分頻信號,脈寬也可視具體情況而作相應的改變,電路類似FW1、FW2的產生電路。

由圖2,在ispEXPERT中經仿真得出如圖3所示的波形。

[page]

[page]2.2 延時電路

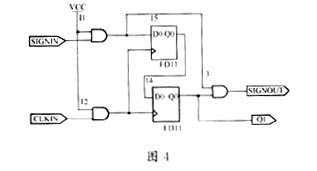

根據干擾源的情況,以前面所述信號作為觸發時鐘,未經處理的信號源經觸發產生延時,再與其本身相比,這樣,一些干擾信號由于脈寬過窄而被濾去。具體電路如圖4所示。

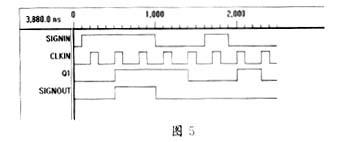

SIGNIN為需處理的信號,被第一個觸發器觸發后,產生延時,同時送入二級觸發器產生二級延時。CLKIN信號的頻率可視干擾源的寬度而定,但需注意的是,干擾源的寬度要遠遠小于信號源的寬度,否則信號寬度將被大幅削減,導致特性被破壞。電路仿真波形如圖5所示。

在SIGNIN信號線上,第二個脈沖由于其寬度小于CLKIN信號周期而被濾去。這在同步串行傳輸的時鐘線上顯得尤為重要。

3 效果分析

此電路簡單可靠,筆者在一串行同步通訊過程中運用此電路解決干擾問題,取得了良好的效果。

由于基于EPLD技術,不需額外增加硬件,且編程靈活,可在ispEXPERT中直接仿真,節省了大量的實驗時間。但在實際操作中需注意兩點:一是在運用此濾波器時,主信號脈沖會有一定的延時,作為同步時鐘,此延時對串行通訊不會有太大的影響,但若在數據線或其它信號線上運用時,需考慮延時時間對系統的影響;二是在運用ispEXPERTSystem進行編程時,它提供的宏器件功能與TTL器件相似,但個別引腳有差別。另外,針對各種傳輸線上的干擾,可根據上述原理加以推廣應用。