【導讀】如何能夠實現在很多電源連接時還能減少引腳接地數量?在降低熱電阻的同時,還能改進PCB設計?本文就來解析使用裸露焊盤和打地線的方式來改進PCB設計性能,同時還能有效的減少引腳數量。

具有裸露芯片焊盤的引腳架構芯片級封裝(LFCSP)和四方扁平封裝(QFP)提供了一種將熱量從元件傳遞到印刷電路板(PCB)、從而降低熱阻的有效解決方案。芯片焊盤的底部是裸露而不是封裝的,應作為集成式散熱器焊接到PCB上。推薦的PCB設計包含一個用于裸露焊盤的焊盤。 該焊盤應包括連接到PCB上的多個接地層的通孔陣列,從而為熱能提供低熱阻路徑。

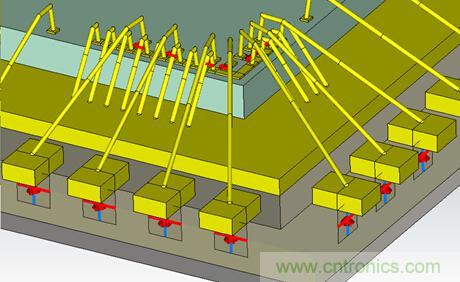

裸露焊盤允許在封裝內使用打地線,從而提供更多的靈活性和優勢。 這些焊線從芯片上的接地墊直接連到芯片焊盤,而不是某一個封裝引腳。外部連接接地層的裸露焊盤還構成一個低阻抗的電氣路徑。 有經驗的設計人員都知道,高性能IC通常在相鄰引腳上有電源連接和接地連接,以形成緊密耦合的低電感環路,用于傳導接地回路電流。 電源和接地電流的相反極性產生的互感可以降低阻抗。

在混合信號設計中,電源和接地連接上的瞬態電流是由數字電路開關、I/O活動、模擬信號擺幅產生的。 這些瞬態會在電源上產生噪聲,或耦合至器件內的敏感節點,從而降低模擬電路的性能。 打地線常用于構建緊密耦合的電流環路,無需額外的封裝引腳。 空閑出來的引腳可以用于其他信號、功能和電源連接。

這些內部打地線通常缺少資料,導致用戶對ADC或DAC如何實現高性能且無需相同數量的電源和接地連接感到迷惑。 某些情況下,器件可能沒有任何接地引腳,因而完全依賴外部焊盤提供所有接地連接。

帶打地線的LLP封裝