【導讀】本文將簡要討論在過程控制中模擬量輸入模塊中的隔離問題以及其傳統(tǒng)解決方法,然后將提出一種替代性的高密度、易于設計的通道間隔離模擬輸入模塊的完整解決方案。測試結果表明,這個16通道、2.5 kV rms通道間隔離演示模塊可以輕松通過EN55022 Class B 和Class A的IEC輻射標準。

在高端工廠自動化應用中(如油氣廠和電廠),常會要求多路采集通道與通道之間進行隔離,其中高耐壓、小尺寸、低EMI、高可靠性和低成本等要求在通道間隔離設計中別具挑戰(zhàn)性。通常目前現(xiàn)有成熟方案,標準模塊實現(xiàn)的通道密度往往僅限于四個通道或八個通道,通道間隔離只能承受數(shù)百伏特耐壓。

過程控制模擬量輸入模塊中的隔離

電氣隔離原理是以物理和電氣方式分開兩個電路,使二者之間無直接傳導路徑,但仍然可以交換數(shù)據(jù)和電源。這通常是通過變壓器、光耦合器或電容來實現(xiàn)的。隔離用于保護電路和人,隔斷接地環(huán)路,提高共模電壓和噪聲抑制性能。

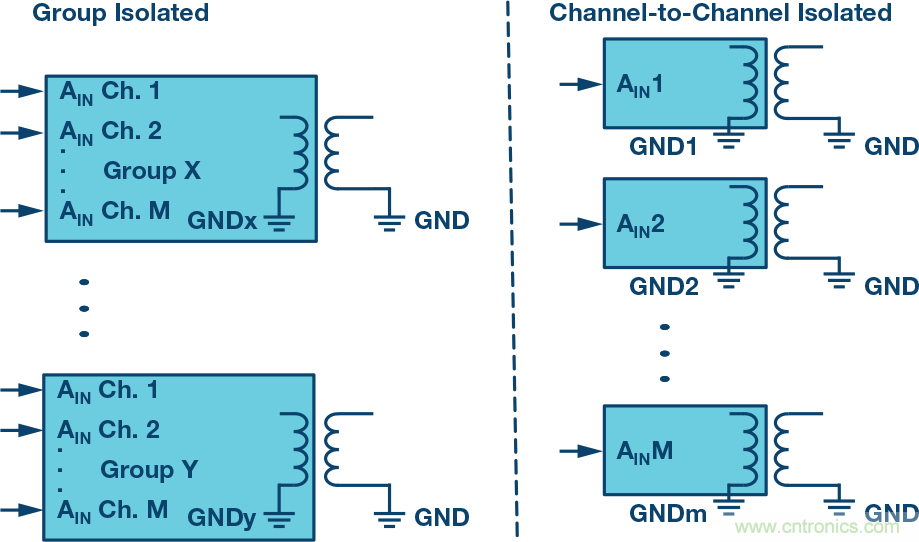

一般地,過程控制的輸入要么采用組塊隔離,要么采用通道間隔離(見圖1)。對于組塊隔離,多路輸入通道組合在一起以共用一組隔離器,包括電源隔離和信號隔離。與通道間隔離相比,這樣可以節(jié)省成本,但限制了組中通道間的共模耐壓,這 意味著這些通道和設備將被建議安裝在相同區(qū)域中。通道間隔離 (如圖1右側所示)相比前者在適用穩(wěn)定性等方面會大大改善。 話雖如此,每通道卻需要更高的成本,因此工廠設計人員必須仔細評估和權衡。

圖1. 組隔離和通道間隔離

在通道間隔離設計中,每個通道都需要專用的電源隔離和信號隔離。隔離是限制輸入模塊通道密度、EMI、成本和可靠性的主要因素之一。在之前的新設計中,每個通道用數(shù)字隔離器來實現(xiàn)數(shù)據(jù)隔離,典型的數(shù)字隔離器(如ADuM141E)有四個隔離數(shù)據(jù)通道,采用16引腳SOIC (6.2 mm × 10 mm)封裝。但是,每個通道仍然需要電 源隔離。接下來,我們就來討論一下三種傳統(tǒng)的電源隔離方法:多抽頭變壓器、推挽式設計和隔離式DC-DC模塊的優(yōu)缺點。

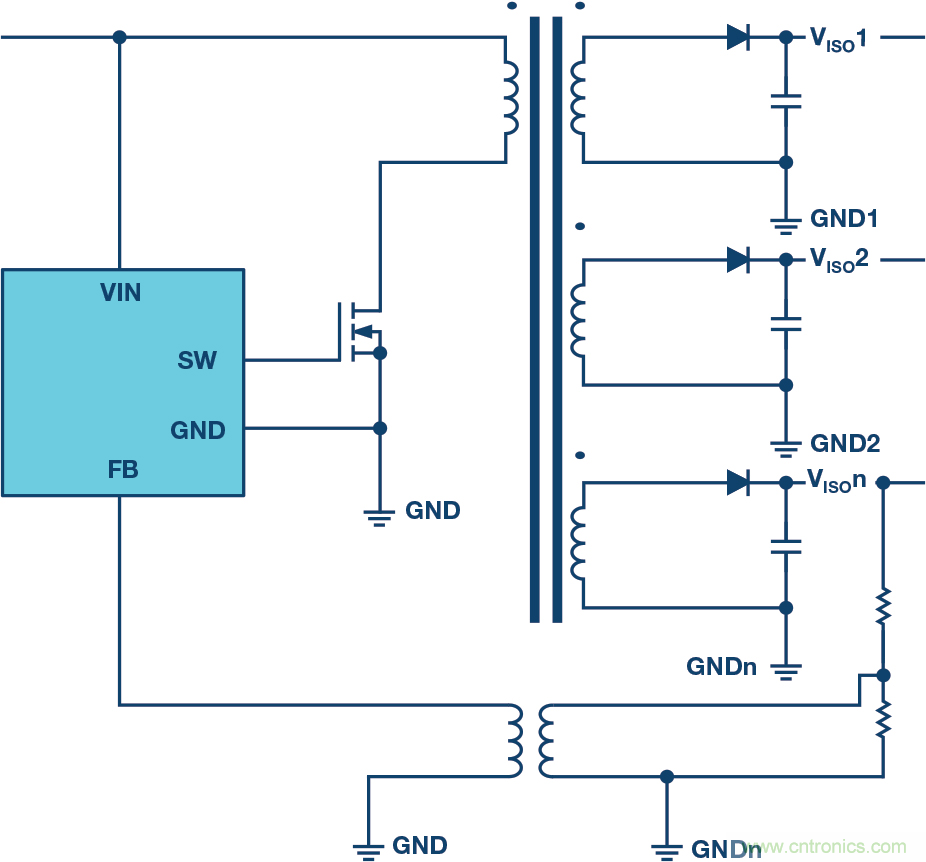

圖2所示為帶有一個多抽頭變壓器的反激式隔離DC-DC架構:一個反激式轉換器驅動變壓器,在抽頭上產(chǎn)生多個輸出。這是一種成熟的電源架構,但在過程控制應用中有六大劣勢:

1.變壓器需要具有多個抽頭和降低EMI的屏蔽層。在小尺寸封裝中很難實現(xiàn)這一目標并保證足夠的可靠性。

2.反饋控制環(huán)路只能使用一路通道,意味著只能對其他通道進行更為松散的調控。為了確保工作的可靠性,就需要對此進行仔細的評估。

3.通道密度很大程度上受到具體變壓器放置方案的限制。對于來自各個抽頭輸出端的電源,變壓器置于模擬輸入模塊的中央,每個輸入通道圍繞變壓器呈扇出形排列,將模擬輸入模塊卡通道限制為四個或八個。

4.來自其中一路通道的干擾噪聲可能通過變壓器抽頭之間的耦合擴散到其他通道中。

5.隔離所能夠承受耐壓等級。多抽頭變壓器只能實現(xiàn)幾百伏特的通道間隔離,除非其采用特殊絕緣材料或設計,然而那樣做會大幅增加變壓器成本。

6.定制變壓器取得UL/CSA認證的成本很高。

圖2. 多抽頭變壓器電源隔離設計

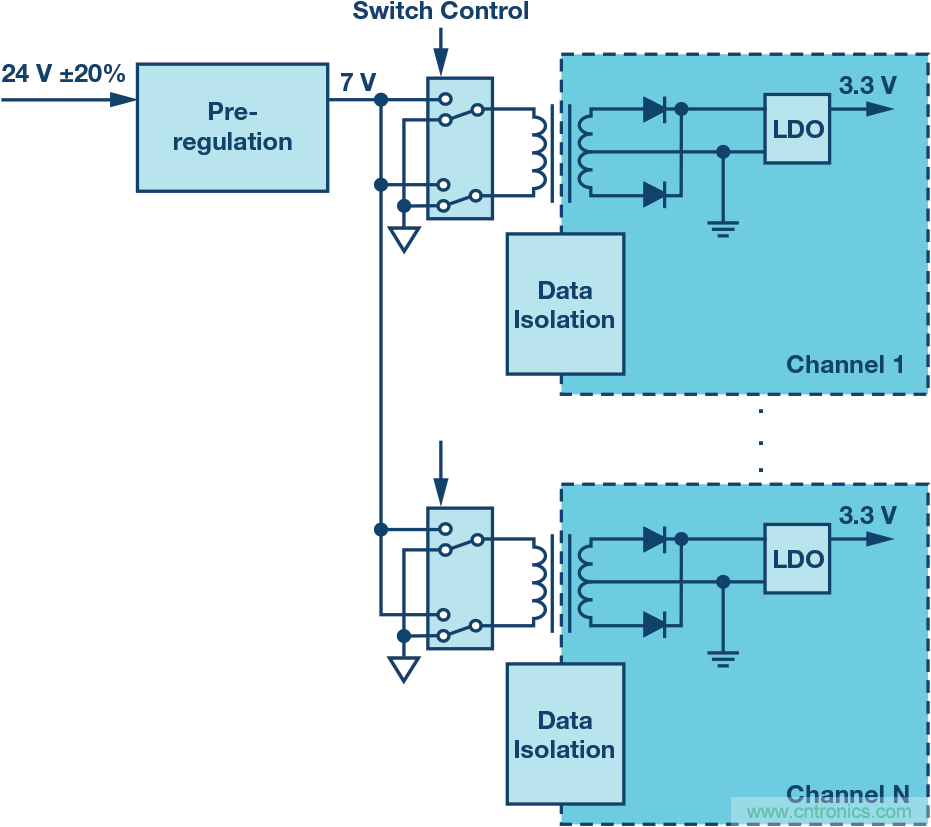

第二種方法是每個通道使用獨立的變壓器,并用推挽法來隔離各個通道。這種方法不使用反饋,而用適當調節(jié)的電源(如7 V)來驅動各個變壓器,然后用LDO在副邊做進一步調節(jié)。這種方法是可行的,因為副邊上的電流消耗相對較低,使得充分調節(jié)成為可能。

這種方法的不足之一是需要進行預調節(jié),每個通道還要使用額外的元件。所選變壓器必須符合要求的隔離額定值。預調節(jié)、變壓器、開關和每個通道需要的LDO會占用電路板空間,增加成本。同時還需要進行大量評估,確保各個條件下都已達到充分調節(jié)。

圖3. 推挽式隔離設計

使用經(jīng)UL/CSA認證的表貼式隔離DC-DC模塊可以大幅簡化隔離式電源設計的復雜性,并使隔離耐壓電壓等級有一定程度提升。即便如此,其成本仍然較高,而且體積并不能有效減少,并且一般只能通過EN55022 A類標準。這些模塊也可能存在傳導性電磁干擾問題,因為多數(shù)模塊的PWM頻率為降低電磁輻射干擾都低于1 MHz。同 時,多數(shù)過程控制模擬量輸入模塊的模擬側電流消耗不到10 mA, 遠遠低于市場上的多數(shù)隔離式電源模塊標稱值。

上面討論的三種傳統(tǒng)方法都難以同時達到隔離性能和成本要求。 這些方法還要求每個通道采用獨立的數(shù)據(jù)隔離器,進一步增加了空間要求和成本。如果電源隔離可以作為數(shù)據(jù)隔離器的一部分, 則結果會怎樣?事實上這一點可以做到,并且也已經(jīng)成為現(xiàn)實。

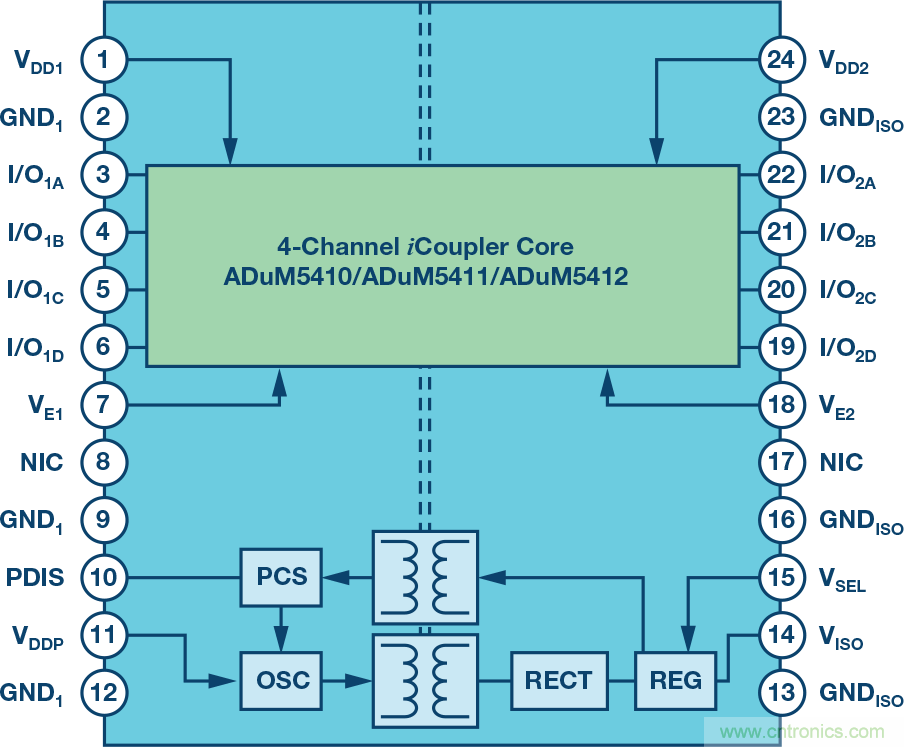

ADI i Coupler®技術和iso Power®技術廣泛用于工業(yè)和汽車市場,這兩種技術可以集成到單個封裝中。以ADuM5411 為例(其功能框圖如圖4 所示),該器件采用7.8 mm × 8.2 mm 24引腳TSSOP封裝,包括完整的電源隔離和四個數(shù)據(jù)隔離通道。其輸出功率高達150 mW,足以滿 足模擬輸入信號調理和數(shù)字化的要求,并能通過2500 V rms UL1577 隔離標準。另外,CMTI(共模瞬變抗擾度)大于75 kV/μs,使其成為存在高瞬變電壓和電流的惡劣工業(yè)環(huán)境(如電廠)的理想選擇。

圖4. ADuM5411功能框圖

基于數(shù)據(jù)和電源隔離的高度集成,模擬量輸入模塊設計得以大幅 簡化,同時還能實現(xiàn)更高的通道密度;可以在傳統(tǒng)隔離八通道空間里實現(xiàn)16個或以上的隔離通道數(shù)量。

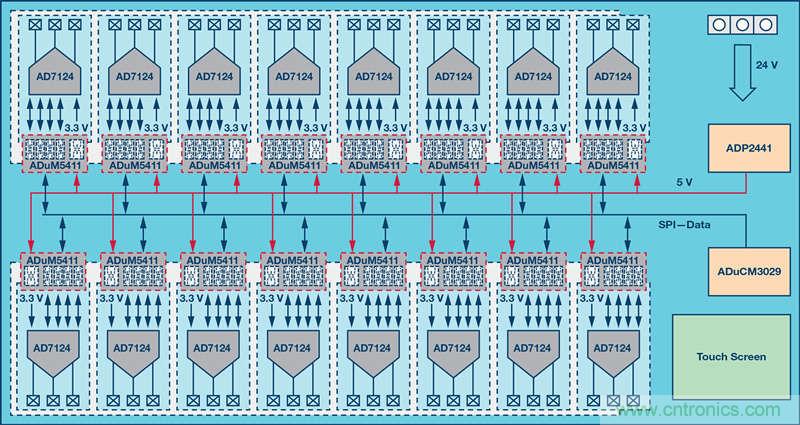

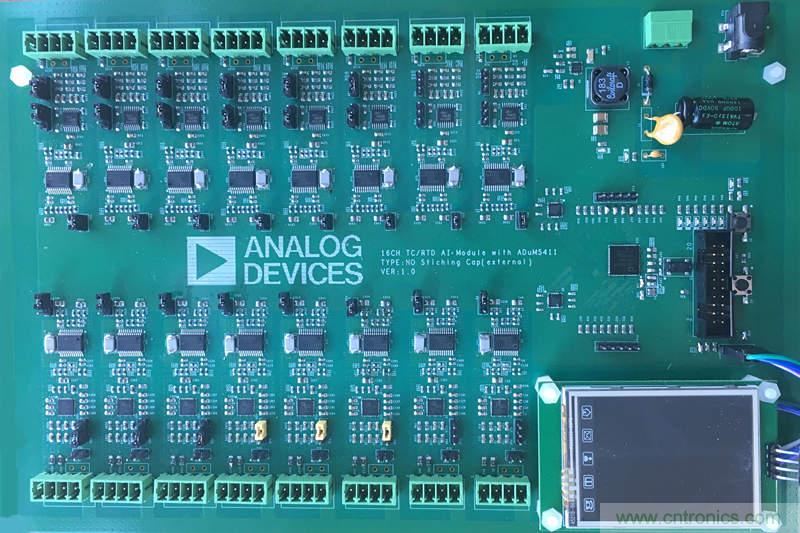

我們用這種方案設計了一個16通道的通道間隔離的溫度輸入模塊 (見圖5),并進行了EMI相關的測試。模塊中的ADuM5411器件為16路溫度輸入通道分別提供隔離電源和數(shù)據(jù)。熱電偶和/或RTD測量是用高度集成的溫度前端IC(AD7124 或 AD7792)實施的,比分立式設計更加節(jié)省空間。ADP2441 將24 V背板電源轉換成3.3 V的低 電壓源用于驅動MCU、觸摸屏和ADuM5411。每個輸入通道只需要 63.5 mm × 17.9 mm的面積。

圖5. 16通道的通道間隔離溫度輸入模塊功能框圖

ADuM5411的布局設計

ADuM5411所用開關頻率為125 MHz。由于通道數(shù)量較多,所以我 們特別注意,以確保電路板能順利通過EN55022 ClassB的電磁輻 射標準測試。

為了盡可能減少輻射,我們采取的原則就是盡量降低功耗、縮短 電流環(huán)路返回路徑,減少共模影響。我們使用了超低功耗集成式 溫度前端IC降,這意味著,隔離現(xiàn)場側消耗的功率會非常小,由此達到減少輻射能量的目的。完全活躍狀態(tài)下AD7124的功耗僅 為0.9 mA。而為了縮短電流返回環(huán)路,我們同時采用了鐵氧體磁珠和少量的旁路電容。

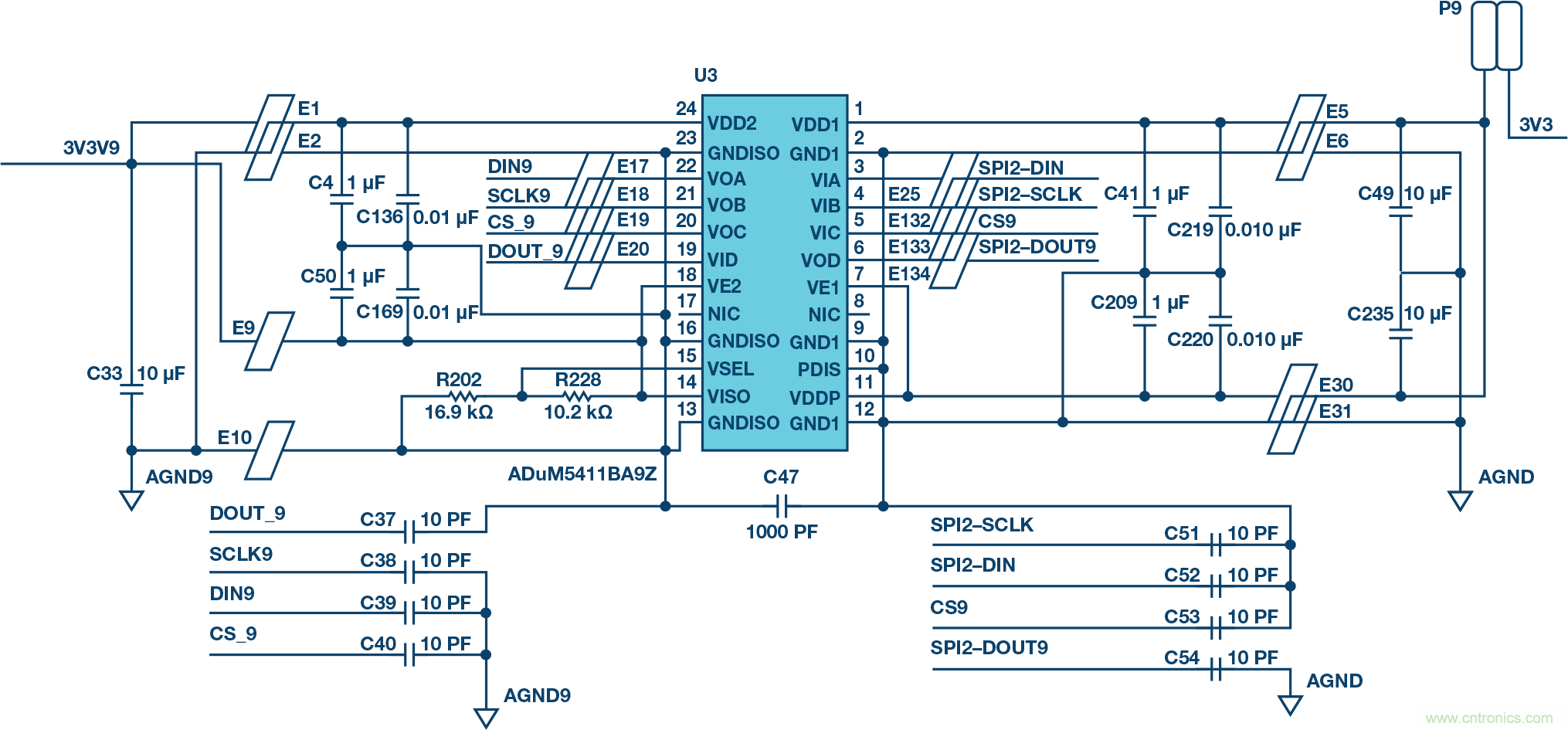

鐵氧體磁珠是在源頭控制輻射信號的一種有效方法,因為它會形成比PCB走線高得多的阻抗。如圖6所示,鐵氧體磁珠與ADuM5411的引腳串聯(lián)(電源引腳起到主要作用)。鐵氧體磁珠的頻率響應是一個很重要的考慮因素,我們使用的鐵氧體磁珠是 BLM15HD182SN1,其頻率范圍在100 MHz至1 GHz之間的阻抗大于 2 kΩ。鐵氧體磁珠應盡量靠近ADuM5411焊盤。VISO路徑上的E9和 GNDISO路徑上的E10上的鐵氧體磁珠是必不可少的。

圖6. ADuM5411原理圖

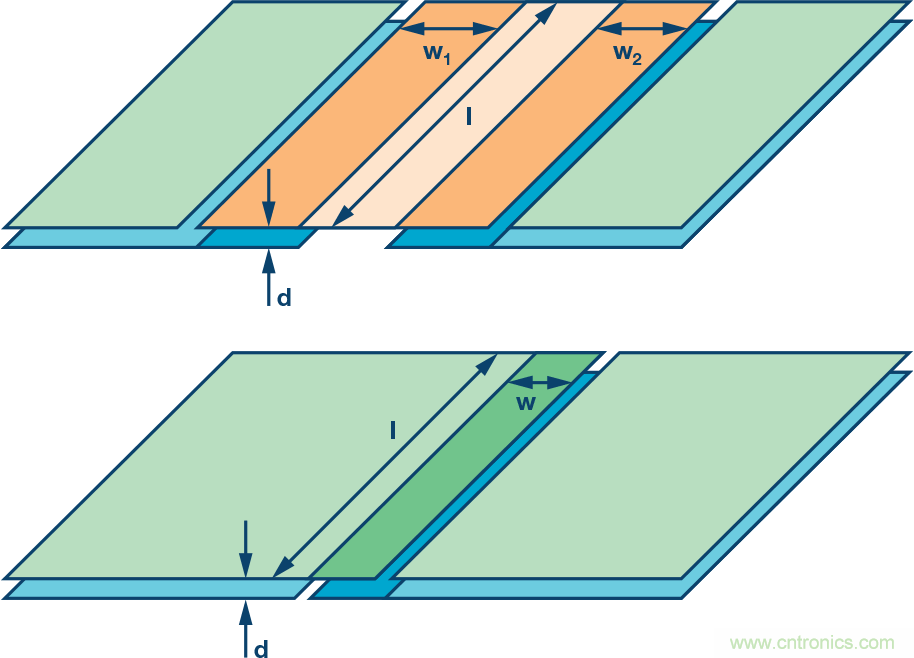

也可以用耦合電容來提供低阻抗的返回路徑,從而減少輻射。 一種方法是在隔離柵上使用表貼式高壓電容,確保符合爬電距離、電氣間隙和耐受電壓標準。Murata、Vishay等供應商均提供此 類電容。受安裝電容帶來的寄生的電感影響,這種方法僅在不 超過200 MHz左右的頻率下有效。為此,一種更有效的技術是在 ADuM5411下方的PCB電路板內構建一個旁路電容。其可以是浮動式旁路電容,也可以是重疊式旁路電容,如圖7所示。

圖7. 浮動式旁路電容與重疊式旁路電容

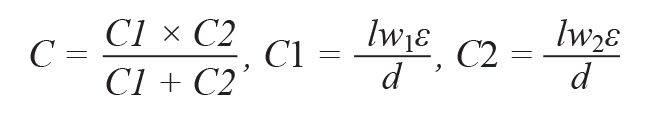

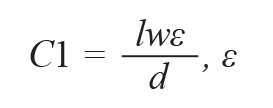

浮動式旁路電容集成了兩個串行電容,即C1和C2。總電容通過公式1計算。

其中:

ε為PCB絕緣材料的介電常數(shù),F(xiàn)R4材料為4.5。

對于重疊式旁路電容,其電容通過公式2計算。

其中:

ε為PCB絕緣材料的介電常數(shù),F(xiàn)R4材料為4 × 10–1 1 F/m。

在材料、面積和距離相同的條件下,浮動式旁路電容的總電容值為重疊式旁路電容的一半,但絕緣材料的厚度則增加了一倍。 依據(jù)IEC60950 2.10.6.4,加強絕緣要求內層絕緣材料的最低厚度為 0.4 mm (15.74 mil),但基本絕緣無此類要求。由于ADuM5411僅提 供2.5 kV rms的基本隔離,所以,我們選擇了重疊式旁路電容以實現(xiàn)電容值的最大化。因相同的原因,內層的厚度也控制在5 mil。

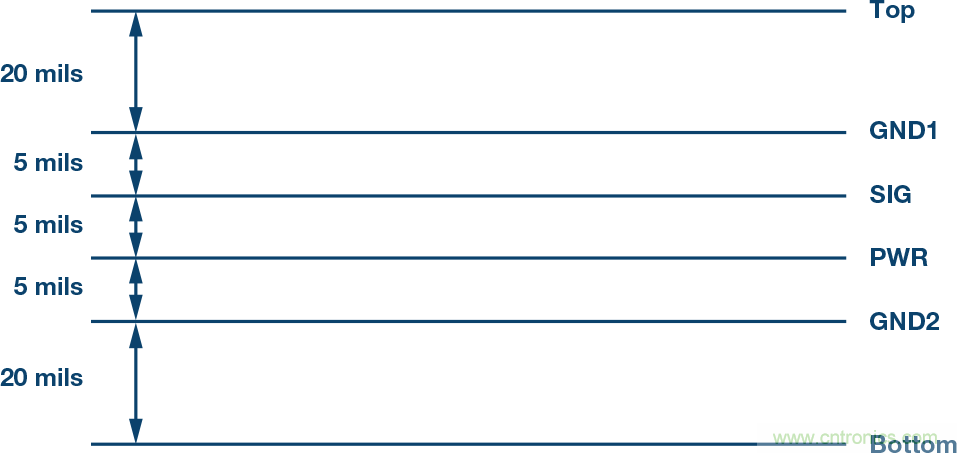

16通道的通道間溫度輸入模塊PCB采用的是一塊6層的電路板。為了兼顧機械和EMI性能,頂層和底層的厚度控制為20 mil,內層控制為5 mil,如圖8所示。

圖8. 六層PCB堆棧分配

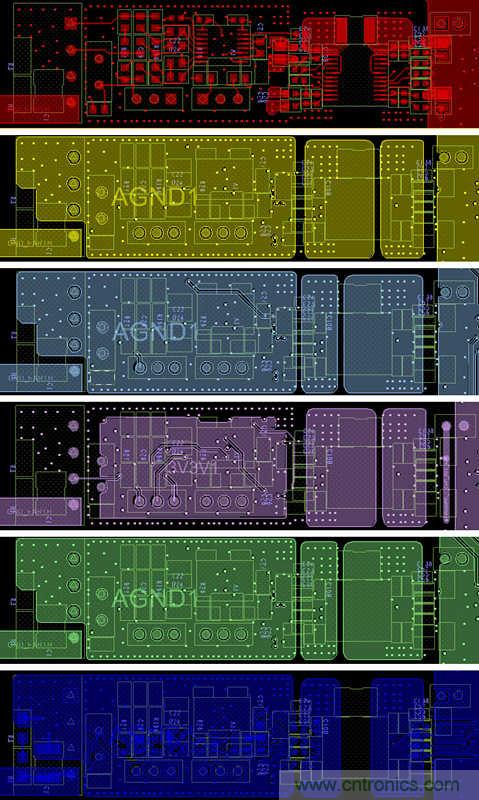

如圖9所示,重疊式旁路電容的各層集成在GND1、SIG、PWR和GND2 中。GND1和PWR上的各層連接至ADuM5411的副邊,SIG和GND2中 的各層連接至ADuM5411的原邊。這意味著,GND1與SIG、SIG與 PWR、PWR與GND2之間共形成了三個并行的旁路電容。重疊區(qū)寬 4.5 mm,長17 mm,即總旁路電容為72 pF。

圖9. ADuM5411區(qū)域的六層PCB布局

基于EN55022規(guī)格的測試結果

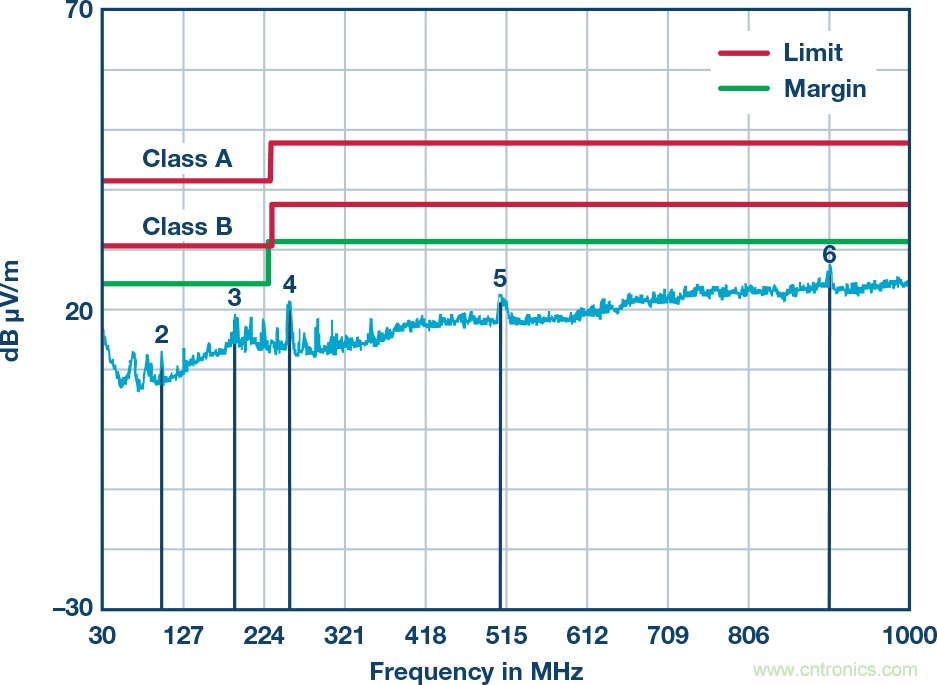

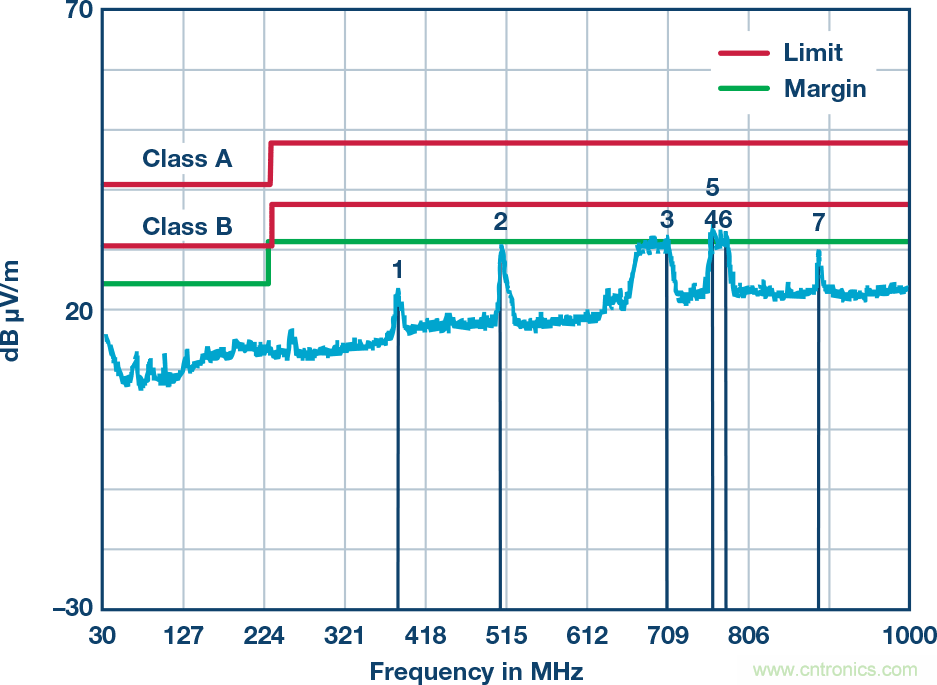

根據(jù)EN55022規(guī)范在10m條件下執(zhí)行兩組EMI測試。對于第一個測 試,帶stitching電容的電路板使用情況如圖10所示。圖11顯示了測試 結果,該測試通過了EN55022 ClassB的標準,裕量約為11.59 dB。對于第二個測試,使用了不帶stitching電容的電路板,而將3kV、150pF 外部高壓電容KEMET C1812C102KHRACTU安裝在電路板上。圖12顯示 了測試結果——通過了EN55022 Class B的標準,裕量為0.82 dB,距 離Class A的閾值還是有足夠多的余量。

圖10. PCB中內置無安規(guī)電容的旁路電容

圖11. EN55022 B類測試結果(PCB中內置旁路電容)

圖12. EN55022 B類測試結果(無旁路電容,有安規(guī)電容PCB)

測試結果證明,相比高壓電容,IC下的stitching電容是更有效的去耦合方法。

結語

通道間隔離往往被視為高端過程控制系統(tǒng)設計中的一項挑戰(zhàn)。相 比傳統(tǒng)數(shù)字和電源分別隔離的方法,ADI的isoPower技術和iCoupler 技術可以大幅提高通道密度,還大大簡化了設計工作,可以提高通道穩(wěn)定性和可靠性。利用PCB中內置的stitching電容或安裝在PCB旁邊的高壓電容,可以輕松地控制EMI輻射以便通過EN55022 B類或A類標準,這是一項技術上的突破。

推薦閱讀: