中心議題:

- 計算機仿真

- 參數建模法

- 子電路建模法

解決方案:

- 直接通過研究器件資料得到所需參數的數值,生成庫文件

- 單元電路和集成電路新產品,由用戶自己創建子電路的網格表轉化庫文件

計算機仿真具有效率高、精度高、可靠性高和成本低等特點,已被廣泛應用于電力電子電路(或系統)的分析和設計。計算機仿真不僅可以取代系統許多繁瑣的人工分析,減輕勞動強度,提高分析和設計能力,還可以對電路進行優化和改進,最大限度地降低設計成本,縮短系統研發周期。

但這些優點都是基于元器件模型,電路的數學化主要是元器件的模型化,可以說沒有模型化就沒有電路的仿真分析。簡單的元器件,比如,電阻、電容和電感等,只需要一個或幾個參數就可以描述其電學性能。而各類半導體和集成器件,則需用很多參數來描述較復雜的建模過程。

目前各種仿真工具中都自帶很多常用的元器件模型,但是自帶模型庫永遠跟不上電子元器件的更新速度。這里針對建模的重要性和必要性,研究當前流行的電子電路仿真工具的電子元器件模型,提出兩種建模方法:參數建模法和子電路建模法。

參數建模法

參數建模法主要是針對加工工藝相同的一類半導體器件提出的,其工作過程是先利用物理法或黑箱法構建出不同復雜程度的等效電路,然后通過公式演算,得出這類半導體器件的參數。在使用過程中,若遇到該類器件,就可以通過直接設置參數值實現不同型號元器件的建模,從而省去重復構建等效電路和繁瑣的方程式推導過程。

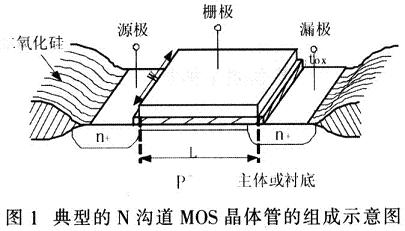

下面以N溝道MOS(metal-oxidesemiconductor)晶體管為例說明等效電路與參數之間的關系。典型的N溝道MOS晶體管組成示意圖如圖1所示。

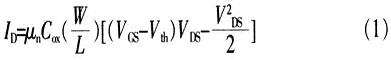

設置柵極寬度為W,有效柵極長度為L,柵極下氧化層的厚度為tOX。MOS管的特性方程為:

式中,COX是每單位面積的柵極電容。Vth為柵極-源極間的閾值電壓。

[page]

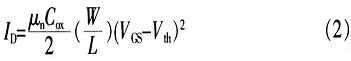

當VDS增加時,ID上升,直到溝道的漏極末端夾斷,ID不再上升。這種夾斷發生在VDS=VGS-Vth時。因此工作區MOS管的特性方程可簡化為:

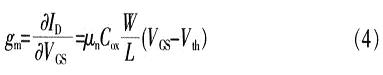

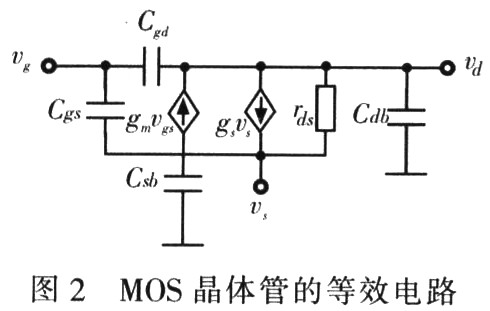

通過式(2)得到如圖2所示的MOS晶體管等效電路,其中壓控電流源gmVgs是模型中最重要的部分,晶體管的跨導gm定義為:

將式(2)代入式(3),可得出:

圖2中,gsVs表示第2個壓控電流源,模擬漏極電流id上的體效應。當源極與地相連時,或其電壓不變化時,此電流源可忽略。當體效應不能忽略時,則有:

式中,γ是體效應參數,|2φF|為表面反轉電勢。圖2中,電阻rds表示有限輸出阻抗,模擬溝道長度調節和漏極電流因Vds改變而引起的效應,由式(1)可得:

圖2中,電容的求解過程參見參考文獻[1],以下給出結果:

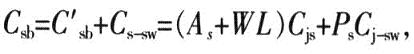

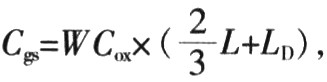

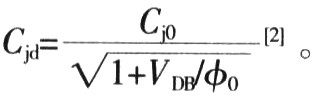

Cgs是最大電容,需要較高精確度時可表示為:

LD是重疊區的距離。

[page]

第2大電容Csb表示為:式中,As是源極的結面積,Ps是源極的結周長,不包括與溝道相鄰的一邊,Cj-sw表示0V偏置下的側壁電容。

(Cj0偏置下的耗盡結電容)。

Cgd稱為密勒電容,其值為:Cgd=WCoxLD。

源極主體電容Cdb表示為:Cdb=C''''''''''''''''db+Cd-sw=AdCjd+PdCj-sw,其中,Ad是漏極的結面積,Pd是不包括與柵極相鄰部分的結周長

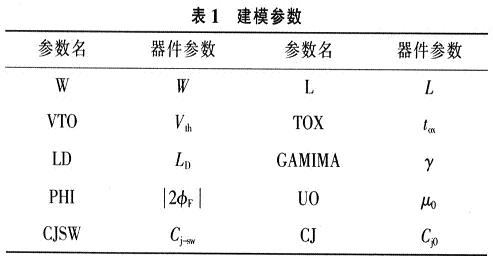

在仿真工具中建模,可指定如表1所示參數,系統自動根據上述計算式確定等效電路參數,從而完成該器件的建模。

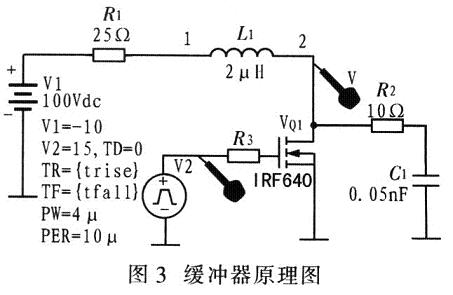

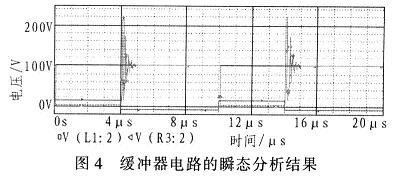

在pspice中仿真得到預期結果,如圖4所示。

可見參數建模法省去了構建等效電路的過程,只需通過廠商提供的器件特性參數就可以直接建模。但該方法只適用于固定結構的半導體器件。

[page]

子電路建模法

隨著電子器件的不斷更新,單純依靠修改參數值進行建模已經遠遠不能滿足現在電子電路仿真的需求。針對常用電路單元和集成電路新產品,本文提出一種為新產品建立一個子電路模型的方法,并將該模型作為一個器件添加到仿真軟件的模型庫,在仿真電路時用戶可以像調用自帶庫一樣直接使用該模型。

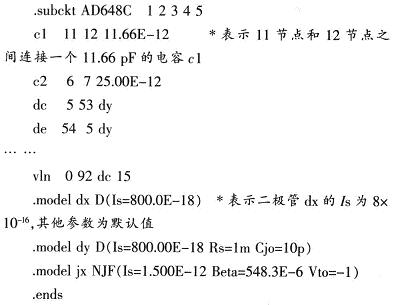

將此種的文本文件存為.lib的后綴名后,通過ModelEditor工具將該文件與器件符號聯系在一起,就可以使用在電路仿真中。圖5為AD648C的簡單運用電路,從圖6瞬態分析結果可知建模正確。

對于前面所述的器件內部全部子電路建模法,很多時候并不能如此具體的了解一個器件內部的所有結構,這種情況下只能通過模擬器件行為建模。直接在子電路中用運算函數代替電路本身。

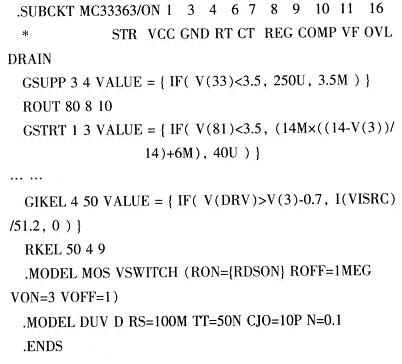

對高壓開關穩壓器MC33363進行以下的子電路連接網格表:

語句GSUPP34VALUE={IF(V(33)<3.5,250U,3.5M)},表示節點33和節點3、4之間連接的模塊實現當輸入端33節點的電壓小于3.5V時,輸出端節點3和節點4之間的電壓為250μF,否則為3.5mV。該網格表使用到的EVALUE和GVALUE器件是將輸出量和輸入量之間運算函數關系用語句表示。EVALUE和GVALUE稱為模擬行為模型(ABM)器件,除了這兩個外還有:*SUM、*MULT、*TABLE、ABS、LOG等,帶有“*”符號的元器件,有E、G兩種類型。使用ABM器件可省去實現這些換算的電路,簡化子電路建模的工作量。

電路原理圖仿真的最大瓶頸在于電子器件的建模,針對這一難點給出兩種方法:一種是對于已經參數化的典型半導體器件,可以直接通過研究器件資料得到所需參數的數值,生成庫文件:另一種是針對一些單元電路和集成電路新產品,由用戶自己創建子電路的網格表,再轉化為庫文件。實驗證明這兩種方法都是行之有效的。