- 可將300mm晶圓打薄至7μm

- 內存模塊、CMOS元件

東京大學研究生院工學系研究專業附屬綜合研究機構與日本迪思科(Disco)、大日本印刷、富士通研究所以及WOW研究中心等共同開發出了可將300mm晶圓(硅底板)打薄至7μm的技術。如果采用該技術層疊100層16GB的內存芯片,芯片之間以硅通孔(TSV)連接,便能以大拇指大小的封裝尺寸實現1.6TB(太拉)的內存模塊。

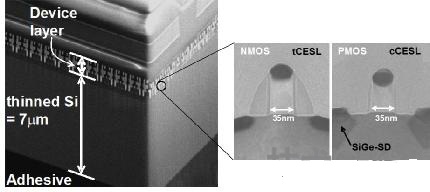

東大等在半導體制造技術相關國際會議“IEDM 2009”上發表了此次的研究開發成果。在IEDM 2009上發表的內容為,在硅晶圓上形成基于CMOS邏輯元件用45nm工藝的CMOS元件時,即使將這種晶圓打薄至7μm,也不會對n型MOSFET和p型MOSFET的應變硅、銅布線以及低介電率(low-k)層間絕緣膜產生不良影響。在不降低晶體管特性的情況下,成功實現了晶圓的薄型化。東大等表示,這是全球首次嘗試將300mm晶圓打薄至7μm并進行特性評測。

此次的成果是通過東大綜合研究機構特任教授大場隆之主導推進的產學項目“WOW Alliance”取得的。約20家企業及團體參與了WOW項目。該項目的目的是,預先對制作CMOS元件的晶圓進行打薄處理,接著層疊打薄后的晶圓,然后利用TSV完成布線,以此提高三維層疊LSI的量產效率。與層疊由晶圓切割而成的半導體芯片,或在晶圓上層疊芯片的三維技術相比,此次在層疊晶圓之后進行切割的技術在成本上具有更高的競爭力。此前最多只能將晶圓打薄至20μm左右,將晶圓打薄至7μm之后,不僅容易形成TSV,而且向TSV內填入金屬也變得更加輕松,因而有助于進一步降低制造成本。

僅厚7μm的300mm晶圓的截面照片。采用45nm的CMOS邏輯元件工藝形成了MOSFET