- 音樂播放控制電路總體方案的設計

- 設計任務分析

- 電路的實現

- 音高編碼和分頻控制

- 音長控制

- 音強控制

- 樂曲的循環播放控制

- 曲譜編碼舉例

1總體方案的設計

設計一個具有3個八度音程的電子音樂自動循環播放電路,具體曲目可以由設計者自由編輯,以簡譜的二進制編碼形式存放在ROM的數據文件中。

設計要求如下:

(1)采用5位二進制碼表示音高信息,曲譜碼存儲器的地址由時值計數器控制,計數頻率按樂曲的演奏速度選擇,每個脈沖周期是所選曲譜中最短音符的時值。存儲器在時值計數脈沖作用下順序輸出音高碼控制分頻器。

(2)采用20Hz~20kHz的音頻脈沖信號控制蜂鳴器,可以使其根據控制信號頻率發出不同的音調。

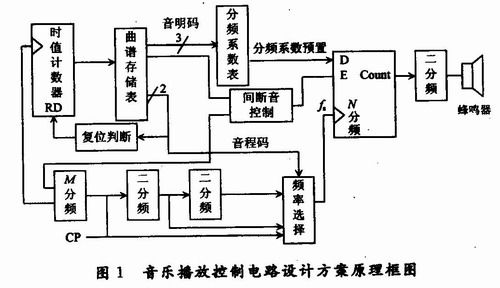

音樂播放控制電路設計方案原理框圖如圖1所示。

2設計任務分析

2.1音高編碼和分頻控制

計數器模值控制的方法很多,改變預置數控制模值是比較簡單的一種。分頻計數器的預置數與分頻率和計數方式、預置方式有關。當采用減計數器、并以計數器的溢出信號(CarryOut)實現異步預置控制時,計數器的模(分頻率)等于預置數。比如,當計數脈沖頻率為10MHz時,若希望產生音高“5”,并考慮占空比整形的二分頻作用,分頻系數(計數器的模)應該是3188.9,四舍五入后的計數器預置數應該是3189。其溢出信號的頻率為3135.8Hz,控制蜂鳴器的信號頻率為1567.9Hz,滿足音高頻率要求。若采用同步預置方式,則計數器的預置數應該是模減1,為3188。由于計數器的溢出信號可能出現冒險干擾,采用同步預置的方法比較安全。

[page]

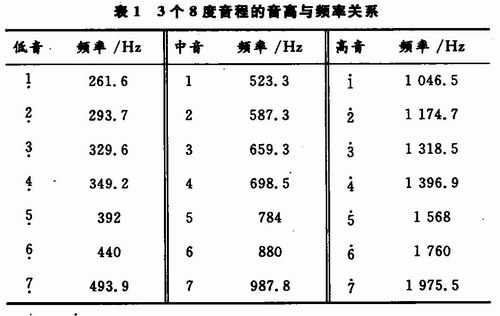

分析表1可見,表中3個不同音程相同音名(同一行)的信號頻率都相差一倍。

即音程升、降8度時,頻率增加或減小一倍。所以,若分頻計數器的計數脈沖頻率降低一倍時,蜂鳴器發出的音調降低8度。比如,當分頻率仍為3189,但計數脈沖頻率為5MHz時,控制蜂鳴器的信號頻率為784Hz,為中音“5”。

因此若采用模值和輸入脈沖頻率都可控的計數器實現信號分頻,可根據音程碼選擇分頻計數器的輸入脈沖頻率fs、根據音名碼控制分頻計數器的模值N,如圖2所示。

這樣,分頻系數表只需考慮7個音高。由于計數脈沖只能分頻降低,所以表中應該存儲高音程7個不同音名對應的計數器預置值,其他兩個音程可通過降低分頻計數器的脈沖頻率實現。

3個8度音程的21個音高至少需要5位二進制碼表示。為了控制方便,考慮將音名和音程分別編碼:7個音名和休止符采用3位二進制碼表示,控制分頻器計數器的預置數實現模值N修改;3個音程用2位二進制碼表示,控制分頻器的計數脈沖頻率fs。

2.2音長控制

曲譜存儲單元的數據輸出時間是時值計數脈沖的一個周期,決定了該單元音符的持續時間。所以,與計數脈沖周期相同時值的音符為音長的度量單位,其音符碼占1個存儲單元。其他音符根據其時值長短占據不同數量的存儲單元。比如,若以8分音符的時值作為存儲器地址計數器的脈沖周期,則8分音符碼占1個存儲單元,4分音符占2個存儲單元,2分音符占4個存儲單元,以此類推。

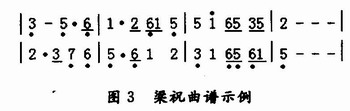

因此,可以所選曲譜的最短音符作為時值的度量單位。比如,圖3所示的《梁祝》曲譜中最短的音符為8分音,若其編碼存放1個存儲單元,則時值計數脈沖周期為一個8分音長時間,可選O.5s。曲譜中的四分音符碼需要存放2個單元,一拍延長音也需要2個單元。該段曲譜有8個音節,每個音節是一個全音(8個8分音),演奏總時值為8×8個8分音。所以,存儲曲譜編碼的存儲器需要64個存儲單元。

[page]

[page]2.3音強控制

音的強度也稱音的力度,體現了樂曲的情感元素。由于本設計實現的是簡單的電子音樂播放,無法表現音強的不同。而且,參考方案還不能區別相同音高的音符連續與否。比如,兩個八分音符“11”的總時值與一個四分音符“1”的時值相同,但體現的樂聲是不同的。前者是兩個強8分音,而后者可以認為是一個強8分音和一個弱8分音構成。為了解決這個問題,可以在連續的相同強音間加一個極短促的間斷區別兩者的不同,間斷時間可以是幾個毫秒。這樣,在音符編碼中應該有一位碼控制。

如果間斷音碼單獨占1個存儲單元,可設置間斷音標志,控制時值計數器狀態為間斷信息單元地址時計數頻率改變,使間斷碼輸出的時間為間斷音長;如果間斷音碼與強音碼存放同一單元,可觸發數字單穩態電路產生問斷控制信號EN。

2.4樂曲的循環播放控制

為了實現樂曲的循環播放,應該在樂曲結束時使曲譜表的查表地址回到初始值。可在曲譜表的最后一個單元中存放一個結束符,結束符的編碼可以利用音程碼的冗余碼。電路采用邏輯門對音程碼進行判斷,當出現結束符碼時控制時值計數器復位,樂曲重新開始演奏。

2.5曲譜編碼舉例

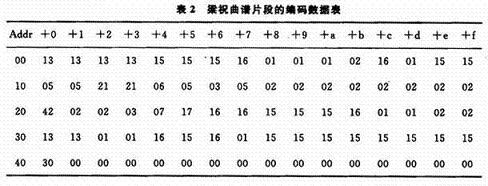

設音符的6位二進制編碼中,最高位為間斷音控制,中間2位為音程碼,最低3位為音名碼。每個8分音存放于1個存儲單元,四分音符碼占2個存儲單元。若音名碼用其簡譜數符對應的二進制碼表示,而低、中、高三個音程分別用"01”,“00",“10”三組碼表示,“11”為結束符碼,則圖3曲譜碼存儲表如表2所示。表中6位二進制音符碼用2位八進制數表示。

3電路的實現

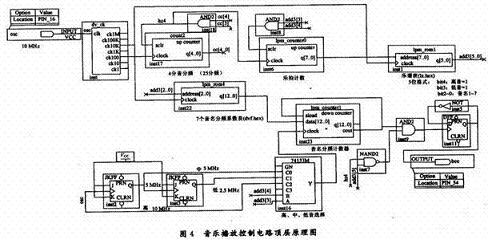

根據設計電路原理框圖,曲譜碼以分頻數編碼,音高信號分頻由一個可預置的模N計數器實現。分頻系數表和曲譜表都存儲在ROM中。若希望控制蜂鳴器的信號占空比為50%,分頻器的輸出信號采用二分頻電路實現占空比整形,但注意信號頻率被降低一半。電路原理框圖中M分頻器的作用是產生合適的時值計數脈沖頻率。電路的頂層原理圖如圖4所示。

FPGA技術已成為電子系統設計領域現代化的標志。本文將FPGA用于電子技術課程設計,取得了較好的效果。通過本設計激發了學生學習的興趣,拓寬了學生的思路,為學生今后的畢業設計和從事電子技術方面的科研、開發工作打下了良好的基礎。