- 探討電平測量時需要考慮的速度問題

- 盡可能短的屏蔽電纜

- 將靜電計、SMU或皮安計與信號源連接起來

時間和頻率的關系

理解穩態直流信號加到電壓表上的情況在概念上沒有什么困難。然而,如果該信號具有時變的分量,例如在直流信號上疊加了交流信號,儀表就將跟隨該變化的信號,并表示出該輸入信號的瞬時幅度。當交流分量的頻率增加時,直流儀表的響應就會變得不夠快,直到在某一頻率時,儀表只能顯示出輸入電壓的平均值。電壓表對交流信號的響應降低到70%時的頻率常常稱為“3dB點”(f3dB)。數字多用表的帶寬粗略地為其顯示讀數的變換速率(每秒鐘的讀數次數)的一半。除了將數字量重新變換為模擬信號的情況,儀表模擬輸出的帶寬一般要寬得多。

帶寬說明了儀器在某一頻率范圍內響應時變信號的能力。儀器響應速度的另一種度量方法是其響應階躍函數信號的能力。這種響應的典型度量是儀器的上升時間。帶寬或上升時間可以用來說明儀器對時變信號的響應情況。

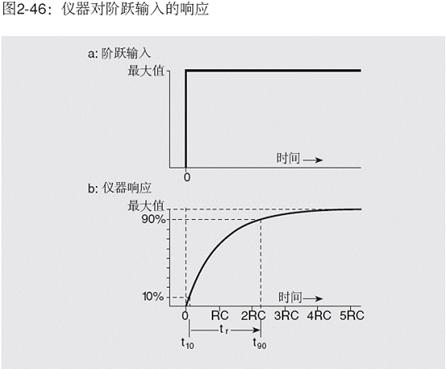

模擬儀器(或模擬輸出)的上升時間一般定義為輸入信號從零立即上升到某一固定值時,輸出信號從最終值的10%上升到90%所需要的時間。此關系示于圖2-46。圖2-46a示出假定上升時間為零的階躍函數,而圖2-46b示出儀器的響應及相應的上升時間。單極點系統(1階系統)的上升時間、頻率響應和RC常數是有關聯的。3dB點由下式給出:

在要求的誤差優于0.1%(有的時候是1%)的情況下,二極點效應開始起作用。例如,由于絕緣體的介電吸收和其它的二階效應,為了達到最終值的0.01%,一般需要4倍以上上升時間的時間長度。

總的來說,由于頻率響應和上升時間直接有關,模擬儀器(或者大多數數字儀器的模擬輸出)對于變化的輸入信號的響應是其帶寬的函數。為了確保準確的測量結果,在加入輸入信號之后,必須允許足夠的建立時間,以便使源、儀器的連接以及儀器本身建立到其穩定的狀態。 function ImgZoom(Id)//重新設置圖片大小 防止撐破表格 { var w = $(Id).width; var m = 650; if(w

[page]

輸入電容對上升時間和噪聲的影響

電壓測量

在對高阻抗源進行電壓測量時(圖2-47),電壓表(VM)兩端的電容(CIN)必須通過RS充電。輸出電壓對時間的函數關系為:

VM = VS (1-e-t/RSCIN)

其中:VM = 在t秒時電壓表的讀數

VS = 階躍函數電壓源

t = 階躍發生后的時間秒數

RS = 以歐姆為單位的等效串聯電阻

CIN = 以法拉為單位的等效并聯電容(儀器的電容加電纜的電容)

使用分流型安培計(圖2-49)時,輸入電容對電流測量的影響與電壓測量時類似。分流型安培計可以看成是在其輸入端跨接了電阻器的電壓表。電路表明,輸入電容(CIN)必須以時間常數RSCIN的指數速率,充電到ISRS伏。注意,CIN是源、連接電纜和儀表電容之和。

[page]

反饋電流測量

輸入電容對采用負反饋的電流表的影響與其對分流型安培計的影響不同。這種模式的電路示于圖2-50。

反饋型皮安計的上升時間是反饋電阻(RFB)上并聯的物理電容或寄生電容的函數。靜電計、SMU和皮安計等都可以使用比較大的源電容數值。應當認識到增大輸入并聯電容(包括源、電纜和輸入電容等的并聯效果)的數值將會使測量的信號-噪聲比降低。

電阻測量(恒流法)

輸入電容也會以同樣的方式影響電阻測量(圖2-51)。這時,CIN也必須由電流(IR)充電,因此也適用同樣的公式。

對于大多數高阻源的測量來說,考慮上升時間的時候,需要盡量減小儀表輸入端并聯的電容。前面提到,這樣做同時也降低了噪聲增益。廣義地說,與儀表的反饋阻抗相比,源阻抗應當比較大。

減小輸入電容最有效的方法是用盡可能短的屏蔽電纜將靜電計、SMU或皮安計與信號源連接起來。在測量高阻源的電壓或者測量高電阻的時候,保護技術可以盡量降低輸入電容的影響。因為這時用適當的電位驅動三同軸電纜的內層屏蔽或包圍輸入端的屏蔽盒,從而盡量降低了有效電容。