【導讀】業界內對可測性是這樣定義的,產品能及時準確地確定其狀態,隔離其內部故障的設計特性,以提高產品可測試性為目的而進行的設計被稱為可測試性設計。本文詳述遙測產品信號處理器的設計原理,并且增加BIT來提高信號處理器的測試覆蓋率。

可測試性是同可靠性、維修性相并列的一門新型學科,其發展和應用對于提高產品的質量,降低產品的全壽命周期費用具有重要意義。隨著集成電路設計方法與工藝技術的不斷進步,集成電路的可測性已經成為提高產品可靠性和成品率的重要因素。

1 信號處理器簡介

硬件電路軟件化是電路設計的發展趨勢。借助大規模集成的FPGA和高效的設計軟件,不僅可通過直接對芯片結構的設計實現多種數字邏輯系統功能,而且由于管腳定義靈活,從而減輕了信號處理器電路圖設計和電路板設計的工作量及難度。這種基于可編程邏輯器件的設計大幅減少了芯片的數量,縮小了系統的體積,提高了系統的可靠性,同時也增加了信號處理器的測試復雜度,降低了故障隔離率。

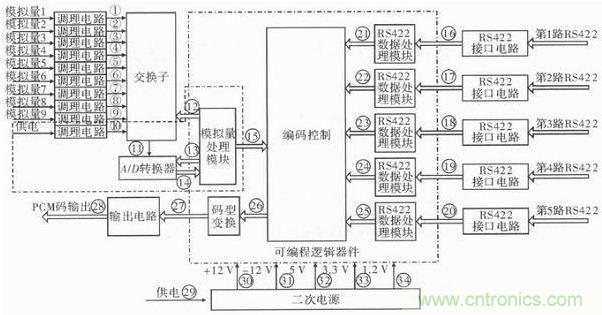

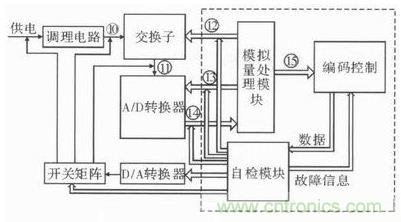

信號處理器主要完成電壓模擬信號的分時采集、RS422總線信號的接收和編碼輸出等功能,原理框圖如圖1所示。

圖1 信號處理器原理框圖

2 信號處理器測試現狀分析信號處理器作為遙測產品的重要部件,其可測試性基本決定了遙測產品的可測試性,因此提高信號處理器的可測試性意義重大。由圖1可知信號處理器需要進行測試的節點較多,主要包括多路模擬信號調理電路、交換子、A/D轉換器、RS422總線接口芯片、PCM碼輸出電路、FPGA內部的各邏輯模塊、二次電源等,共計約34個測試節點。

在地面或試驗室環境中,采用信號模擬器、萬用表、示波器、數據接收設備等對信號處理器進行測試,可以考核全部測試節點,基本實現信號處理器100%的測試覆蓋率和故障隔離率。

在供電、二次電源變換以及PCM輸出正常的前提下,在掛機自檢過程中通過接收到的PCM數據僅可獲取部分模塊的工作狀態,主要包括“供電”信號所在的調理電路、交換子、A/D轉換器、模擬量處理模塊和編碼控制模塊的部分功能,測試覆蓋率約為24%。當4個單元中任意一個單元或多個單元出現故障時,無法通過數據分析完成故障的進一步隔離,從而形成一個模糊度為4的模糊組,故障隔離率0%。

[page]

3 BIT設計分析

3.1 單一模擬信號采集通路BIT分析

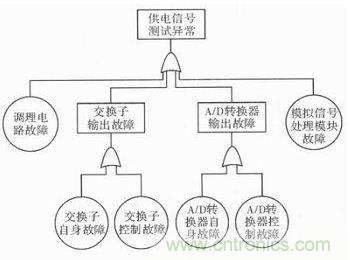

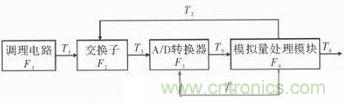

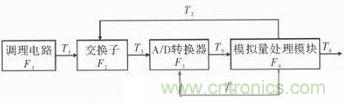

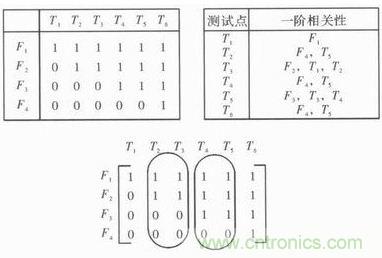

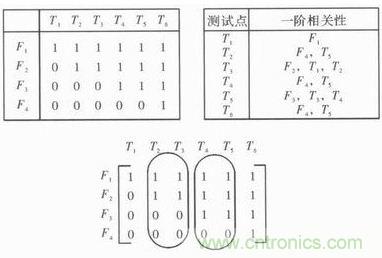

通過對圖1中雙點劃線部分電路進行分析,建立故障樹如圖2所示,根據故障樹形成相關性圖形模型如圖3所示,獲得一階相關性及相關D矩陣如圖4所示。

圖2 故障樹

圖3 相關性圖形模型

圖4 一階相關性及相關D矩陣

圖5 診斷樹和故障字典

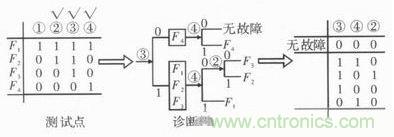

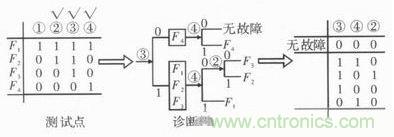

通過對D矩陣分析,識別冗余測試點和模糊組,完成檢測用測試點選擇,生成診斷樹和故障字典如圖5所示。3.2 單一模擬信號采集通路的BIT設計

部分電路BIT分析是基于通過獲得測試點的狀態來識別故障和故障定位。根據信號處理器的特殊性,設計采用為電路各測試點引入激勵信號的方式,實現判斷功能模塊是否存在故障的功能,其BIT方案如圖6所示。

圖6 模擬信號BIT方案

在信號處理器上增加D/A轉換器電路和開關矩陣模塊,FPGA中增加自檢模塊;信號處理器加電時,自檢模塊控制開關矩陣接入各測試點,由D/A轉換器接入特定電壓值;通過比較電路最終測試返回值與引入值即可了解各模塊的狀態。以模擬信號“供電”測試通道為例說明BIT工作流程。(1)自檢模塊預設D/A輸出值為4 V。(2)通過開關矩陣將4 V電壓接入“供電”信號所在調理電路前端。(3)自檢模塊將通過A/D轉換器獲得的數據同預定值進行比較。(4)如果比較結果一致,則輸出“000”表示無故障,自檢結束。(5)如果比較結果不一致,則控制開關矩陣將4 V電壓接入調理電路后端,即交換子前端,自檢模塊將通過A/D轉換器獲得的數據同預定值比較。(6)如果比較結果相一致,則輸出“110”表示調理電路故障,自檢結束。(7)如果比較結果不一致,則控制開關矩陣將4 V電壓接入交換子后端,即A/D轉換器前端,自檢模塊將通過A /D轉換器的獲得的數據同預定值進行比較。(8)如果比較結果相一致,則輸出“101”表示交換子故障,自檢結束。(9)如果比較結果不一致,則通過“100”表示A/D轉換器故障,自檢結束。

此流程存在盲點,即模擬信號處理模塊故障。因為該故障也可能導致交換子輸出和A/D轉換器輸出故障,單一流程無法進行識別和隔離。全部模擬通道均加入到此流程后,就可以通過多數原則判定和隔離上述故障。

[page]

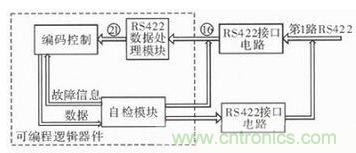

3.3 RS422數據通道BIT設計

RS422數據接收只有兩級功能模塊,故障判定和隔離相對簡單。只需要在FPGA中增加相應數量的標準RS422總線數據流,通過RS422總線接口芯片、開關矩陣和總線選擇器接入RS422總線接口芯片輸入端或RS422數據處理模塊。RS422數據通道BIT方案如圖7所示。

圖7 RS422數據通道BIT方案

信號處理器加電后,自檢模塊首先發出預定格式的RS422信息,并控制開關矩陣切入RS422接口電路的輸入端,將接收到的數據同原始數據進行比對。如果一致則代表無故障;否則,將預定數據通過總線選擇器切入RS422接口電路后端,再將收到的數據與預定數據比較,比對結果數據一致則RS422接口電路存在故障,反之RS422數據處理模塊故障,但不能同時識別RS422接口電路是否故障。3.4 信號處理器整體BIT設計

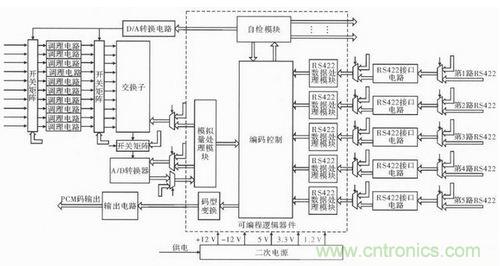

通過對單一模擬信號采集通道以及RS422數據通道的BIT設計實現,最終信號處理器整體BIT設計結果如圖8所示。

圖8 信號處理器完善BIT后的設計框圖

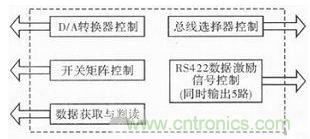

自檢模塊為整個BIT設計的核心,自檢模塊需要控制D/A轉換、開關矩陣的切換、總線選擇器工作狀態、產生需要的激勵信號、完成數據判讀以及生成故障代碼。自檢模塊的功能框圖如圖9所示。

圖9 自檢模塊的功能框圖

相關閱讀:

絕對實用!一種FBAR傳感器信號處理電路的設計

數字信號處理器的POL電源解決方案設計

改進電路設計規程提高可測試性